### UNIVERSIDADE FEDERAL DE PELOTAS

# Centro de Desenvolvimento Tecnológico Programa de Pós-Graduação em Computação

Dissertação

**Exploring Independent Gates in FinFET-Based Transistor Network Generation**

**Vinicius Neves Possani**

| Vinicius N                           | eves Possani                                                                                                                                                                                                             |

|--------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                      |                                                                                                                                                                                                                          |

|                                      |                                                                                                                                                                                                                          |

|                                      |                                                                                                                                                                                                                          |

| Exploring Independent Gates in FinFe | ET-Based Transistor Network Generation                                                                                                                                                                                   |

|                                      |                                                                                                                                                                                                                          |

| G<br>D<br>Fe<br>ob                   | issertação apresentada ao Programa de Pósraduação em Computação do Centro de esenvolvimento Tecnológico da Universidade ederal de Pelotas, como requisito parcial à otenção do título de Mestre em Ciência da omputação. |

|                                      |                                                                                                                                                                                                                          |

| Orientador: Prof. Dr. Leo            | omar Soares da Rosa Junior                                                                                                                                                                                               |

|                                      | Felipe de Souza Marques                                                                                                                                                                                                  |

|                                      |                                                                                                                                                                                                                          |

|                                      |                                                                                                                                                                                                                          |

## Universidade Federal de Pelotas / Sistema de Bibliotecas Catalogação na Publicação

## P856e Possani, Vinicius Neves

Exploring independent gates in finfet-based transistor network generation / Vinicius Neves Possani ; Leomar Soares da Rosa Junior, orientador ; Felipe de Souza Marques, coorientador. — Pelotas, 2015.

80 f.: il.

Dissertação (Mestrado) — Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, 2015.

1. Vlsi design. 2. Tecnologia finfet. 3. Síntese lógica. 4. Ferramentas de CAD. 5. Redes de transistores. I. Rosa Junior, Leomar Soares da, orient. II. Marques, Felipe de Souza, coorient. III. Título.

CDD: 005

#### Vinicius Neves Possani

Exploring Independent Gates in FinFET-Based Transistor Network Generation

Dissertação aprovada, como requisito parcial, para obtenção do grau de Mestre em Ciência da Computação, Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas.

| Banca examinadora:                                                             |

|--------------------------------------------------------------------------------|

|                                                                                |

| Prof. Dr. Leomar Soares da Rosa Junior (Orientador)                            |

| Doutor em Microeletrônica pela Universidade Federal do Rio Grande do Sul       |

| Prof. Dr. Felipe de Souza Marques (Co-orientador)                              |

| Doutor em Ciência da Computação pela Universidade Federal do Rio Grande do Sul |

| Prof. Dr. Bruno Zatt                                                           |

| Doutor em Microeletrônica pela Universidade Federal do Rio Grande do Sul       |

|                                                                                |

| Prof. Dr. Júlio Carlos Balzano de Mattos                                       |

| Doutor em Ciência da Computação pela Universidade Federal do Rio Grande do Sul |

| . After J.                                                                     |

Prof. Dr. Paulo Francisco Butzen

Data da Defesa: 29 de ianeiro de 2015

Doutor em Microeletrônica pela Universidade Federal do Rio Grande do Sul

#### **ACKNOWLEDGEMENTS**

Firstly, I would like to thank my family, especially my mother Mariane Possani and my father Jonas Possani for the love, affection, education and all the support along of my life. I also thank my sister Taise Possani and my brother in law Regis Ceretta for the incentive and especially for give us the Bruno Possani Ceretta, my nephew. Bruno, thank you for all the happiness that you bring for our family and for all the play, shouts and laughter around me, while I wrote this work.

An especial acknowledgement for my girlfriend Bárbara Cavalheiro for all the love, understanding and incentive while I was away for more two years during the master's degree. I also would like to thank her father, mother, and brother Antonio Cavalheiro, Lenir Cavalheiro, and Artur Cavalheiro, respectively.

This work is result of a long time of research under the orientation of the professors Leomar S. da Rosa Junior and Felipe S. Marques, which are my advisor and co-advisor respectively. Thank you for all the conversations, advices and patience during these years of work. Thank you also for the friendship, barbecues and traveling for conferences.

Since the undergraduate in Computer Science until today, I completed six and a half years studying at UFPEL. Thus, I would like to thank all the people who do this university works, especially my professors and colleagues. I am very happy for the opportunity of work as substitute professor at UFPEL in the last year, this was a very nice experience for me. Indeed, I learn a lot during the lessons together with the students.

"But my hand was made Strong

By the hand of the Almighty

We forward in this generation

Triumphantly"

Redemption Song – Bob Marley

#### **RESUMO**

POSSANI, Vinicius Neves. **Explorando Gates Independentes na Geração de Redes de Transistores Baseada em FinFET**. 2015. 80f. Dissertação (Mestrado em Ciência da Computação) — Pós-Graduação em Ciência da Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, Pelotas, 2015.

Inicialmente, este trabalho apresenta uma análise, apontando o impacto da tecnologia FinFET na geração de redes de transistores durante a etapa de síntese lógica. Essa análise apresenta diversos estudos de casos para demonstrar que uma mudança de paradigma vem sendo introduzida pelos dispositivos double-gate, como os transistores independent-gate (IG) FinFET. Além disso, o presente trabalho mostra que essa mudança de paradigma deixa uma lacuna a ser explorada, tendo em vista que os métodos de geração de redes de transistores disponíveis na literatura não são capazes de explorar o potencial que os dispositivos double-gate oferecem. Então, neste trabalho são propostos dois métodos alternativos para geração de redes de transistors baseadas em dispositivos IG FinFET. Um dos métodos é baseado em grafos e visa encontrar padrões de arranjos promissores para explorar o potencial dos dispositivos double-gate. O segundo método proposto visa realizar defatorações em expressões Booleanas a fim de maximizar o uso dos gates independentes de cada transistor IG FinFET. Os experimentos realizados demonstram que os métodos propostos são capazes de gerar redes de transistors IG FinFET otimizadas, com um baixo custo em tempo de execução. Além disso, os resultados obtidos demonstram que de fato os métodos convencionais de geração de redes de transistors não são a melhor alternativa para gerar redes baseadas em dispositivos double-gate. Com isso, os resultados reforçam a existência de um novo paradigma introduzido pela tecnologia IG FinFET. Enfim, a análise apresentada neste trabalho dá suporte para o desenvolvimento de novas técnicas de geração de redes de transistors IG FinFET.

**Palavras-chave:** VLSI design; tecnologia FinFET; síntese lógica; EDA; ferramentas de CAD; redes de transistores; portas lógicas; fatoração; teoria de grafos.

#### **ABSTRACT**

POSSANI, Vinicius Neves. **Exploring Independent Gates in FinFET-Based Transistor Network Generation**. 2015. 80f. Dissertation (Master Degree in Computer Science) – Pós-Graduação em Ciência da Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, Pelotas, 2015.

Firstly, this work presents an analysis pointing the impacts of the FinFET technology in the transistor network generation during the logic synthesis step. This analysis presents some case studies demonstrating that a new paradigm has been introduced by the double-gate devices, like the independent-gate (IG) FinFETs. Moreover, this work demonstrates that this new paradigm introduces a lack to be explored. Since the conventional methods for transistor network generation are not able to explore the potential provided by double-gate devices. Thus, this work proposes two alternative methods for IG FinFET-based transistor network generation. The first one is a graph-based method, which aims to find promising patterns to explore the potential provided by the double-gate devices. The second one aims to defactoring Boolean expression in order to maximize the use of the independent gates of each IG FinFET. The experiments have demonstrated that the proposed methods are able to generate optimized IG FinFET transistor networks, with a low cost in run time. Moreover, the obtained results demonstrate that, in fact, the conventional methods of transistor network generation are not the best alternative to design networks based in double-gate devices. This way, the results reinforce the existence of a new paradigm introduced by the IG FinFET technology. Finally, the analysis presented in this work provides support to design new methods to build transistor networks based in IG FinFETs.

**Key-words:** VLSI design; FinFET technology; logic synthesis; EDA; CAD tools; transistor network; logic gates; factorization; graph theory.

## **LIST OF FIGURES**

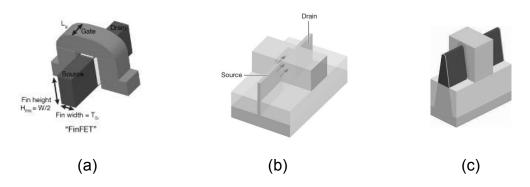

| Figure 1 -  | In (a), SG FinFET transistor and in (b) IG FinFET transistor15                   |

|-------------|----------------------------------------------------------------------------------|

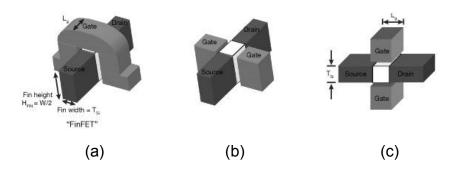

| Figure 2 -  | Three different implementations of the Single-Gate (SG) FinFET                   |

|             | transistor. Images source: (a) (SYNOPSYS, 2012), (b) (MARKOV, 2014)              |

|             | and (c) Intel (GSS, 2012)21                                                      |

| Figure 3 -  | Usual Single-Gate (SG) FinFET configuration in (a) and Independet-Gate           |

|             | (IG) FinFET configuration in (b) and (c). Images source: (SYNOPSYS               |

|             | 2012)22                                                                          |

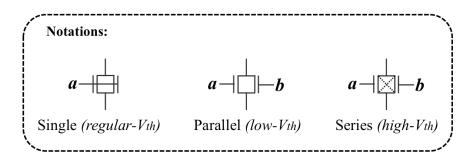

| Figure 4 -  | Different FinFET representations: in SG FinFET, IG FinFET paralle                |

|             | (low-Vth) and IG FinFET series (high-Vth)24                                      |

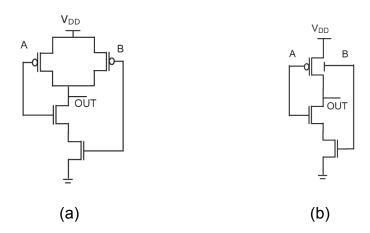

| Figure 5 -  | Conventional implementation for 2-input NAND (a) and optimized                   |

|             | solution obtained by merging parallel transistors in an IG FinFET                |

|             | regular-V <sub>T</sub> (parallel) (b), proposed in (CHIANG, KIM, et al., 2005)25 |

| Figure 6 -  | Conventional implementation for 2-input NAND (a) and optimized                   |

|             | solution obtained by merging series and parallel transistors in IG               |

|             | FinFETs, proposed in (CHIANG, KIM, et al., 2006)26                               |

| Figure 7 -  | New implementation for the 6-input NAND gate using only six IG FinFET            |

|             | transistors, proposed in (CHIANG, KIM, et al., 2006)27                           |

| Figure 8 -  | Representation of different kinds of FinFETs proposed in (ROSTAMI e              |

|             | MOHANRAM, 2011)29                                                                |

| Figure 9 -  | Defactorizations proposed in (ROSTAMI e MOHANRAM, 2011)30                        |

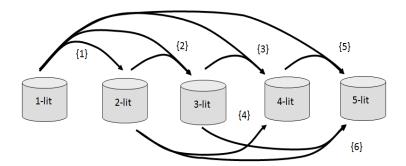

| Figure 10 - | Generation of sub-functions until the 5th bucket, proposed in (MARTINS           |

|             | DA ROSA JUNIOR, et al., 2010). The number inside braces indicates                |

|             | the bucket composition step order33                                              |

| Figure 11 - | Example of network composition proposed in (KAGARIS e HANIOTAKIS                 |

|             | 2007)34                                                                          |

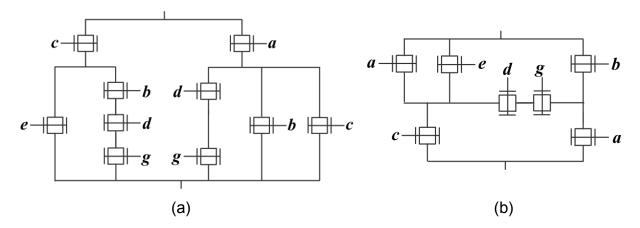

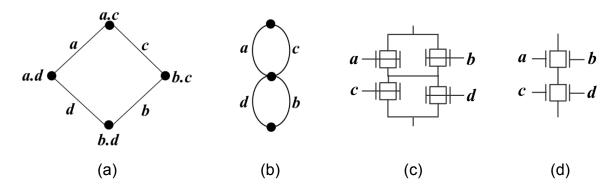

| Figure 12 - | Kernel structures: (a) NSP and (b) SP proposed in (POSSANI,                              |

|-------------|------------------------------------------------------------------------------------------|

|             | CALLEGARO, et al., 2013)35                                                               |

| Figure 13 - | SP and NSP kernels in (a) and (c), respectively, and correspondent                       |

|             | networks in (b) and (d). Final solution (e) obtained by compose networks                 |

|             | (b) and (d)37                                                                            |

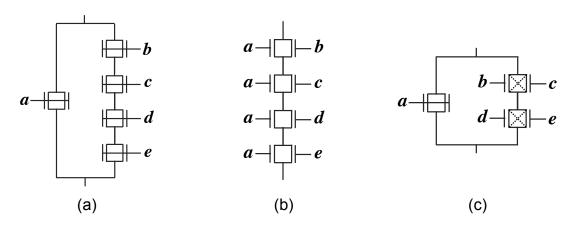

| Figure 14 - | In (a), transistor network obtained from Equation (2) and in (b), the                    |

|             | optimized network obtained from Equation (3)40                                           |

| Figure 15 - | In (a), network obtained from Equation (4) and in (b), optimized network                 |

|             | obtained from Equation (5)41                                                             |

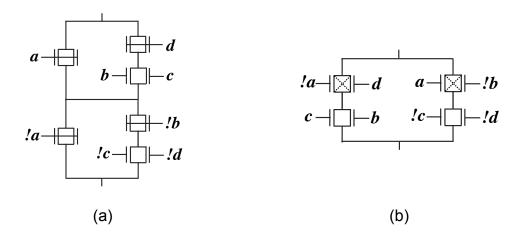

| Figure 16 - | Two possible solutions to implement the logic function $f$ using SG                      |

|             | FinFETs: in (a) SP network and in (b) NSP network42                                      |

| Figure 17 - | Two possible solutions to implement the logic function $f$ using IG                      |

|             | FinFETs: in (a) SP network and in (b) NSP network43                                      |

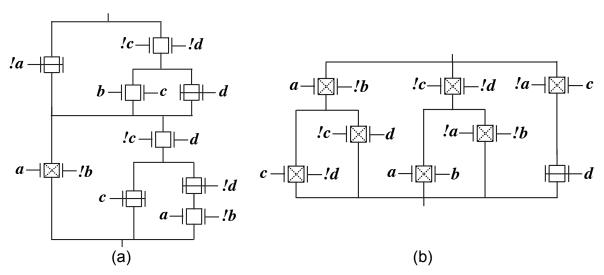

| Figure 18 - | Two possible solutions to implement the logic function $f$ using SG                      |

|             | FinFETs: in (a) SP network and in (b) NSP network43                                      |

| Figure 19 - | Two possible solutions to implement the logic function $f$ using $\operatorname{IG}$     |

|             | FinFETs: in (a) SP network and in (b) NSP44                                              |

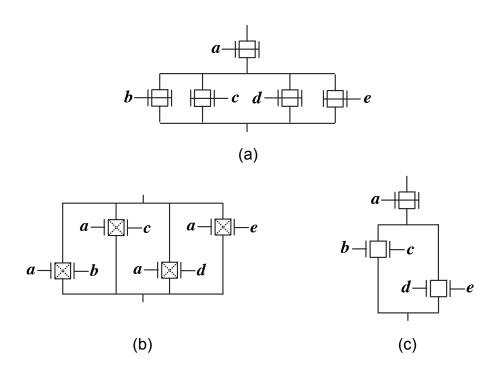

| Figure 20 - | In (a) SG FinFET implementation and in (b) IG FinFET implementation,                     |

|             | both obtained from the factored form of Equation (12). In (c) IG FinFET                  |

|             | implementation obtained by replicating the literal $\boldsymbol{a}$ in the factored form |

|             | of Equation (12)46                                                                       |

| Figure 21 - | SP kernel template (a), auxiliary template graph (b) and resulting SG                    |

|             | FinFET network (c)49                                                                     |

| Figure 22 - | SP kernel (a) derived from Equation (14), auxiliary graph template (b),                  |

|             | SG FinFET network (c) and IG FinFET network obtained after applying                      |

|             | the edge reordering routine50                                                            |

| Figure 23 - | Table obtained from Equation (15) that represents cubes relationship to                  |

|             | determine wanted groups that share at least two literals51                               |

| Figure 24 - | Network delivered by the proposed method obtained from Equation (15).                    |

|             | 51                                                                                       |

| Figure 25 - | Network delivered by conventional methods obtained from Equation                         |

|             | (15)52                                                                                   |

| Figure 26 - | Partial arrangements found form Equation (16) during the two first steps |

|-------------|--------------------------------------------------------------------------|

|             | in (a), (b), and (c). Final solution achieved after to remove redundant  |

|             | transistors among the parallel branches in (d)53                         |

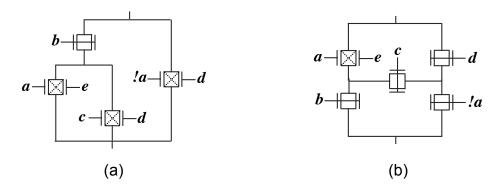

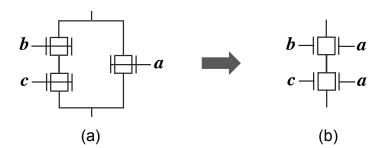

| Figure 27 - | First defactorization proposed in (ROSTAMI e MOHANRAM, 2011):            |

|             | conventional arrangement in (a) and defactored arrangement saving one    |

|             | transistor in (b)54                                                      |

| Figure 28 - | Conventional arrangement in (a), network obtained by defactoring         |

|             | according (ROSTAMI e MOHANRAM, 2011) in (b), and the proposed            |

|             | merging in (c)55                                                         |

| Figure 29 - | Second defactorization proposed in (ROSTAMI e MOHANRAM, 2011):           |

|             | conventional arrangement in (a) and defactored arrangement saving one    |

|             | transistor in (b)56                                                      |

| Figure 30 - | Conventional arrangement in (a), network obtained by defactoring         |

|             | according (ROSTAMI e MOHANRAM, 2011) in (b), and the proposed            |

|             | merging in (c)56                                                         |

| Figure 31 - | Two adopted patterns to perform series defactorizations57                |

| Figure 32 - | Promising arrangement to be defactorized, by replicating the transistor  |

|             | controlled by the literal a58                                            |

| Figure 33 - | Logic tree derived from Equation (16) in (a), tree obtained by merging   |

|             | nodes in (b), and resultant tree after performing the defactorization of |

|             | literal a in (c)60                                                       |

| Figure 34 - | Optimized transistor network obtained by defactoring the factored form   |

|             | described in Equation (16)60                                             |

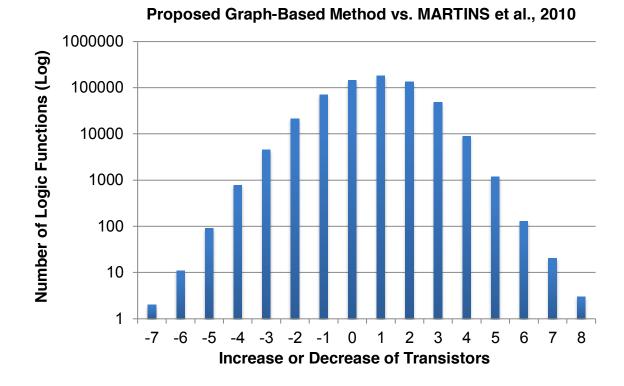

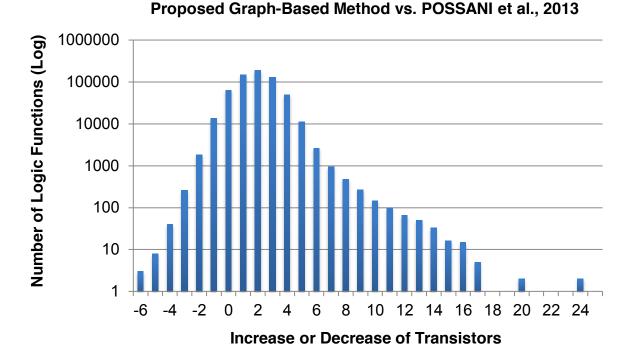

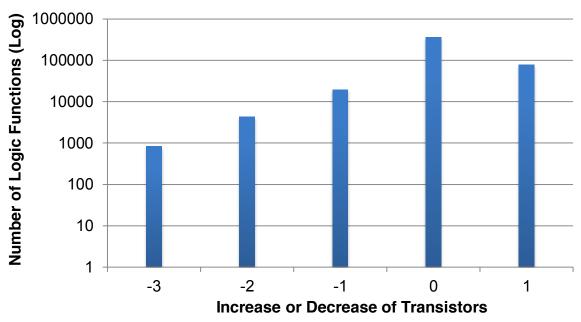

| Figure 35 - | Transistors increase or decrease obtained by the proposed method when    |

|             | compared to (MARTINS, DA ROSA JUNIOR, et al., 2010), for the set of      |

|             | 5-input NPN-class functions63                                            |

| Figure 36 - | Transistors increase or decrease obtained by the proposed method when    |

|             | compared to (POSSANI, CALLEGARO, et al., 2013), for the set of 5-        |

|             | input NPN-class functions64                                              |

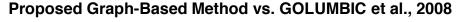

| Figure 37 - | Transistors increase or decrease obtained by the proposed method when    |

|             | compared to (GOLUMBIC, MINTZ e ROTICS, 2008), for the set of 6-          |

|             | input Read-Once functions65                                              |

## **LIST OF TABLES**

| Table 1 - | Total number of transistors for the set of 5-inputs NPN-class Boolean     |

|-----------|---------------------------------------------------------------------------|

|           | functions62                                                               |

| Table 2 - | Total number of transistors for the set of 6-inputs read-once functions65 |

| Table 3 - | Results for decomposition of circuits into K-cuts, with k=4, k=6 and K=8  |

|           | 67                                                                        |

| Table 4 - | Improvement obtained by the proposed defactorization method over the      |

|           | results provided by method (MARTINS, DA ROSA JUNIOR, et al., 2010)        |

|           | considering the set of Boolean functions (1)69                            |

| Table 5 - | Improvement obtained by the proposed defactorization method over the      |

|           | results provided by method (MARTINS, DA ROSA JUNIOR, et al., 2010)        |

|           | considering the set of Boolean functions (2)69                            |

| Table 6 - | Improvement obtained by the proposed defactorization method over the      |

|           | results provided by method (CALLEGARO, MARTINS, et al., 2013              |

|           | considering the set of Boolean functions (3)69                            |

| Table 7 - | Improvement obtained by the proposed defactorization method over the      |

|           | results provided by method (GOLUMBIC, MINTZ e ROTICS, 2008)               |

|           | considering the set of Boolean functions (4)70                            |

| Table 8 - | Comparative analysis between the proposed methods71                       |

#### LIST OF ABBREVIATIONS AND ACRONYMS

BDD Binary Decision Diagram

CAD Computer Aided Design

CMOS Complementary Metal-Oxide-Semiconductor

DARPA Defense Advanced Research Projects Agency

DG Double-Gate

EDA Electronic Design Automation

FC Functional Composition

FinFET Field-Effect Transistor

IC Integrated Circuit

IG FinFET Independent-Gate FinFET

ISOP Irredundant-Sum-Of-Products

ITRS International Technology Roadmap for Semiconductors

NSP Non-Series-Parallel

NSP Kernel Non-Series-Parallel Kernel

RO Read-Once

RPO Read-Polarity-Once

SG FinFET Single-Gate FinFET

SP Series-Parallel

SP Kernel Series-Parallel Kernel

SOP Sum-Of-Products

UTB-SOI Ultra Thin Body Silicon Over Insulator

VLSI Very-Large-Scale Integration

## **SUMMARY**

| 1 IN  | NTRODUCTION                                                              | 15   |

|-------|--------------------------------------------------------------------------|------|

| 1.1   | Motivation                                                               | 16   |

| 1.2   | Objectives                                                               | 18   |

| 1.3   | Organization of this Work                                                | 19   |

| 2 B   | BACKGROUND                                                               | 20   |

| 2.1   | The FinFET Transistor                                                    | 20   |

| 2.2   | Innovations and Applications of the FinFET Transistors                   | 24   |

| 2.2.1 | CHIANG et al. (CHIANG, KIM, et al., 2005) e (CHIANG, KIM, et al., 2006). | . 24 |

| 2.2.2 | Patta et al. (DATTA, GOEL, et al., 2007)                                 | . 27 |

| 2.2.3 | 8 Wang (WANG, 2010)                                                      | . 28 |

| 2.2.4 | Rostami et al. (ROSTAMI e MOHANRAM, 2011)                                | . 29 |

| 2.3   | The State of the Art on Transistor Network Generation                    | 31   |

| 2.3.1 | Mintz et al. (MINTZ e GOLUMBIC, 2005)                                    | . 32 |

| 2.3.2 | Martins et al. (MARTINS, DA ROSA JUNIOR, et al., 2010)                   | . 33 |

| 2.3.3 | Kagaris et al. (KAGARIS e HANIOTAKIS, 2007)                              | . 34 |

| 2.3.4 | Possani et al. (POSSANI, CALLEGARO, et al., 2013)                        | . 35 |

| 3 IN  | NVESTIGATING AND IDENTIFYING THE NEW CHALLENGES ESTABLISI                | ΗED  |

|       | BY INDEPENDENT-GATE FINFET TRANSISTORS                                   | 39   |

| 4 P   | ROPOSED METHODS FOR INDEPENDENT-GATE FINFET TRANSIST                     | ГОБ  |

|       | NETWORK DESIGN                                                           | 47   |

| 4.1   | Generating Transistor Networks by Graph-Based Optimizations              | 47   |

| 4.1.1 | Series-Parallel Kernel Finder                                            | . 48 |

| 4.1.2 | 2 IG FinFET Dedicated Factorization                                      | . 50 |

| 4.1.3 | Network Composition                                               | 52  |

|-------|-------------------------------------------------------------------|-----|

| 4.2   | Generating Transistor Networks by Defactoring Boolean Expressions | .54 |

| 4.2.1 | First Observation on Defactorization                              | 54  |

| 4.2.2 | Second Observation on Defactorization                             | 55  |

| 4.2.3 | Third Observation on Defactorization                              | 57  |

| 4.2.4 | Integrating the Three Observations in a Single Method             | 58  |

|       |                                                                   |     |

| 5 EX  | KPERIMENTAL RESULTS                                               | .61 |

| 5.1.1 | Results for the Graph-based Approach                              | 62  |

| 5.1.2 | Results for the Defactorization Approach                          | 68  |

| 5.1.3 | Comparing the Proposed Approaches                                 | 71  |

|       |                                                                   |     |

| 6 C   | ONCLUSIONS AND FUTURE WORKS                                       | .73 |

|       |                                                                   |     |

| REFE  | RENCES                                                            | .75 |

|       |                                                                   |     |

| APPE  | NDIX A - Publications                                             | .79 |

#### 1 INTRODUCTION

Although the continuous CMOS transistor scaling has been providing performance improvements of digital circuits, its technology process faces great challenges due to the devices shrinking and the fundamental materials limits (FRANK, DENNARD, *et al.*, 2001). Since 2001, the International Technology Roadmap for Semiconductors (ITRS) has pointed the FinFET (HUANG, LEE, *et al.*, 1999) and the UTB-SOI (CHOI, JEON, *et al.*, 2000) as promising technologies for transistor scaling beyond CMOS limits. In the last years, different solutions of doublegate (DG) devices were proposed (CHANG, CHOI, *et al.*, 2003) (NOWAK, ALLER, *et al.*, 2004) (ROY, MAHMOODI, *et al.*, 2005).

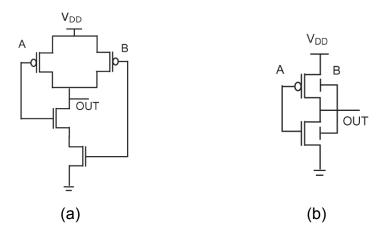

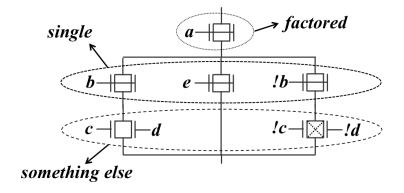

In this work we have a special interest for DG FinFET devices, which can be designed in two different ways according to the gate configuration. One possibility is to binding the two gates yielding a single-gate (SG) FinFET, as illustrated in Fig. 1(a). This configuration is also known as shorted-gate FinFET. The other one is to build an independent-gate (IG) FinFET, in such a way that each gate can be controlled by a different input signal, as illustrated in Fig. 1(b). These different configurations have allowed a rich project space and introduced new challenges to be explored both in logic and physical synthesis.

Figure 1 - In (a), SG FinFET transistor and in (b) IG FinFET transistor.

Based on the IG FinFET structure shown in Fig. 1(b), some researchers have observed the possibility of exploring the separated gates to merge two transistors associated in parallel, *i. e.*, (a + b), in a single IG FinFET (CHIANG, KIM, *et al.*, 2005) (DATTA, GOEL, *et al.*, 2007) (MUTTREJA, AGARWAL e JHA, 2007). In this case, the threshold voltage must be low enough to turn on the transistor ( $l_{on}$ ) when at least one gate is active. This kind of transistor is called IG FinFET *low-Vth* (*parallel*).

Furthermore, some authors introduced the possibility of merging two transistors associated in series, *i. e.,* (*a . b*), in an IG FinFET. It is also done based on the threshold voltage, which must be high enough to turn on the transistor (*Ion*) if and only if both gates are active (CHIANG, KIM, *et al.*, 2006) (WANG, 2010) (ROSTAMI e MOHANRAM, 2011). Otherwise, the current is low enough to keep the transistor in the off state (*Ioff*). This kind of transistor is called IG FinFET *high-Vth* (*series*).

It becomes possible to design transistor networks by using only conventional single-gate SG FinFETs or combining both SG FinFETs and IG FinFETs (*series* and *parallel*). These three variations of FinFETs have enhanced the project space during the synthesis of transistor networks. This way, the merging of series and parallel transistors in IG FinFETs becomes a powerful strategy to decrease the transistor count in logic gates (CHIANG, KIM, *et al.*, 2005) (DATTA, GOEL, *et al.*, 2007) (MUTTREJA, AGARWAL e JHA, 2007) (CHIANG, KIM, *et al.*, 2006) (WANG, 2010) (ROSTAMI e MOHANRAM, 2011).

#### 1.1 Motivation

Considering the new possibilities provided by the IG FinFET devices, several works available in the literature are concerned to use such possibilities to design basic gates and other few different Boolean functions. Recently, some works have presented novel solutions to implement elementary gates as AND, NAND, OR, and NOR, by merging series and parallel transistors in IG FinFETs (CHIANG, KIM, *et al.*, 2005) (DATTA, GOEL, *et al.*, 2007) (MUTTREJA, AGARWAL e JHA, 2007) (CHIANG, KIM, *et al.*, 2006) (ROSTAMI e MOHANRAM, 2011). Some of these authors have also synthesized benchmark circuits using such novel gates as cell library. Their experiments have demonstrated that decreasing the transistor count through IG FinFETs is an efficient way to reduce area and power in digital design (MUTTREJA, AGARWAL e JHA, 2007) (ROSTAMI e MOHANRAM, 2011).

In the literature there are many different methods to decrease the transistor count and to help the development of optimized logic gates (SENTOVICH, 1992) (MARTINS, DA ROSA JUNIOR, *et al.*, 2010) (GOLUMBIC, MINTZ e ROTICS, 2008) (CALLEGARO, MARTINS, *et al.*, 2013) (KAGARIS e HANIOTAKIS, 2007) (POSSANI, CALLEGARO, *et al.*, 2013). Such methods are able to deliver satisfactory solutions for single-gate devices, *i. e., conventional CMOS or SG FinFET*.

In general, these methods aim to minimize the number of literals in a Boolean expression by applying Boolean and algebraic factorization (SENTOVICH, 1992) (MARTINS, DA ROSA JUNIOR, *et al.*, 2010), graph-based factorizations (GOLUMBIC, MINTZ e ROTICS, 2008) (CALLEGARO, MARTINS, *et al.*, 2013), and also more flexible graph-based optimizations (KAGARIS e HANIOTAKIS, 2007) (POSSANI, CALLEGARO, *et al.*, 2013). Traditionally, minimize the number of literals leads to a reduced transistor network. It occurs because there is a direct relation between literals and transistors. In other words, each literal in a factored expression can be directly mapped to a transistor in a network. This relation also happens when the literals represented by edges in a graph-based solution are mapped to transistors in a network.

However, a new paradigm has been introduced by merging series and parallel transistors in IG FinFETs, as mentioned before. It impacts in how to generate efficient transistor arrangements during the logic synthesis. Thus, when the goal is to decrease the transistor count by using IG FinFETs, just to minimize the number of literals in a given Boolean expression may not drive to the best solution. We have observed two main reasons for that:

- (1) Just consider the literal count as metric during the optimization process is not enough, we also need to adopt structural characteristics as criterion;

- (2) Some redundant literals, in a factored expression or in a graph-based solution, can contribute to find the best merging of series and parallel transistors in IG FinFETs.

In order to achieve efficient transistor arrangements, these two factors must be considered during the transistor network generation. Therefore, as both the conventional factorization methods and the graph-based techniques aim to decrease the maximum number of literals, these methods (SENTOVICH, 1992) (MARTINS, DA ROSA JUNIOR, *et al.*, 2010) (GOLUMBIC, MINTZ e ROTICS, 2008) (CALLEGARO,

MARTINS, et al., 2013) (KAGARIS e HANIOTAKIS, 2007) (POSSANI, CALLEGARO, et al., 2013) may not be the best alternative to generate IG FinFET transistor networks.

Considering that the merging of series and parallel transistors in IG FinFET devices has become an alternative way to reduce area and power dissipation in VLSI design (ROSTAMI e MOHANRAM, 2011), it is important to determine an automated method to find efficient IG FinFET transistor networks. We have observed that the corelated works (CHIANG, KIM, *et al.*, 2005) (DATTA, GOEL, *et al.*, 2007) (MUTTREJA, AGARWAL e JHA, 2007) (CHIANG, KIM, *et al.*, 2006) (WANG, 2010) (ROSTAMI e MOHANRAM, 2011) are concerned to demonstrate that the new possibilities provided by the IG FinFET devices are feasible for a real design.

In general, such works have investigated materials, electrical effects and geometric characteristics in order to solve problems for the physical synthesis step. Indeed, no one of them presents an automated method to find efficient transistor networks for IG FinFETs, during the logic synthesis step. Thus, the main motivation of this work consists in exploring the lack introduced by the IG FinFET technology in the logic synthesis level.

## 1.2 Objectives

The first objective of this work is to present a detailed analysis discussing that there is a new paradigm being introduced by the double-gate FinFET devices, during the transistor networks generation. This analysis will be performed through a set of case studies, demonstrating that the conventional methods of transistor networks generation may not be useful for an IG FinFET-based design. Thus, after characterizing the problem, the second objective of this work is to propose two alternative methods able to explore the potential of the IG FinFETs during the synthesis of transistor networks. One method tries to explore the double-gate devices by finding promising patterns that allow series and parallel merging of transistors in IG FinFETs. The other one is a defactorization method, which receives a factored expression as input and replicates some literals of the expression, in order to enable series and parallel merging in IG FinFETs. We also aim to reinforce the existence of a new paradigm by comparing the results of the proposed methods with the results provided by conventional ones.

As this is one of the first works that investigate the impact of double-gate FinFETs in the logic synthesis level, our overall objective is to provide support for further investigations related to double-gate devices in such level. In this sense, the main contributions of this work are:

- ✓ A set of case studies discussing the new paradigm to implement Boolean functions using IG FinFETs.

- ✓ A graph-based method for automatic generation of optimized IG FinFET transistor networks.

- ✓ An alternative method for defactoring Boolean expressions and improve the factored forms, generated by conventional methods, for an IG FinFET-based design.

#### 1.3 Organization of this Work

The remaining of this work is organized as follows. The Chapter 2 presents a brief review of all material that provided support to design this work. Thus, the Chapter 2 presents the origin and the characteristics of the FinFET transistor and also presents the main related works regarding FinFET technology and transistor network generation. The Chapter 3 presents the case studies that pointing for a new paradigm involving Boolean algebra, switch theory and the double-gate devices. In the sequence, the Chapter 4 presents the proposed graph-based method and the proposed defactorization method for IG FinFET transistor network design. The experiments performed in this work and the obtained results are presented in the Chapter 5. Finally, the Chapter 6 presents our conclusions, and also points some future works.

#### 2 BACKGROUND

This chapter presents a brief review of related works, which were used as basis to develop this work. The section 2.1 presents some basic characteristics of FinFET transistors in order to provide a better understanding of this work. In the sequence, some papers that propose new approaches based on IG FinFETs are briefly discussed in the section 2.2. Finally, the most recent works related to transistor networks generation are discussed in the section 2.3. These three sections give us support to understand what are the new possibilities provided by the FinFET devices and how the most recent transistor network generation methods work.

#### 2.1 The FinFET Transistor

The FinFET transistor arises in the end of 90's years, when the *Defense Advanced Research Projects Agency* (DARPA) annunciates a demand for sub 25nm technologies. In such days, the microelectronics industry was designing chips with technology of 250nm. Thus, Chenming Hu, professor and researcher from University of California, Berkeley, proposes a promising transistor structure feasible for sub 25nm design. In 1997 Chenming Hu and their research group receive support from DARPA to design and demonstrate the FinFET transistor (HUANG, LEE, *et al.*, 1999) (SPECTRUM, 2011).

Nowadays, it is possible to say that there is a race among the foundries to find the most accurate structure to implement FinFET transistors. Fig. 2 presents three different implementations of the FinFET transistor, among others. Although there are different ways to implement a FinFET, the main characteristics of this new device is the 3D construction of the *gate*, *source*, and *drain*, as we can see in all versions presented in Fig 2.

Figure 2 - Three different implementations of the Single-Gate (SG) FinFET transistor. Images source: (a) (SYNOPSYS, 2012), (b) (MARKOV, 2014), and (c) Intel (GSS, 2012).

As we can see in Fig. 2, the channel of the FinFET transistor is rounded by the gate in such a way that there is a contact of three faces of the channel with three sides of the gate. According to the experts, this approach provides greater control of the transistor channel, bringing the following characteristics:

- ✓ The gate has more control over the current flow in the transistor channel;

- ✓ The voltage in silicon substrate cannot impact in the current when the transistor is in the *I<sub>off</sub>* state. In other words, the FinFET has lower static power dissipation;

- ✓ Due to the large inversion area of the transistor, the current flow is high when the transistor is in the *l<sub>on</sub>* state:

- ✓ The FinFET structure does not impact in the density of transistors into the chip;

- ✓ The number of fins can vary according to the demand for performance.

The first two characteristics presented in the list above are related to low leakage. The last three characteristics are interesting because they allow greater performance with low energy consumption. Another issue that contributes for the integrated circuits (IC) design based on FinFET devices is the great similarity of such technology with the conventional planar CMOS fabrication process (HUANG, LEE, *et al.*, 1999).

As briefly presented in the introduction of this work, a FinFET transistor can be designed of different ways according the gate configuration. The Fig. 2 presents three different implementations for the usual configuration of the gate for a FinFET transistor. Notice that, in the usual configuration there is a single gate around the channel of the transistor. However, by removing the top of the gate, it is possible to produce two independent gates, as shown in Fig. 3(b) and Fig. 3(c) (LIU, MATSUKAWA, *et al.*, 2007). These different configurations can be explored according to the design constraints and the objectives of the project (WANG, 2010) (ROSTAMI e MOHANRAM, 2011) (MISHRA, MUTTREJA e JHA, 2011) (CAKICI, MAHMOODI, *et al.*, 2005).

Figure 3 - Usual Single-Gate (SG) FinFET configuration in (a) and Independet-Gate (IG) FinFET configuration in (b) and (c). Images source: (SYNOPSYS, 2012).

Among the applications to explore the separated gates of an IG FinFET, the most common are:

- ✓ Decrease the transistor count by merging series and parallel transistors in IG FinFETs (CHIANG, KIM, *et al.*, 2006) (DATTA, GOEL, *et al.*, 2007) (MUTTREJA, AGARWAL e JHA, 2007) (ROSTAMI e MOHANRAM, 2011);

- ✓ Decrease the logic gate capacitances and power dissipation by disable one of the independent gates in each transistor (DATTA, GOEL, et al., 2007) (MUTTREJA, AGARWAL e JHA, 2007) (ROSTAMI e MOHANRAM, 2011);

✓ Design optimized memory cells by exploring the independent gates (LIU, TAWFIK e KURSUN, 2008) (TAWFIK e KURSUN, 2008) (AMAT, ALMUDEVER, et al., 2013).

Although the merging of pairs of transistors in IG FInFETs come with a slight deterioration in gate delay, it is shown that reducing the number of stacked devices by series merging is a good strategy to mitigate the loss in performance. Another point is that the merging of series and parallel transistors tends to increase the complexity and the wire length to perform intra-cell routing. However, this extra cost for routing the independent gates may be covered by the area reduction obtained by merging pairs of transistors in IG FinFETs.

Indeed, the FinFET technology brings a renewal for the microelectronics industry, allowing that the Moore's law remains in the next decades (MOORE, 1965). In the last two years the main companies of the microelectronics field have started to design ICs based on FinFETs. However, as mentioned before, there are some new possibilities to explore the separated gates of each IG FinFET, resulting in more challenges during the design.

The advances of the FinFET technology also bring challenges to the *Electronic Design Automation* (EDA) and *Computer-Aided Design* (CAD) tools. At the same time that the foundries have gradually adapted the fabrication flow to produce FinFET-base chips, the EDA industry also needs to adapt and design new feature to ensure that the tools are able to represent and model the complexities imposed by the FinFET technology (SYNOPSYS, 2012). In general, the main problems related to the FinFET design are in the physical synthesis step and in the fabrication process.

Although the impact of the FinFETs in the logic synthesis is small, such impact exists and demands for an efficient solution. As the IC design flow is composed of several steps, and the quality of the early steps can impact the following ones, it is important to perform optimizations in all phases of the project to attend the design constraints. Thus, in this work we will expose and propose alternative solutions for problems tied to the logic synthesis, more specifically during the transistor network generation. The problems and challenges tied to the physical synthesis are beyond the scope of this works.

In the remaining of this work the SG FinFET, the IG FinFET (parallel) and the IG FinFET (series) are represented according the notations illustrated in Fig. 4, respectively.

Figure 4 - Different FinFET representations: in SG FinFET, IG FinFET parallel (*low-Vth*) and IG FinFET series (*high-Vth*).

## 2.2 Innovations and Applications of the FinFET Transistors

This section presents some works that propose new approaches to implement logic gates exploring the IG FinFET transistors. In general, such works have demonstrated, through electrical simulations, the feasibility of using separated gates for different goals during the transistor network generation. These authors have presented results showing that the IG FinFETs allow the implementation of optimized logic gates, pointing reductions in different aspects as area, power dissipation, input capacitance and delay.

### 2.2.1 CHIANG et al. (CHIANG, KIM, et al., 2005) e (CHIANG, KIM, et al., 2006)

In 2005, Chiang et al. presented an IG FinFET-based implementation for the 2-input NAND and the 2-input NOR logic gates (CHIANG, KIM, *et al.*, 2005). For instance, as we can see in Fig. 5(a), a conventional implementation of the 2-input NAND has a parallel association of transistors in the *pull-up* plane. Thus, as an IG FinFET has two independent gates, the authors observed the possibility of merging two different input signals associated in parallel in a single IG FinFET, resulting in the networks illustrated in Fig. 5(b). The authors called this kind of transistor as IG FinFET *regular-V<sub>T</sub>* (*parallel*), since the parallel merging does not require changes in the threshold of the transistor. Thus, it means that the transistor will propagate the signal when at least one of the gates is active. Similarly to NAND, the optimized NOR gate is obtained by merging the parallel transistor of the *pull-down* plane.

Figure 5 - Conventional implementation for 2-input NAND (a) and optimized solution obtained by merging parallel transistors in an IG FinFET  $regular-V_T$  (parallel) (b), proposed in (CHIANG, KIM, et~al., 2005).

When comparing the optimized NAND gate illustrated in Fig. 5(b) with the conventional implementation it is possible to achieve 40% and 33% of reduction in static and dynamic power, respectively. Moreover, the authors report an improvement of 10% in performance for the optimized NAND gate. Another interesting issue is that the merging of transistors in IG FinFETs brings reductions in the input capacitances, resulting in a reduction of the total capacitance of the logic gate. For the proposed NOR gate, the authors report a reduction of 20% and 17% in the static and dynamic power, respectively. However, the performance is 2% worst than the conventional NOR gate. Although there is a small increasing in the gate delay, the proposed NOR implementation still being competitive by presenting significant reductions in area, power, and capacitance.

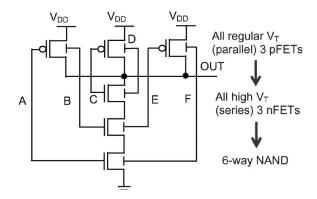

Afterwards, in 2006, Chiang et al. presented a new approach that allows the merging of two series transistors in a single IG FinFETs (CHIANG, KIM, *et al.*, 2006). The series merging is feasible by increasing the threshold of the transistors, resulting in a new king of device called IG FinFET *high-V<sub>T</sub>* (*series*). Thus, this king of transistor will propagate the signal if and only if both gates are active. The possibility of merging series and parallel transistors in IG FinFETs contributes significantly to decrease the number of devices needed to implement a logic gate. In this sense, it is possible to improve the gains previously presented in (CHIANG, KIM, *et al.*, 2005).

The authors propose a new implementation for the 2-input NAND gate, which can be designed using only two transistors, one N-FinFET  $high-V_T$  (series) and one

P-FinFET *regular-V* $_{T}$  (parallel), as illustrated in Fig. 6(b). This new implementation has 2 times less area and capacitance than the conventional implementation, with an improvement of 19% in performance. The 2-input NOR also can be implemented using only two IG FinFETS.

Another interesting point demonstrated in (CHIANG, KIM, *et al.*, 2006) is that the proposed approaches for series and parallel merging of transistors allow the implementation of logic gates with larger number of inputs than the conventional CMOS implementation. Nowadays, the number o transistor associated in series is limited in order to achieve a practical performance. Thus, a conventional 6-input NAND implementation is not practical for the CMOS technology with a satisfactory performance. It is due to the six transistors associated in series in the *pull-down* plane of the 6-input NAND gate. However, by merging series and parallel transistors in IG FinFETs it is possible to reduce the transistor stack and achieve a practical implementation for the 6-input NAND gate, as illustrated in Fig. 7 (CHIANG, KIM, *et al.*, 2006).

Figure 6 - Conventional implementation for 2-input NAND (a) and optimized solution obtained by merging series and parallel transistors in IG FinFETs, proposed in (CHIANG, KIM, *et al.*, 2006).

Figure 7 - New implementation for the 6-input NAND gate using only six IG FinFET transistors, proposed in (CHIANG, KIM, *et al.*, 2006).

## 2.2.2 Datta et al. (DATTA, GOEL, et al., 2007)

The authors present different low power implementations for basic logic gates like 2-input NAND, 2-input NOR and INVERTER, where the independent gates of each IG FinFET are explored with different purposes (DATTA, GOEL, et al., 2007). Some of these implementations use one gate as input and the other one is disabled (connected to the ground or supply rail), to reduce the switching capacitances. Other implementations use the independent gates for merging parallel transistors and decrease the transistor count, as early proposed in (CHIANG, KIM, et al., 2005). However, the authors do not mention the possibility of merging series transistors in IG FinFETs. Such work also proposes a semi-analytical model to estimate power and performance of the FinFET-based circuits (DATTA, GOEL, et al., 2007). A set of circuits from ISCAS85 benchmark was synthesized using two cell libraries composed of few elements, which were proposed by the authors.

*First Library:* The first library contains just three logic cells: 2-input NAND, 2-input NOR, and INVERTER. These cells were designed using single-gate SG FinFETs and each cell has different versions of size.

**Second Library:** The second library contains all logic cells from the first library and more five low power cells designed with IG FinFETs, which are presented in the paper.

The cells of these libraries were characterized and the circuits were synthesized through commercial EDA tools. This experiment demonstrated a significant reduction in power and area of the ISCAS85 circuits. The results obtained by using the second library, based on IG FinFETs, present an average reduction of

18% and 8.5% in power dissipation and design area, respectively, when compared to the first library results.

### 2.2.3 Wang (WANG, 2010)

Wang presents a methodology to explore the separated gates of the IG FinFETs (WANG, 2010). Basically, the paper presents electrical simulations demonstrating the possibility of merging series and parallel transistors in IG FinFETs, using different thresholds for series and parallel merging. The author reports that the increase in the threshold of an IG FinFET, to allow the series merging, degrades the transistor performance. Moreover, the transistor cannot works in a voltage lower than 1.0 V to enable the series merging. However, the author demonstrates that these problems do not prohibit the use of IG FinFET (series).

The paper presents an algorithm to explore the possibility of generating optimized transistor arrangements by merging series and parallel transistor in IG FinFETs. The algorithm starts from the set of minterms from a given logic function and generates all combinations of the minterms, producing a new set called by the author as *Power Set* (PS). In the sequence, the groups of PS that can be implemented in SG FinFETs or in IG FinFETS are separated in another set called SPS. The next step is to perform intersection and union operations among the elements from SPS. Finally, the results produced by such operations are mapped to series and parallel association of transistors in a network. This algorithm is repeated to generate a network for the complementary plan of the logic gate.

As results, the author presents new implementations for a majority gate, a 2-input MUX, a 3-input XOR, and for a comparator. These implementations were designed in static CMOS and also in *Pass-Transistor Logic* (PTL). In general, the solutions based in IG FinFETs presented reduction in power dissipation and area while the solutions based in SG FinFETs and PTL presented an increase of 52% and 98% in power and area, respectively. However, the solutions designed with SG FinFETs have greater performance.

Although the paper presents an algorithm for IG FinFET transistor networks generation, the author does not make clear whether such algorithm was implemented and tested for a large set of functions. The paper presents results for a very small set of five logic functions. Moreover, the algorithm presented in the paper is not enough

to understand how the networks are generated. The author does not present a complete example demonstrating how the networks are built.

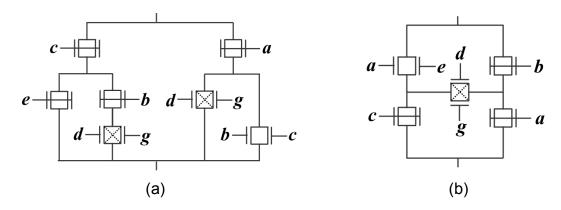

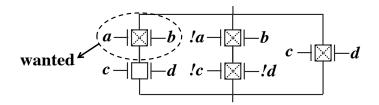

#### 2.2.4 Rostami et al. (ROSTAMI e MOHANRAM, 2011)

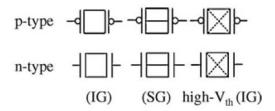

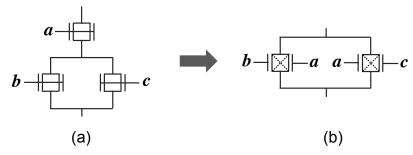

Rostami et al. present a set of electrical and geometric configurations to determine the appropriated threshold needed to design IG FinFETs  $high-V_{th}$  and IG FinFETs  $low-V_{th}$  (ROSTAMI e MOHANRAM, 2011). A  $high-V_{th}$  transistor implements a series arrangement of two input signal, as previous presented in (WANG, 2010) (CHIANG, KIM, et al., 2006). On the other hand, the  $low-V_{th}$ , transistor implements a parallel arrangement of two input signals, equivalent to a  $regular-V_T$  transistor previously presented in (CHIANG, KIM, et al., 2006). Fig. 8 shows the notations proposed in (ROSTAMI e MOHANRAM, 2011) to represent different kinds of FinFETs.

Figure 8 - Representation of different kinds of FinFETs proposed in (ROSTAMI e MOHANRAM, 2011).

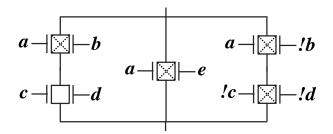

The authors propose two techniques for defactoring Boolean expressions in order to leverage the merging of series and parallel transistor in IG FinFETs. For instance, a conventional network for the expression  $(a + (b \cdot c))$  can be implemented with three SG FinFETs, as illustrates in Fig. 9(a). However, by defactoring such expression we obtain  $((a + b) \cdot (a + c))$ , which needs only two IG FinFETs  $low-V_{th}$  to implement the target function, as illustrated in Fig. 9(b). Similarly, the Fig. 9(c) presents a network composed of three SG FinFETs to implement the expression  $(a \cdot (b + c))$ . The defactorization produces  $((a \cdot b) + (a \cdot c))$ , allowing an optimized implementation using only two IG FinFET  $high-V_{th}$ , as shown in Fig. 9(d).

Figure 9 - Defactorizations proposed in (ROSTAMI e MOHANRAM, 2011).

Notice that, such defactorization technique tends to decrease the transistor count needed to implement a given logic function. In general, it contributes to design optimized logic gates and minimize area, capacitance and power dissipation. In this sense, the authors propose three libraries composed of low power logic cells implemented with SG FinFETs and IG FinFETs  $high-V_{th}$  and  $low-V_{th}$ . These libraries were designed as follow:

**Basic library:** Contains some elementary gates as INV, 2-input AND, 2-input OR, 3-input NAND, 3-input NOR, and so on. All of the gates were implemented using only SG FinFETs.

Library proposed in previous works: This library has 41 gates, composed of the basic library presented above and adding other gates designed by merging transistors and disabling back gates, previously proposed in the literature (MUTTREJA, AGARWAL e JHA, 2007) (DATTA, GOEL, et al., 2007).

**Complete library:** This library with 135 cells uses  $high-V_{th}$  devices along with regular  $low-V_{th}$  devices, and contains all the gates that are designed by merging series or parallel merging, along with the gates designed by

defactoring the Boolean equations. This library is a super-set of the two previous libraries.

Each gate is represented in the libraries by four different strengths, *i.e.*, 1X, 2X, 3X, and 4X. The strength of FinFET gates can be increased by adding parallel fins in each of its transistors. The ISCAS and OpenSPARC benchmark circuits were synthesized using the proposed libraries through the *Synopsys Desing Compiler*. The experiment demonstrated that the complete library brings a significant reduction in area and power for the circuits. On average, the complete library reduces total power and number of fins by 36% and 37%, respectively, over the basic library based on conventional SG FinFETs in 32 nm technology. On the other hand, the previous work library achieves 20% and 21% reduction in total power and number of fins, respectively, over the basic library based on SG FinFETs in 32 nm technology (ROSTAMI e MOHANRAM, 2011).

Although the authors present a defactorization technique to improve the merging of series and parallel transistors, the paper does not present and automated method for IG FinFET transistor network generation. Thus, it is not clear how the 135 logic gates from the complete library were generated, insinuating that the library was manually generate.

#### 2.3 The State of the Art on Transistor Network Generation

The switch network generation arises in the 1930 years, when Claude Elwood Shannon studied techniques to build logic networks based on Boolean algebra. Thus, Shannon designed the Master's thesis entitled "A Symbolic Analysis of Relay and Switching Circuits" (SHANNON, 1938), which becomes the reference in the digital design fewer years later.

In the last decades, different methods to generate optimized transistor networks were published in the literature. Part of them is based on factorization techniques and another part is based on graph optimizations. The main characteristics of the factorization method is that the final solution always is a seriesparallel (SP) transistor network. It is due to the AND and OR operations present in the factored forms. On the other hand, the graph-based methods are able to achieve non-series-parallel (NSP) transistor networks, due to flexibility provided by the graph structure. In general, the SP arrangements contribute to design a more regular layout

compared to the NSP counterparts. The microelectronic industry has explored this characteristic through the *standard cell* libraries. However, the NSP arrangements can implement a given logic function using fewer transistors than the SP arrangements. These different characteristics can be explored according to the design constraints.

The following subsections present a review of the most recent works, published in the literature, for automatic transistor network generation. The main characteristics of such methods are briefly presented here, in order to identify why they are not the best alternative for IG FinFET design. Before to continue, it is important to mention that all these methods were designed thinking in single-gate devices *i. e.,* conventional planar CMOS or single-gate SG FinFETs. Thus, nowadays, these methods may be the best alternative for single-gate devices as SG FinFETs.

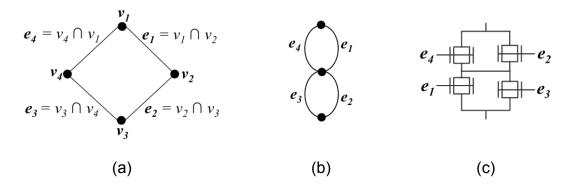

#### 2.3.1 Mintz et al. (MINTZ e GOLUMBIC, 2005)

Mints et al. propose a factorization method based on graph partitioning (MINTZ e GOLUMBIC, 2005). The algorithm is recursive and operates over a logic function and their complement. For each iteration of recursion the function F is represented through the sum of two sub-functions F = F1 + F2 or through the product of two sub-functions F = F3 \* F4. Thus, the algorithm selects one of them to continue the recursion. The sub-functions used to perform a sum, or a product, are determined by computing two graphs  $G_f$  and  $G'_f$  from the function F. These graphs are used to calculate the intersections among the cubes from F. In the sequence, a graph partitioning is performed over  $G_f$  and  $G'_f$  and the best partitioning determines what sub-functions will be selected to continue the recursion.

In general, in the lowest levels of the recursion tree, *read-once* (RO) functions are found. Thus, a special routine is invoked to manipulate these parts of the function. A function is called *read-once* if it can be represented in a factored form where there are not repeated literals. In other words, each variable of the function appears once in the exact factored form (MINTZ e GOLUMBIC, 2005). The method proposed in (MINTZ e GOLUMBIC, 2005) and after improved in (GOLUMBIC, MINTZ e ROTICS, 2008) can achieve the exact solution (minimum number of literals) for *read-once* functions. In addition, this method has a competitive run time when compared with other techniques for *read-once* factorization.

#### 2.3.2 Martins et al. (MARTINS, DA ROSA JUNIOR, et al., 2010)

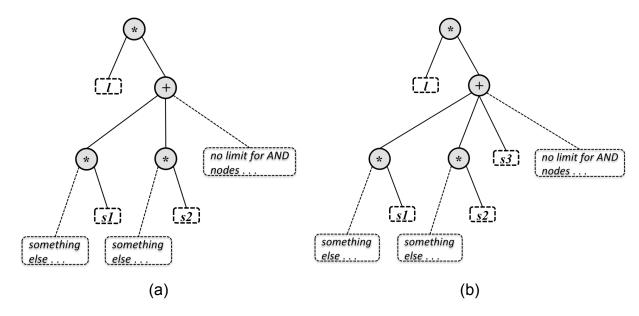

Martins et al. propose a factorization technique based in a new paradigm called *Functional Composition* (FC), which consists in combining small (fewer literals) sub-functions until reaching the target function. The gradual composition allows controlling other criteria, beyond the literal count, of the partial functions and also of the final solution (MARTINS, DA ROSA JUNIOR, *et al.*, 2010).

The proposed algorithm represents logic functions as a pair of *{functionality, implementation}*. The functionality is either a *Binary Decision Diagram* (BDD) node or a truth table. The implementation is either the root of an operator tree or a string representing a factored form. Together with the function implementation other characteristics can be stored like, number of literals, logic depth, series and parallel properties and so on.

The main idea of the algorithm is to produce pairs {functionality, implementation} of logic functions that can be represented by a single literal. After, the algorithm checks if the target function was already implemented with a single literal. If the target function was reached, then the algorithm ends. Otherwise, a loop is started where the sub-functions generated in the previous steps are combined by AND and OR operations to produce new sub-functions with an increase in the number of literals, as illustrated in Fig 10. This process is executed until reaching a factored form for the target function.

Figure 10 - Generation of sub-functions until the 5th bucket, proposed in (MARTINS, DA ROSA JUNIOR, *et al.*, 2010). The number inside braces indicates the bucket composition step order.

This method is able to produce interesting results when compared to other factorization techniques available in the literature. Moreover, through the Functional Composition paradigm it is possible to adopt different criteria during the optimization process. This way, the method can deliver different solutions for a given logic function, each one with a particular impact in the quality of the final solution. However the limitation of this method is the high cost in run time, when the input function grows.

### 2.3.3 Kagaris et al. (KAGARIS e HANIOTAKIS, 2007)

Kagaris et al. propose a method that starts from a logic function f described in a sum-of-products (SOP) form and compose the transistor network gradually (KAGARIS e HANIOTAKIS, 2007). Each cube form f is inserted into the network according to the smallest cost to arrange their literals between two terminal nodes of the network. The authors called a set of literals (switches) in the network as spine, which can be divided in subsets to create new spines. Thus, a new cube can be inserted in the network by sharing their literals with other cubes (spines) already inserted in the network. If the new cube does not have common literals with the spines in the network, then a new independent spine is created between the terminal nodes of the network. For instance, let us consider the network composition illustrated in Fig. 11.

Figure 11 - Example of network composition proposed in (KAGARIS e HANIOTAKIS, 2007).

It is important to mention that the final solution depends on the order that the cubes are placed in the network. The authors propose different heuristics to start the insertion of cubes: examining the cubes in descending (or ascending) order of their literal counts, or examining next the cube that has maximum (or minimum) intersection with the already placed cubes (*spines*), or examining next the cube that

has maximum (or minimum) intersection with some terminal-to-terminal path in the currently constructed network, or simply examining the cubes in some random ordering (KAGARIS e HANIOTAKIS, 2007). As presented in the paper, if there are k candidate orders to starts the optimization process, thus the method can try all of them and choose the best solution.

This method is able to generate NSP arrangements when a new *spine* shares literals with other two different *spines* already placed in the network. To ensure that the network is properly generated, a routine is execute to find and fix false paths in the network. A false path is a sequence of literals (switches) between the terminal nodes that is not covered by any cube form the input function. In some cases, a literal is inserted in the false path in order to transform it in a valid path. The paper presents a significant reduction in transistor count when compared with previous methods (CARUSO, 1991), (ZHU e ABD-EL-BARR, 1993), and (POLI, RIBAS e REIS, 2003).

#### 2.3.4 Possani et al. (POSSANI, CALLEGARO, et al., 2013)

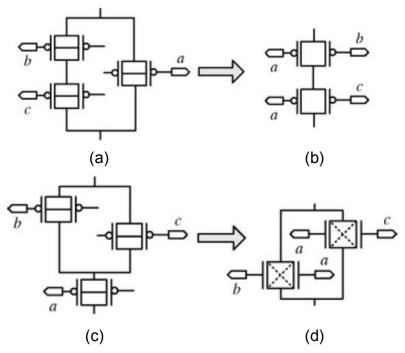

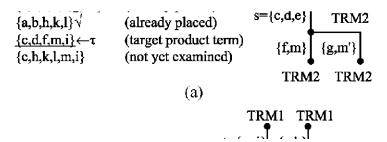

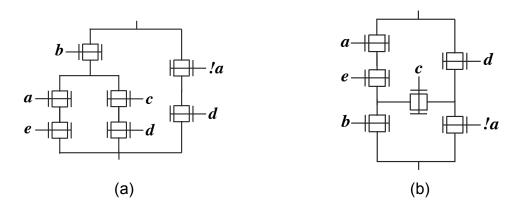

Recently, a new graph-based method for transistor network generation was proposed in (POSSANI, CALLEGARO, *et al.*, 2013). The method starts from an irredundant-sum-of-products (ISOP), and tries to combine the cubes of the function to build NSP and SP kernels. The NSP and SP kernels are graph structures used to determine the relationship among the cubes, as illustrated in Fig. 12(a) and in Fig. 12(b), respectively.

Figure 12 - Kernel structures: (a) NSP and (b) SP proposed in (POSSANI, CALLEGARO, *et al.*, 2013).

The main idea behind the kernels is to avoid greedy choices during the

beginning of the optimization process. In general, the greedy choices are related to local minima, prohibiting that more efficient solutions can be found. Thus, the kernels allow to find optimal sub-structures, which are merged to implement the final network. The method is divided in five well defined steps. The first three steps aim to build the kernels. The last two steps try to compose the found kernels in order to deliver an optimized switch network. Such steps are run in the following sequence: (A) NSP Kernel Finder, (B) SP Kernel Finder, (C) Fake Cube Insertion, (D) Kernel Composition, (E) Edges Compression.

Basically, the step (A) selects four cubes at a time and tries to build a NSP kernel for each combination. The found kernels are stored in a list and the remaining cubes are carried to the step (B). This second step selects four cubes at a time in order to built SP kernels. Similarly, the SP kernels are stored in a list and the remaining cubes are carried to to the step (C). The third step selects three cubes at a time and tries to build a NSP kernel by inserting a fourth cube that is a false cube. A false cube does not contribute with any logic to the network, but is structurally necessary to achieve the optimized arrangement. This way, the cubes of the input ISOP are gradually taken into account according to the kernels that are found. Hence, the number of possible combinations to select the cubes and to build the kernels tends to decrease from the step (A) to the step (C). Finally, the found kernels are associated in parallel and the last two steps (D) and (E) try to share equivalent switches<sup>1</sup> among the kernels, in order to perform local optimizations and remove redundancies.

According to the characteristics of the input ISOP, different situation may occur during the optimization process. A possible situation is that, one of these three first steps may not find any kernel. Thus, the following step receives all cubes still available at that moment. Other situation is that, the routines (A), (B), and (C) may not find any kernel. Thus, the switch network is generated during the steps (D) and (E), by applying an edge sharing technique associated to an edge compression technique. In some cases, multiple kernels can be found during the steps (A), (B), and (C). This way, the method is able to generate more complex networks by merging these kernels during the steps (D) and (E).

-

<sup>&</sup>lt;sup>1</sup> Switches controlled by the same literal are considered equivalentes.

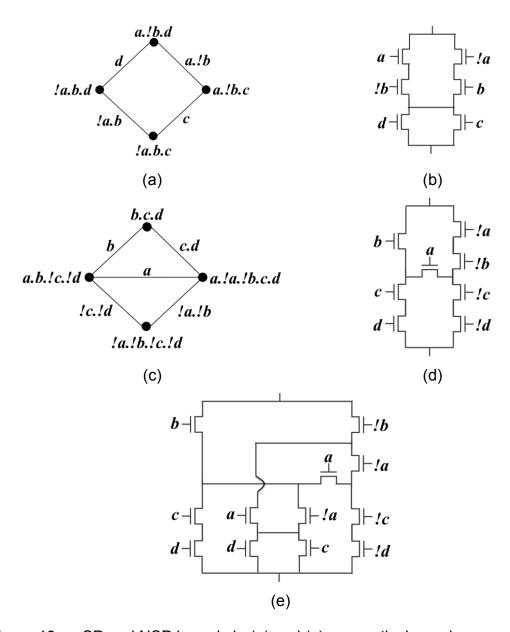

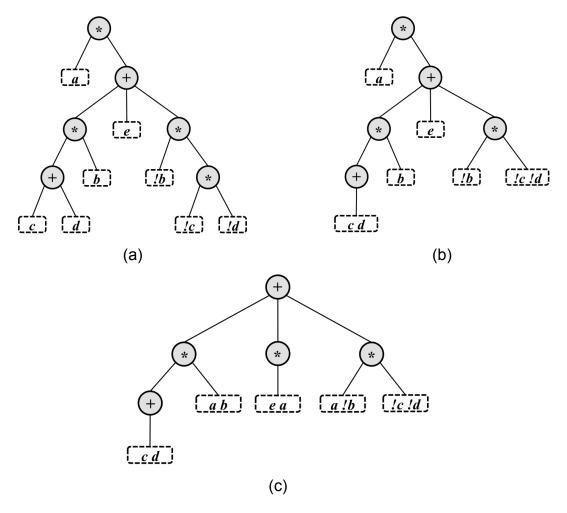

For instance, let us consider the Equation (1) to exemplify how the method works. In this case, the method is able to find a SP kernel and a NSP kernel as illustrated in Fig. 13(a) and Fig 13(c), respectively. Thus, each kernel is translated to their respective network by reordering and mapping the literals of the edges to switches in the network, as illustrated in Fig. 13(b) and Fig. 13(d). In the sequence, the kernel composition step removes redundant switches between these partial networks, resulting in the optimized transistor network illustrated in Fig. 13(e).

$$f = !a.!b.!c.!d + !a.b.d + !a.b.c + a.!b.d + a.!b.c + a.b.!c.!d + b.c.d$$

(1)

Figure 13 - SP and NSP kernels in (a) and (c), respectively, and correspondent networks in (b) and (d). Final solution (e) obtained by compose networks (b) and (d).

The paper presents some experiments over different set of logic functions. The obtained results demonstrate improvements in the transistor count reduction when compared to the results obtained by the most recent methods (KAGARIS e HANIOTAKIS, 2007) (MARTINS, DA ROSA JUNIOR, *et al.*, 2010). The main contribution of this method is the possibility to find promising arrangements in the beginning of the optimization process without performing greedy choices.

# 3 INVESTIGATING AND IDENTIFYING THE NEW CHALLENGES ESTABLISHED BY INDEPENDENT-GATE FINFET TRANSISTORS

This chapter presents some case studies that demonstrate how the merging of series and parallel transistors in IG FinFETs impacts in the transistor network generation. A brief discussion regarding this impact was previously presented in (POSSANI, REIS, *et al.*, 2014). We consider this analysis the main contribution of this work. Although, in the literature, there are many works proposing novel solutions based in IG FinFET transistors, no one of them presents an analysis demonstrating the existence of a new paradigms as we are presenting here. This analysis provides support to design future works related to IG FinFET devices.

In general, a transistor network can be generated by different ways and using different logic styles. In this work we are concerned to generate transistor networks to implement logic gates based in FinFET devices. As a logic gate can be implemented using two complementary networks, one for the *pull-up* and the other one for *pull-down* plane, the proposed methods aim to generate the networks for each plane separately. Thus, in order to simplify the case studies and the examples along of this work, we will consider the transistor network generation for a single plane of the logic gates.

Case 1: The first interesting point is that two different factored forms, which represent the same logic function f and are composed of the same number of literals, can result in transistor networks with a different number of devices. Thus, in order to demonstrate that, let us consider the equivalent factored forms represented by Equation (2) and Equation (3), both composed of 8 literals.

$$f = (a + (d \cdot (b + c))) \cdot (!a + (!b \cdot (!c + !d)))$$

(2)

$$f = ((!a . d) . (c + b)) + ((a . !b) . (!c + !d))$$

(3)

When considering single-gate devices, *i. e.*, conventional CMOS or SG FinFETs, these factored forms can be used to build two different transistor networks to implement the function *f*, both composed of 8 devices. However, when considering the possibility of merging series and parallel transistor in IG FinFETs, it is possible to save 2 transistors by using the Equation (3) instead of using the Equation (2). The IG FinFET transistor network obtained from Equation (2) is illustrated in Fig. 14(a) and the more optimized arrangement, obtained from Equation (3), is illustrated in Fig. 14(b). As can be seen, it is difficult to determine what is the best factored form to be used if just the literal count is adopted as metric. ■

Figure 14 - In (a), transistor network obtained from Equation (2) and in (b), the optimized network obtained from Equation (3).

Case 2: This second case demonstrates that just minimizing the number of literals in a Boolean expression may not lead to the minimum number of IG FinFETs. Let us consider the logic function f, which can be factored of two different ways. One resulting in 14 literals and the other one resulting in 15 literals, as represented in Equation (4) and in Equation (5), respectively.

$$f = (!a + ((!c + !d) \cdot (b + (c + d)))) \cdot ((a \cdot !b) + ((!c + d) \cdot (c + (!d \cdot (a + !b)))))$$

(4)

$$f = ((!b . a) . ((!d . c) + (d . !c))) + ((!d . !c) . ((!b . !a) + (b . a))) + (!a . (d . c))$$

(5)

These two factored forms can be used to build transistor networks composed of single-gate devices. In this case, the networks obtained from Equation (4) and

Equation (5) are composed of 14 and 15 transistors, respectively. As expected, the network obtained from Equation (4) will save one transistor compared to the network obtained from Equation (5). On the other hand, when considering devices like IG FinFETs to implement the function f, we have the opposite. Notice that, through the Equation (4) it is possible to build a network composed of 9 transistors, as shown in Fig. 15(a). However, through the Equation (5), it is possible to build an efficient arrangement using only 8 transistors, as shown in Fig. 15(b). In this case, more literals in the factored form results in fewer transistors in the network. Indeed, the best factored form for single-gate devices may not be the best candidate equation for independent-gate devices and vice versa.

Figure 15 - In (a), network obtained from Equation (4) and in (b), optimized network obtained from Equation (5).

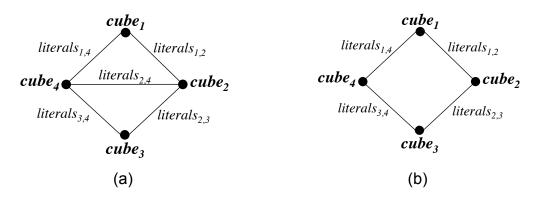

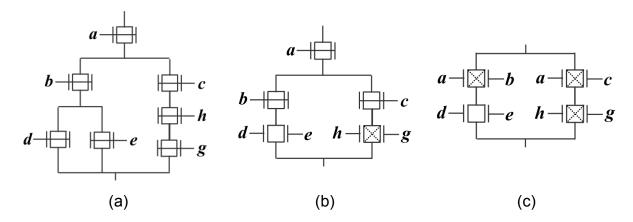

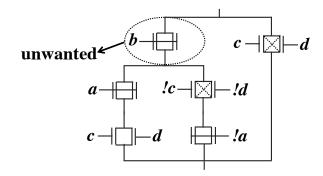

Case 3: When the goal is to minimize the transistor count, the non-series-parallel (NSP) arrangements are a feasible way to do that (POSSANI, CALLEGARO, et al., 2013). In general, the graph-based techniques are able to find NSP arrangements while the factorization methods are limited to series-parallel (SP) arrangements. Thus, when considering single-gate devices, the NSP arrangements can result in a network with the same number of transistors or with fewer transistors than the SP counterpart. However, when considering the merging of series and parallel transistors in IG FinFETs, in some cases, the SP arrangements can result in a network with fewer transistors than the NSP solution.

To demonstrate an instance of this problem, let us consider the Equation (6). This equation can be factored resulting in an expression composed of 7 literals, as presented in Equation (7).

$$f = a.e.b + !a.d + b.c.d$$

(6)

$$f = b \cdot ((a \cdot e) + (c \cdot d)) + (!a \cdot d) \tag{7}$$

Such factored form can be used to build a SP transistor network with 7 single-gate devices, as shown in Fig. 16(a). Another alternative is to apply a graph-based technique over the Equation (6), resulting in a NSP transistor network comprising 6 single-gate devices, as shown in Fig. 16(b). Notice that, the NSP arrangement contributes to decrease the transistor count. Thus, in a first analysis we can claim that the NSP solution is better than the SP one, considering SG FinFETs.

Figure 16 - Two possible solutions to implement the logic function f using SG FinFETs: in (a) SP network and in (b) NSP network.

However, when considering IG FinFETs, the series transistors of the SP network illustrated in Fig. 16(a) can be merged resulting in the network illustrated in Fig. 17(a). Similarly, by merging transistors in the NSP network illustrated in Fig. 16(b), it is possible to achieve the network illustrated in Fig. 17(b). As can be seen, the NSP network results in 5 transistors while the SP network needs only 4 transistors to implement the function *f*. Thus, we have observed that, in some cases, the NSP configuration precludes the merging of transistors. ■

Figure 17 - Two possible solutions to implement the logic function f using IG FinFETs: in (a) SP network and in (b) NSP network.

Case 4: This case demonstrates that in some cases, the NSP arrangements still being the best solution to decrease the transistor count. For instance, let us consider the Equation (8). By applying a factorization technique over this equation we obtain a factored form composed of 10 literals, as presented in Equation (9). Such factored form can be directly mapped to a SP network composed of 10 single-gate devices, as shown in Fig. 18(a). However, when applying a graph-based technique over the Equation (8), it is possible to achieve an efficient NSP arrangement with 7 transistors, as shown in Fig. 18(b).

$$f = a.b + a.c + a.d.g + c.e + b.c.d.g$$

(8)

$$f = c \cdot (e + (b \cdot e \cdot g)) + a \cdot ((d \cdot g) + b + c)$$

(9)

Figure 18 - Two possible solutions to implement the logic function f using SG FinFETs: in (a) SP network and in (b) NSP network.