# AVALIANDO A VIABILIDADE DO USO DE PORTAS LÓGICAS COMPLEXAS CMOS EM CIRCUITOS COMBINACIONAIS DE ALTO DESEMPENHO

BRUNO T. FERRAZ; HENRIQUE C. KESSLER; VINÍCIUS V. A. CAMARGO

Universidade Federal de Pelotas – {btferraz; hckessler; vvacamargo}@inf.ufpel.edu.br

### 1. INTRODUÇÃO

Com o avanço da microeletrônica, novas ferramentas de automação de projetos para circuitos integrados vêm sendo criadas. Antigamente, projetos de circuitos integrados eram feitos manualmente, fato que gerava problemas relacionados a *time-to-market* e custos. Tendo isso em vista, projetistas buscaram opções para automatizar este processo, o que acarretou no surgimento de métodos como o de células padrão. Este método se baseia em uma biblioteca de portas lógicas pré-projetada, as quais são utilizadas pelas ferramentas de automação de projeto para construir circuitos mais complexos.

O uso de portas complexas no mapeamento de circuitos combinacionais têm sido amplamente estudado como alternativa ao método de células padrão (CONCEIÇÃO, 2019). Esta metodologia é aqui referenciada como *design on-the-fly*, e uma de suas virtudes é não se restringir a uma biblioteca de células pré estabelecida, podendo assim mapear circuitos da maneira mais otimizada possível. Também é notável o ganho em características topológicas desta metodologia, como diminuição de transistores e níveis lógicos, além do baixo consumo energético (CONCEIÇÃO, 2019) e de uma maior tolerância a efeitos de degradação (GHANE, 2016) (BRENDLER, 2019). Apesar destes resultados serem promissores, existem poucos estudos que investigam características elétricas de portas complexas.

Visando contribuir para preencher esta lacuna, este trabalho foca em avaliar o impacto de portas complexas no atrasos de propagação e no consumo energético de circuitos combinacionais, além dos impactos em suas características topológicas. Para isso, serão abordados circuitos com versões baseadas em células padrão e portas complexas, buscando extrair padrões entre essas versões e comparar os resultados. Durante a análise dos resultados é importante lembrar que portas complexas têm maior custo, pois não garantem regularidade na etapa de leiaute (UEHARA, 1979), tendo assim maiores perdas em relação a simulações elétricas que não consideram interconexões e outros parasitas extraídos do leiaute. Este fato garante uma vantagem para fluxo de células padrão, mas pode ser inibido pelo desempenho elétrico de portas complexas.

Neste trabalho, um estudo buscando explorar o uso de portas complexas é apresentado e, para isso, será feita uma comparação detalhada entre a metodologia design on-the-fly e fluxo de células padrão em três diferentes circuitos. Na seção 2 estão os conceitos necessários para replicação do estudo, além dos mapeamentos dos circuitos utilizados. Na seção 3 foram destacadas algumas particularidades extraídas de algumas versões dos circuitos, além de conter inferências sobre padrões apresentados. A seção 4 apresenta conclusões baseadas nos valores obtidos a partir das simulações elétricas.

#### 2. METODOLOGIA

Com o objetivo de se avaliar o impacto do uso de portas complexas no desempenho elétrico de circuitos combinacionais, implementações com e sem o uso de portas complexas das funções F e G, descritas nas equações (1) e (2)

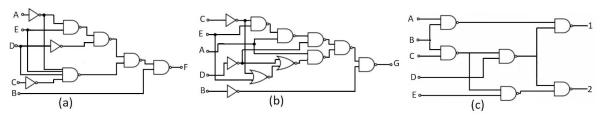

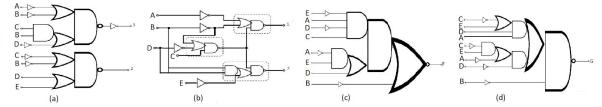

respectivamente, e circuito C17 do *Benchmark* ISCAS'85 (BRGLEZ, 1985) serão analisados. As implementações por células padrão são mostradas na Figura 1, enquanto as versões alternativas destes circuitos utilizando portas complexas são mostradas na Figura 2. No circuito C17, duas versões utilizando portas complexas foram adicionadas, uma delas (a) reduzindo o circuito a apenas duas portas complexas e outra (b) de acordo com o estudo apresentado por Brendler (2019).

$$F = !(B^*!(!(!A^*D^*E^*!C)^*!(!D^*!(!A^*E))))$$

(1)

$$G = !(!B^*!((!A+(!D+!(!C+E)))^*!(!D^*!(A^*!(E^*!C)))))$$

(2)

Figura 1: Versões mapeadas com células padrão dos circuitos das funções (a) F e (b) G, e do circuito (c) C17 do *benchmark* ISCAS'85.

Figura 2: Versões alternativas dos circuitos ISCAS'85 C17 (a) contendo apenas duas portas complexas e (b) seguindo a implementação apresentada por BRENDLER (2019), e das funções (c) F e (d) G.

As redes de transistores CMOS das portas complexas utilizadas nas simulações serão geradas pela ferramenta SwitchCraft (CALLEGARO, 2010), utilizando *Factorization Method* para criação da rede de transistores que implementa a porta lógica. O dimensionamento dos transistores será feito utilizando o método *Logical Effort* (SUTHERLAND, 1999), com o parâmetro lambda igual a 1,32643.

As análises elétricas serão baseadas em simulações SPICE na tecnologia 45nm CMOS TSMC TT. Para se obter um ambiente de simulação do *Design Under Test* (DUT) mais realista, serão usadas as convenções de Fan-Out 4 e as entradas atravessam dois inversores mínimos antes de conectarem-se ao DUT. Além disso, os pulsos de sinal de cada entrada serão estabelecidos de forma que todos os arcos de transição das expressões sejam considerados, lembrando que um arco é definido como a situação em que apenas um bit da entrada é alterado e leva a uma alteração no bit de saída.

Nas simulações elétricas serão coletados dados de atraso de propagação em cada uma das funções e consumo energético, dividido em potência estática e dinâmica. Além das características elétricas, características topológicas como número de transistores, número de níveis lógicos e uma estimativa da área ocupada pelo circuito, calculada a partir da soma do produto entre a largura e comprimento de canal de cada transistor, também serão avaliados.

#### 3. RESULTADOS E DISCUSSÃO

A tabela 1 resume os resultados obtidos com o projeto dos circuitos combinacionais com e sem portas complexas seguindo a metodologia descrita na seção anterior. Dentre os dados apresentados, alguns são extraídos dos esquemáticos de cada circuito, como número de transistores e níveis lógicos, e outros das simulações elétricas, como o atraso máximo, a potência estática média e a potência dinâmica. Os dados de atraso, potência e área apresentados na Tabela 1 são normalizados para cada circuito de acordo com os valores obtidos com o mapeamento por células padrão.

Tabela 1: Resumo dos resultados obtidos nas simulações elétricas das versões de cada circuito combinacional.

| Circuito        | Versão                       | Número de<br>transistores | Níveis<br>lógicos | Atraso<br>máximo* | Potência<br>Estática<br>média* | Potência<br>dinâmica* | Área<br>estimada* |

|-----------------|------------------------------|---------------------------|-------------------|-------------------|--------------------------------|-----------------------|-------------------|

| Função<br>F     | Células padrão               | 26                        | 5                 | 1                 | 1                              | 1                     | 1                 |

|                 | Complexo                     | 24                        | 2                 | 1,20              | 1,29                           | 1,44                  | 1,63              |

| Função<br>G     | Células padrão               | 48                        | 6                 | 1                 | 1                              | 1                     | 1                 |

|                 | Complexo                     | 26                        | 3                 | 1,02              | 1,00                           | 1,03                  | 1,32              |

| ISCAS'85<br>C17 | Células padrão               | 24                        | 3                 | 1                 | 1                              | 1                     | 1                 |

|                 | Complexo                     | 28                        | 3                 | 1,16              | 1,27                           | 1,25                  | 1,44              |

|                 | Complexo<br>(BRENDLER, 2019) | 28                        | 3                 | 1,20              | 1,13                           | 1,23                  | 1,13              |

<sup>\*</sup> Os dados apresentados estão normalizados para cada circuito baseado na versão com células padrão.

Fonte: Do autor

Analisando a tabela 1, nota-se que o mapeamento de versões com portas complexas tende a diminuir o número de transistores e níveis lógicos em relação a mapeamentos com células padrão – fato que não se aplica ao circuito C17, que possui múltiplas saídas. Partindo disso, uma hipótese razoável seria de que tal diminuição também estaria relacionada à menores valores de atrasos, área e consumo. No entanto, se percebe que mapeamentos com células padrão tiveram, em média, números de atraso máximo (14,5%), área (38%) e potências dinâmica (23,75%) e estática média (17,25%) superiores em relação à suas respectivas versões com portas complexas. Vale ressaltar que durante o projeto, busca-se reduzir ao máximo todas estas métricas.

Dentre os circuitos estudados, os que implementam a função F foram os que tiveram maior discrepância entre os valores. O atraso máximo da versão complexa foi 20% maior que a com células padrão. Tal situação ocorre porque o arco de maior atraso precisa passar por um grande número de transistores em série, neste caso são 5 transistores. O aumento do número de transistores em série também leva a uma maior área devido ao método de dimensionamento utilizado, o *Logical Effort*, e a um maior consumo de energia. O maior número possível de transistores em série em uma dada porta é o número de entradas que esta possui.

Por outro lado, as duas versões da função G sugerem um padrão, se comparadas com os outros dois circuitos: quanto maior for a diminuição de transistores e níveis lógicos em relação ao modelo células padrão, melhor será o

desempenho elétrico da versão complexa. Neste circuito, em que houve uma diminuição de 46% do número de transistores e 50% de níveis lógicos, foi onde os valores de atraso máximo (2%), potências estática (0%) e dinâmica (3%) foram menos distantes entre as versões complexa e por células padrão. Mesmo neste caso, a implementação com portas complexas não teve características elétricas superiores, apesar dos ganhos topológicos.

As implementações baseadas em portas complexas também não apresentaram melhorias em relação ao atraso médio. Ao avaliarmos a função G, notamos que o caminho lógico máximo percorrido pela entrada B é dois níveis lógicos. Este caminho garante ótimos resultados de atraso. Quando reduzimos o circuito a uma porta complexa, este caminho continua tendo bons valores, mas piores que da versão original. Este fato contribui para o aumento do atraso médio do circuito na versão complexa. Estudos em nível de sistema, no entanto, priorizam o estudo do atraso máximo uma vez que este é o que limita a frequência de operação do circuito.

#### 4. CONCLUSÕES

Neste trabalho foi avaliado o desempenho elétrico de três circuitos combinacionais mapeados com portas complexas e com células padrão. Os resultados obtidos sugerem que mapeamentos feitos a partir de portas complexas têm piores características elétricas em relação ao fluxo de células padrão. Apesar da redução em parâmetros topológicos, como o número de transistores e de níveis lógicos, a presença de um grande número de transistores em série nas portas complexas avaliadas levou a um prejuízo nas métricas de atraso e potência.

## 5. REFERÊNCIAS BIBLIOGRÁFICAS

CONCEIÇÃO, C. M. D. O.; REIS, R. A. D. L. Transistor Count Reduction by Gate Merging, **IEEE Trans. Circuits Syst. I, Reg. Papers**, vol. 66, no. 6, pp. 2175--2187, 2019.

GHANE, M.; ZARANDI, H. R. Gate Merging: An NBTI Mitigation Method to Eliminate Critical Internal Nodes in Digital Circuits, **2016 24th Euromicro Int. Conf. on Parallel, Distrib., and Network-Based Process. (PDP)**, 2016.

BRENDLER, L. et al. Gate mapping impact on variability robustness in FinFET technology. **Microelectronics Reliability**, v. 100, p. 113448, 2019.

BRGLEZ, F. Neutral netlist of ten combinational benchmark circuits and a target translator in FORTRAN. In: **Special session on ATPG and fault simulation**, **Proc. IEEE Int. Symp. Circuits and Systems**, **June 1985**. 1985. p. 663-698.

CALLEGARO, V. et al. SwitchCraft: a framework for transistor network design. In: **Proc. of the 23rd symp. on Integrated circuits and system design**. 2010. p. 49-53.

SUTHERLAND, I. et al. **Logical effort: designing fast CMOS circuits**. Morgan Kaufmann, 1999.

UEHARA, T. VANCLEEMPUT, W. M. Optimal Layout of CMOS Functional Arrays, **16th Design Automation Conference**, San Diego, CA, USA, 1979, pp. 287-289.