**UNIVERSIDADE FEDERAL DE PELOTAS**

**Centro de Desenvolvimento Tecnológico**

**Programa de Pós-Graduação em Computação**

Dissertação

**Dedicated Hardware Architectures for the Affine Motion Estimation of Versatile

Video Coding Video Standard for Real-Time UHD Videos**

**Marcello Morales Muñoz**

Pelotas, 2025

**Marcello Morales Muñoz**

**Dedicated Hardware Architectures for the Affine Motion Estimation of Versatile

Video Coding Video Standard for Real-Time UHD Videos**

Dissertação apresentada ao Programa de Pós-Graduação em Computação do Centro de Desenvolvimento Tecnológico da Universidade Federal de Pelotas, como requisito parcial à obtenção do título de Mestre em Ciência da Computação.

Advisor: Prof. Dr. Marcelo Schiavon Porto

Coadvisores: Prof. Dr. Luciano Agostini

Prof. Dr. Guilherme Corrêa

Pelotas, 2025

Universidade Federal de Pelotas / Sistema de Bibliotecas

Catalogação da Publicação

M967d Muñoz, Marcello Morales

Dedicated hardware architectures for the Affine motion estimation of versatile video coding video standard for real-time UHD videos [recurso eletrônico] / Marcello Morales Muñoz ; Marcelo Schiavon Porto, orientador ; Luciano Agostini, Guilherme Corrêa, coorientadores. — Pelotas, 2025.

81 f.

Dissertação (Mestrado) — Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, 2025.

1. Hardware. 2. Affine ME. 3. H.266/VVC. 4. Motion estimation. I. Porto, Marcelo Schiavon, orient. II. Agostini, Luciano, coorient. III. Corrêa, Guilherme, coorient. IV. Título.

CDD 005

Elaborada por Dafne Silva de Freitas CRB: 10/2175

**Marcello Morales Muñoz**

**Dedicated Hardware Architectures for the Affine Motion Estimation of Versatile

Video Coding Video Standard for Real-Time UHD Videos**

Dissertação aprovada, como requisito parcial, para obtenção do grau de Mestre em Ciência da Computação, Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas.

**Data da Defesa:** 6 de dezembro de 2024

**Banca Examinadora:**

Prof. Dr. Marcelo Schiavon Porto (orientador)

Doutor em Computação pela Universidade Federal do Rio Grande do Sul.

Prof. Dr. Bruno Zatt

Doutor em Microeletrônica pela Universidade Federal do Rio Grande do Sul.

Prof. Dr. Alan Carlos Junior Rossetto

Doutor em Engenharia Elétrica pela Universidade Federal do Rio Grande do Sul.

Prof. Dr. Vladimir Afonso

Doutor em Microeletrônica pela Universidade Federal do Rio Grande do Sul.

## **AGRADECIMENTOS**

Gostaria de agradecer as muitas pessoas que foram fundamentais para mim durante o período do mestrado. Agradeço, primeiramente, aos meus pais, Luiz Eduardo Machado Muñoz e Zoila Morales Fernandes, por todo o apoio que me deram ao longo da minha formação acadêmica, incluindo esta etapa do mestrado.

Gostaria também de expressar minha gratidão ao professor Marcelo Porto, meu orientador. Muito obrigado por ter me aceito como orientando durante a pandemia, mesmo com minha pouca experiência anterior em pesquisa e nesta área de conhecimento. Sou extremamente grato por essa oportunidade.

Agradeço igualmente aos meus co-orientadores, Luciano Agostini e Guilherme Correa, que, junto ao professor Marcelo, me ensinaram muito sobre codificação de vídeo e sobre o mundo da pesquisa acadêmica, áreas com as quais eu tinha pouco contato antes de iniciar o mestrado.

Meus sinceros agradecimentos também ao Murilo Perleberg, que me auxiliou bastante durante todo o processo do mestrado, e ao Denis Maass, cujo apoio foi igualmente essencial no desenvolvimento do meu trabalho. A contribuição de ambos foi crucial para a conclusão desta jornada.

Também quero expressar minha gratidão ao ViTech (Video Technology Research Group), do qual faço parte. Sem a infraestrutura e o suporte do grupo, este mestrado não teria sido possível.

Por fim, deixo meus agradecimentos à UFPel, onde iniciei minha trajetória em 2014 como estudante de graduação em engenharia da computação. Foi ali que aprendi tudo sobre computação e onde conheci quase todas as pessoas que, de alguma forma, contribuíram para este trabalho.

## ABSTRACT

MUÑOZ, Marcello Morales. **Dedicated Hardware Architectures for the Affine Motion Estimation of Versatile Video Coding Video Standard for Real-Time UHD Videos.** Advisor: Marcelo Schiavon Porto. 2025. 81 f. Dissertation (Masters in Computer Science) – Technology Development Center, Federal University of Pelotas, Pelotas, 2025.

The demand for streaming digital videos over the internet has significantly increased in recent years. This substantial rise in video data traffic requires efficient compression techniques for storage and transmission. Moreover, these compression techniques must preserve image quality while addressing energy consumption and real-time processing constraints. In this context, the Versatile Video Coding (VVC) compression standard, also known as H.266, is the state-of-the-art video compression standard released in July 2020 by the Joint Video Experts Team (JVET).

VVC introduced several new tools to aid video compression compared to its predecessor, the H.265/HEVC standard. This results in significant gains in compression efficiency (the ratio of bit rate reduction to the encoded video quality), allowing for more efficient transmission or storage of digital videos. One of the new tools added in VVC is Affine prediction, which is used to characterize non-translational motion. This new tool has the highest computational cost in the entire inter-frame prediction stage of the VVC encoder. However, Affine prediction can provide gains of up to 2.18% in compression efficiency (BD-Rate) in exchange for a 5.26% increase in encoding time.

Affine prediction supports two versions, using four or six parameters, where two or three motion vectors are used, respectively. These vectors are inherited from the reference block to be encoded and are used for reconstructing the block. This work was designed and synthesized using ASIC hardware architectures for the Affine motion estimation in the VVC standard, focusing on low energy consumption. The architectural design emphasizes the capability to process real-time UHD 4K videos ( $3840 \times 2160$ ), aiming for its application in mobile devices. Three architectures are presented: One for Affine motion compensation with an area utilization of 189k Gates and 121mW power dissipation. Another for the architecture that calculates the Affine  $\Delta MV$  with 245k Gates and 31mW of power dissipation. Also, an initial version of the gradient-based coefficient generator is presented with 6,900k Gates and 4.8W power dissipation.

Keywords: Hardware; H.266/VVC; Affine ME; Motion Estimation.

## RESUMO

MUÑOZ, Marcello Morales. **Arquiteturas de Hardware Dedicada para a Estimação de Movimento Affine UHD em tempo real do Padrão de Compressão de Vídeo Versatile Video Coding.** Orientador: Marcelo Schiavon Porto. 2025. 81 f. Dissertação (Mestrado em Ciência da Computação) – Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, Pelotas, 2025.

A demanda de streaming de vídeos digitais pela internet está aumentando de forma significativa nos últimos anos. Este grande aumento no tráfego de dados de vídeo requer técnicas de compressão eficientes para armazenamento e transmissão. Além disso, estas técnicas de compressão devem preservar a qualidade da imagem, enquanto lidam com restrições de consumo de energia e processamento em tempo real. Neste cenário, o padrão de compressão de vídeo *Versatile Video Coding* (VVC), também conhecido como H.266, é o padrão de compressão de vídeo estado-da-arte, tendo sido lançado em julho de 2020 pelo *Joint Video Experts Team* (JVET).

O VVC adicionou diversas novas ferramentas para auxiliar na compressão de vídeo, quando comparado ao seu antecessor, o padrão H.265/HEVC. Desta forma, proporcionando grandes ganhos em termos de eficiência de compressão (relação entre redução da taxa de bits e a qualidade do vídeo codificado) e permitindo a transmissão ou armazenamento de vídeos digitais de forma mais eficiente. Uma das novas ferramentas adicionadas no VVC é a predição *Affine*, que é utilizada para caracterizar movimentos não-translacionais, sendo que essa nova ferramenta possui o maior custo computacional de toda a etapa de predição inter-quadros do codificador VVC. A predição *Affine* pode trazer ganhos de até 2,18% na eficiência de compressão (BD-Rate) em troca de um aumento de 5,26% no tempo de codificação.

A predição *Affine* suporta duas versões, utilizando quatro ou seis parâmetros, onde dois ou três vetores de movimento são usados, respectivamente. Esses vetores são herdados do bloco de referência a ser codificado e são usados para reconstruir o bloco. Neste trabalho foi projetado e sintetizado arquiteturas de *hardware ASIC* para predição *Affine* do padrão VVC com foco em baixo consumo de energia. As arquiteturas são projetadas para processar vídeos UHD 4K ( $3840 \times 2160$ ) em tempo real, visando sua aplicação em dispositivos móveis. Três arquiteturas são apresentadas: uma para compensação de movimento *Affine*, com uma de área de 189k Gates e dissipação de potência de 121mW. Outra para a arquitetura que calcula o  $\Delta MV$  *Affine*, com 245k Gates e dissipação de 31mW. Além disso, uma versão inicial do gerador de coeficientes baseado em gradiente do *Affine* com 6.900k Gates e dissipação de 4,8W.

Palavras-chave: Hardware; H.266/VVC; Affine ME; Estimação de movimento.

## LIST OF FIGURES

|           |                                                                                                                                                                          |    |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1  | Flowchart of the video compression . . . . .                                                                                                                             | 19 |

| Figure 2  | Elements present in the ME (Porto, 2012) . . . . .                                                                                                                       | 20 |

| Figure 3  | Search process of the ME . . . . .                                                                                                                                       | 21 |

| Figure 4  | Affine models. (a) 4-Parameter with LT and RT MVs. (b) 6-Parameter with LT, RT, and LB MVs. . . . .                                                                      | 22 |

| Figure 5  | Affine AMVP Algorithm. . . . .                                                                                                                                           | 23 |

| Figure 6  | Affine representation of the subblock split, where 16 subblocks with 4x4 samples compose one 16x16 PU. Each subblock has its own SMV. . . . .                            | 24 |

| Figure 7  | Representation of diagonal interpolation of a 4x4 subblock. The blue squares are the integers, the triangles are horizontal, and the stars are diagonal samples. . . . . | 25 |

| Figure 8  | Representation of the Gradient-Based Iterative Algorithm. . . . .                                                                                                        | 27 |

| Figure 9  | The kernel Sobel Filter in the X- and Y-direction. . . . .                                                                                                               | 28 |

| Figure 10 | Representation of the Block-Matching Iterative Algorithm. . . . .                                                                                                        | 32 |

| Figure 11 | Representation of all the BMIA possible positions explored after three rounds for <b>one</b> CPMV. . . . .                                                               | 33 |

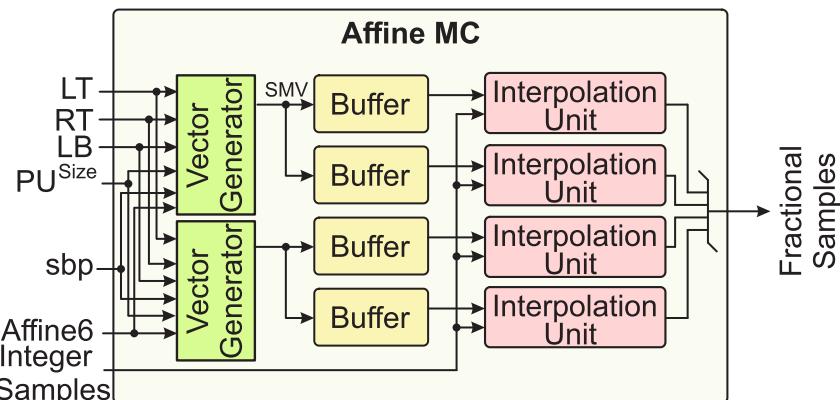

| Figure 12 | High-level architecture of Affine MC . . . . .                                                                                                                           | 47 |

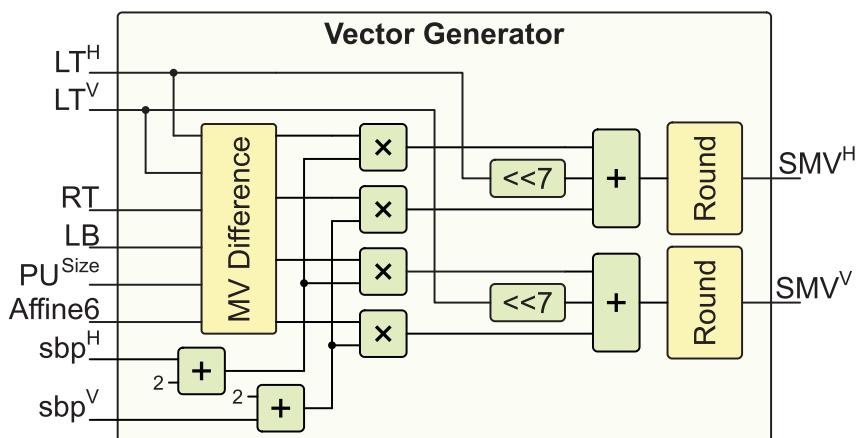

| Figure 13 | Architecture of the Vector Generation unit . . . . .                                                                                                                     | 48 |

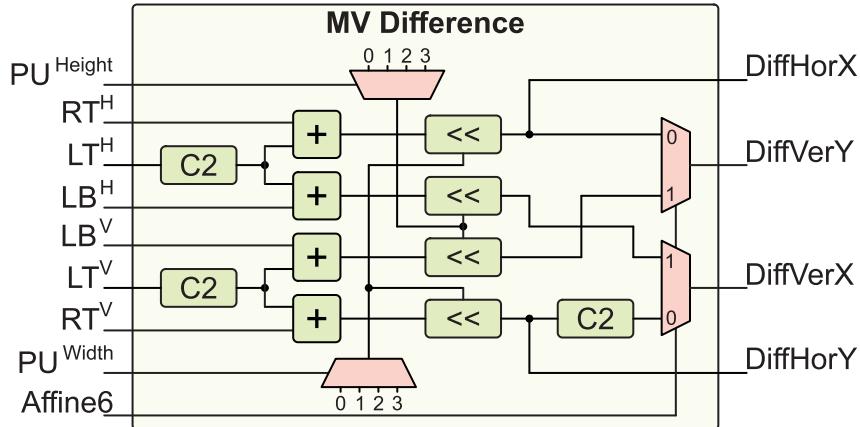

| Figure 14 | Architecture that calculates MV differences . . . . .                                                                                                                    | 49 |

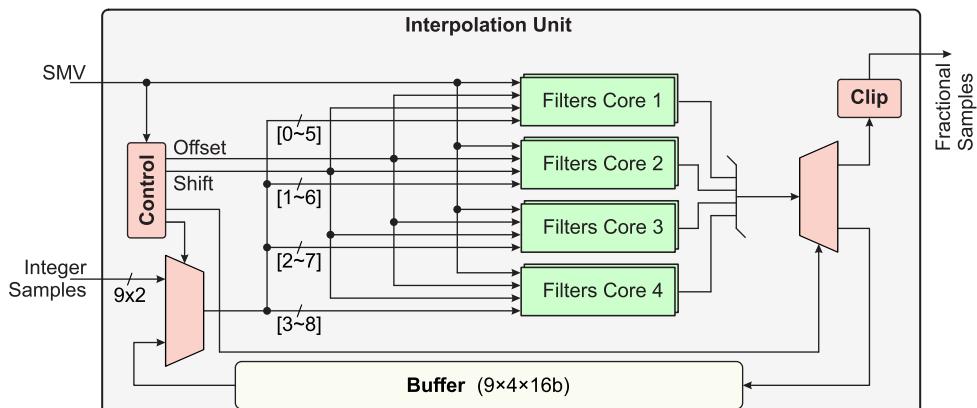

| Figure 15 | Architecture of the Interpolation Unit . . . . .                                                                                                                         | 49 |

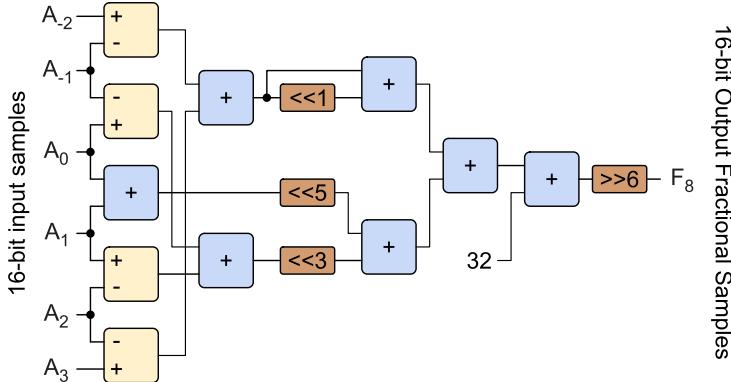

| Figure 16 | Proposed Architecture of the Interpolation Filter $F_8$ . . . . .                                                                                                        | 50 |

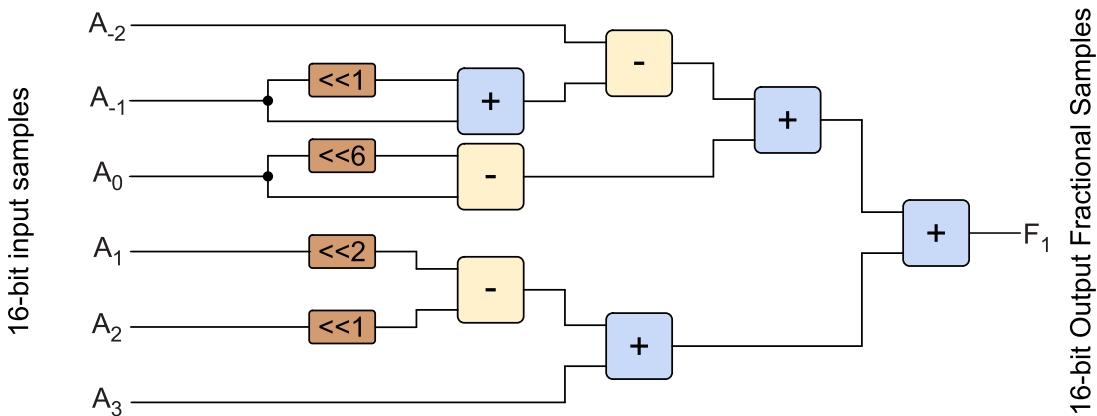

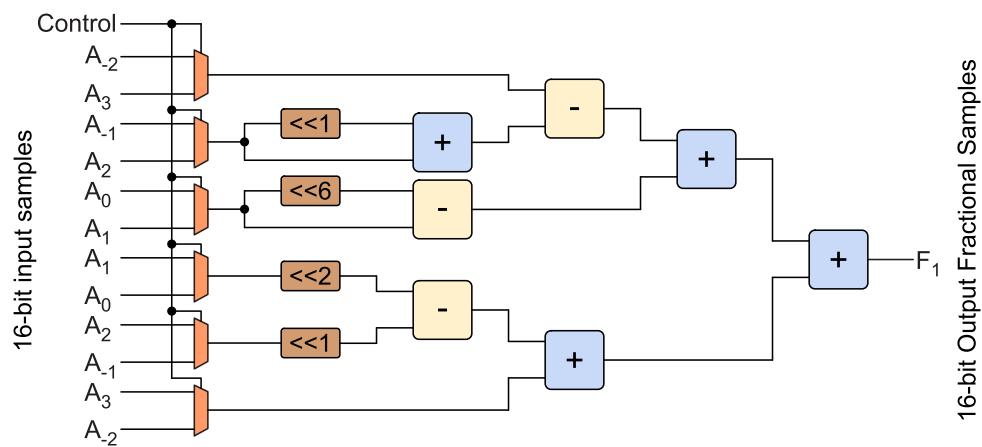

| Figure 17 | Implementation of the Filter $F_1$ using a multiplierless approach in the Baseline architecture . . . . .                                                                | 50 |

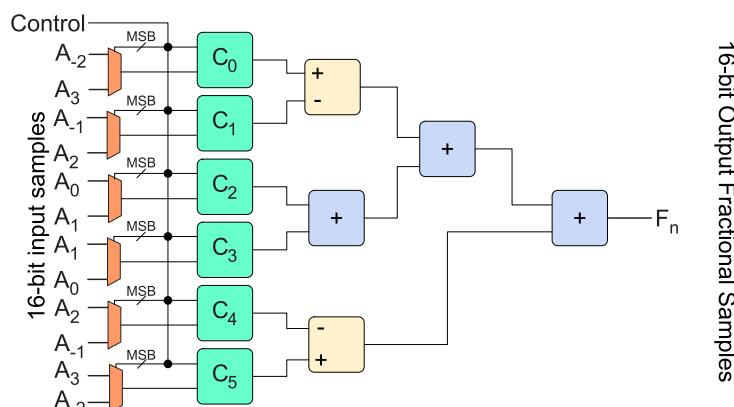

| Figure 18 | Proposed Architecture of the Interpolation Filter $F_1$ or $F_{15}$ (used in the PE architecture), depending on the order of the inputs. . . . .                         | 51 |

| Figure 19 | Proposed Hardware-Efficient Architecture. . . . .                                                                                                                        | 52 |

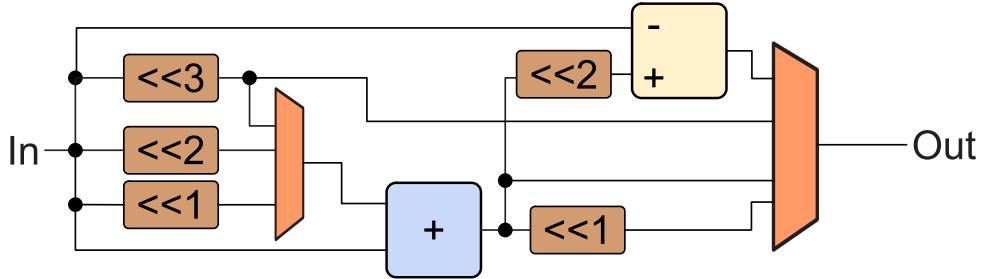

| Figure 20 | The Architecture of the Coefficient Multiplier $C_1$ , used in HE architecture. . . . .                                                                                  | 53 |

| Figure 21 | Time diagram of the Affine MC architecture when $LT = [4, -1332]$ and $RT = [-72, -1336]$ . . . . .                                                                      | 54 |

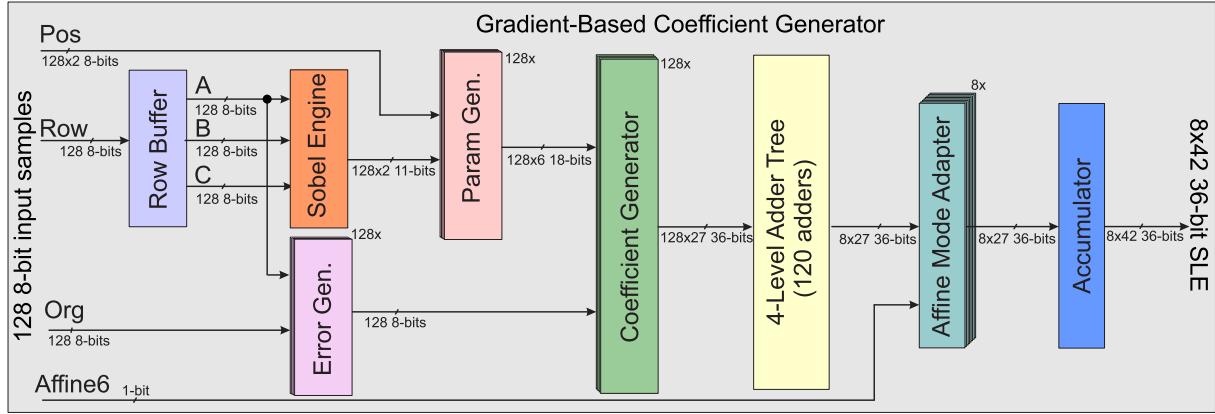

| Figure 22 | High-level architecture of the GBIA . . . . .                                                                                                                            | 55 |

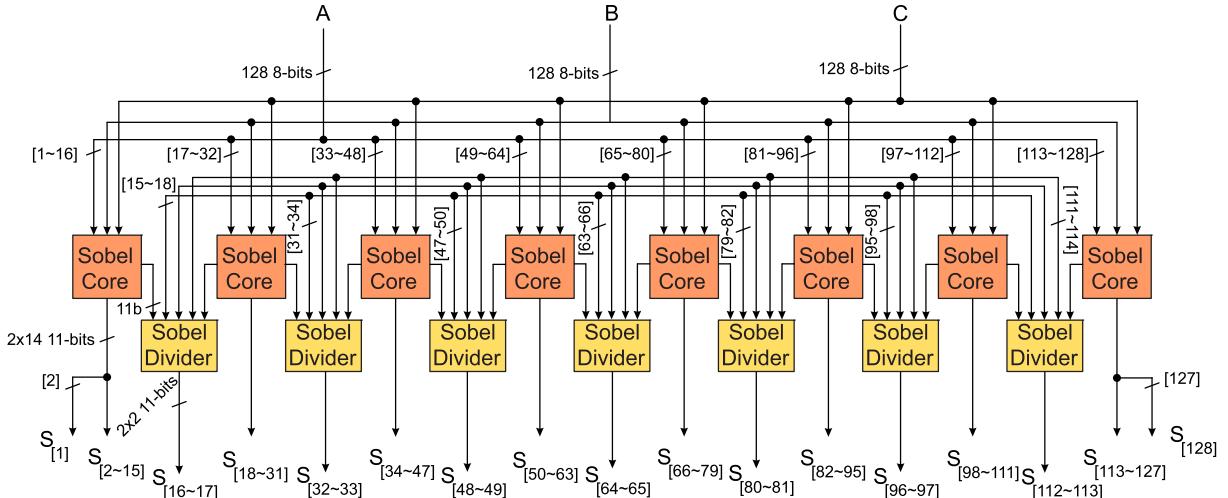

| Figure 23 | Architecture of the Sobel Engine . . . . .                                                                                                                               | 55 |

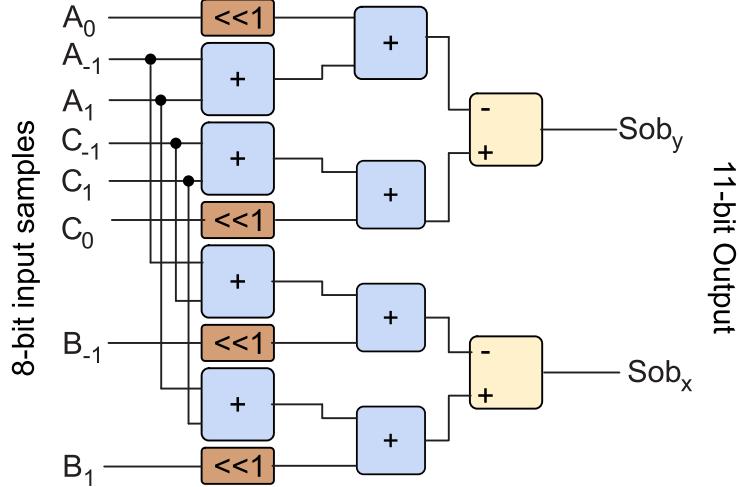

| Figure 24 | Sobel Unit architecture . . . . .                                                                                                                                        | 56 |

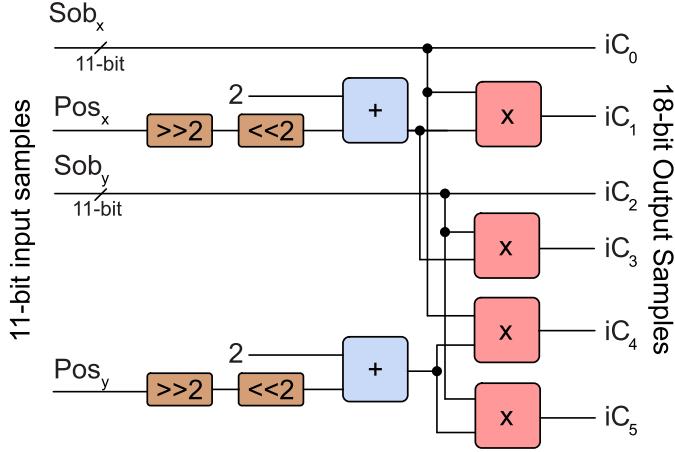

| Figure 25 | Architecture of the Affine Parameter Generator . . . . .                                                                                                                 | 57 |

| Figure 26 | Architecture of the Coefficient generator . . . . .                                                                                                                      | 57 |

|           |                                                                         |    |

|-----------|-------------------------------------------------------------------------|----|

| Figure 27 | Architecture of the Affine Mode Adapter . . . . .                       | 58 |

| Figure 28 | Architecture of the Affine Mode Adapter Converter . . . . .             | 58 |

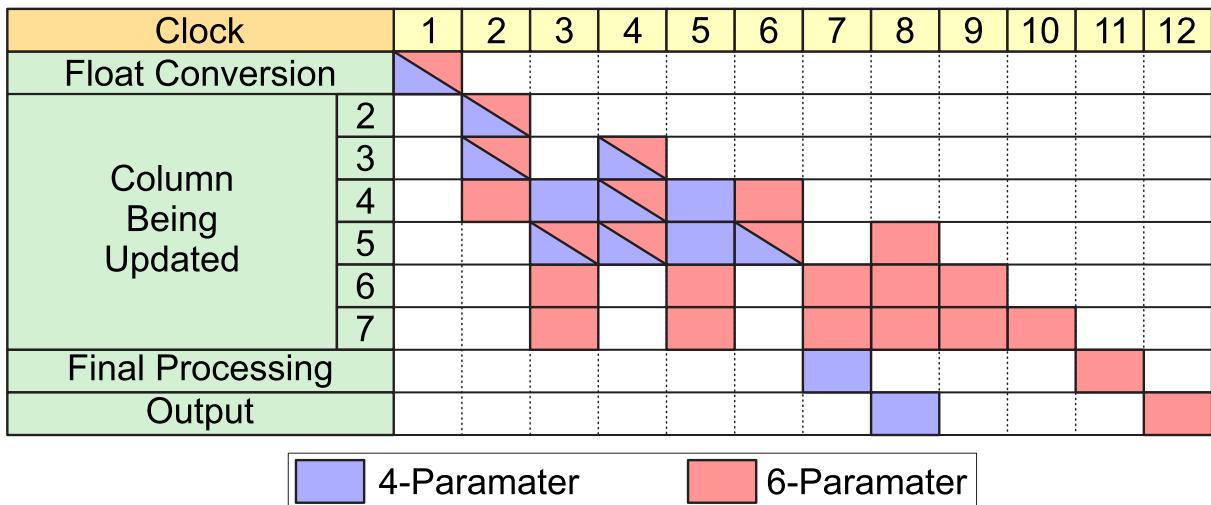

| Figure 29 | Temporal Analysis of the Gradient-Based Coefficient Generator . . . . . | 60 |

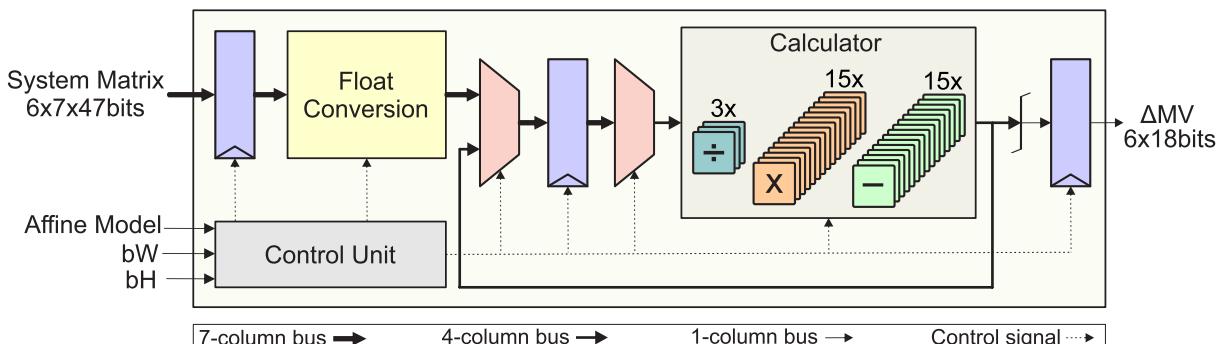

| Figure 30 | The Affine $\Delta MV$ Architecture. . . . .                            | 61 |

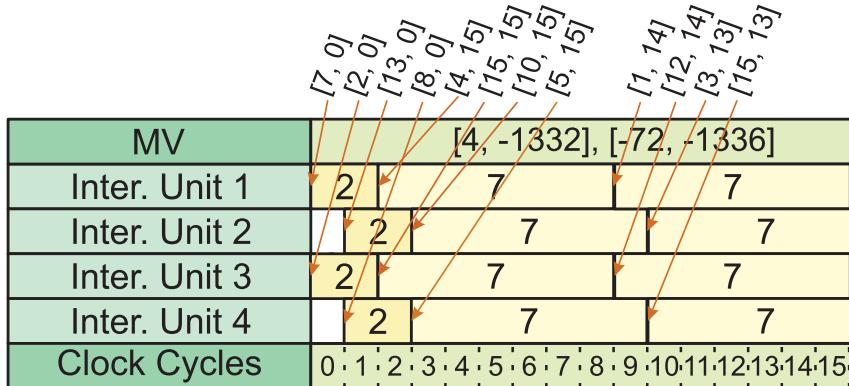

| Figure 31 | Time diagram of the proposed Affine $\Delta MV$ architecture. . . . .   | 62 |

## LIST OF TABLES

|          |                                                                                                                                                                             |    |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Table 1  | Affine Filter Coefficients . . . . .                                                                                                                                        | 27 |

| Table 2  | SLE of 6-parameters. . . . .                                                                                                                                                | 29 |

| Table 3  | SLE of 4-parameters. . . . .                                                                                                                                                | 30 |

| Table 4  | Results of the Affine Motion Estimation in the VVC for <b>four</b> Reference Frames. . . . .                                                                                | 37 |

| Table 5  | Average Processing of the Affine Motion Estimation divided by PU size for four Reference Frames. . . . .                                                                    | 38 |

| Table 6  | Results of the Affine Motion Estimation in the VVC for <b>one</b> Reference Frames. . . . .                                                                                 | 39 |

| Table 7  | Average Processing of the Affine Motion Estimation divided by PU size for <b>one</b> Reference Frames. . . . .                                                              | 40 |

| Table 8  | BD-Rate of the PU constraints evaluated. . . . .                                                                                                                            | 42 |

| Table 9  | BD-Rate of the Iteration constraints evaluated. . . . .                                                                                                                     | 42 |

| Table 10 | BD-Rate of the proposed combined constraints evaluated. . . . .                                                                                                             | 44 |

| Table 11 | Conversions Equations of the SLE 6-parameters to 4-parameters. . . . .                                                                                                      | 59 |

| Table 12 | Synthesis results for Interpolation Unit using <b>four</b> Filter Cores working at 808.7 MHz. . . . .                                                                       | 64 |

| Table 13 | Synthesis Results for the Affine MC for 4K@60fps while only processing GBIA and 16x16 PUs. . . . .                                                                          | 65 |

| Table 14 | Synthesis Results for the Gradient-Based Coefficient Generator for UHD 4K@60fps for both throughputs, GBIA and quadratic sizes (186MHz) and GBIA and 16x16 (48MHz). . . . . | 67 |

| Table 15 | Synthesis results of the Affine $\Delta MV$ architecture when targeting 4K UHD 60 fps videos . . . . .                                                                      | 69 |

| Table 16 | Comparison among the proposed Affine MC architecture and FPGA related works. . . . .                                                                                        | 70 |

| Table 17 | Comparison among the proposed Affine MC architecture and ASIC related works. . . . .                                                                                        | 71 |

| Table 18 | Comparison with related work for the Affine $\Delta MV$ architecture when targeting HD 1080p@60fps videos . . . . .                                                         | 71 |

## **LIST OF ABBREVIATIONS AND ACRONYMS**

|         |                                    |

|---------|------------------------------------|

| UHD     | Ultra-High Definition              |

| JVET    | Joint Video Experts Team           |

| VVC     | Versatile Video Coding             |

| SDR     | Standard Dynamic Range             |

| HDR     | High Dynamic Range                 |

| WCG     | Wide Color Gamut                   |

| ME      | Motion Estimation                  |

| CME     | Conventional Motion Estimation     |

| AME     | Affine Motion Estimation           |

| FPS     | Frames per Second                  |

| CU      | Coding Unit                        |

| MC      | Motion Compensation                |

| MV      | Motion Vectors                     |

| FME     | Fractional Motion Estimation       |

| VTM     | VVC Test Model                     |

| BD-Rate | Bjontegaard Delta Rate             |

| GBIA    | Gradient-Based Iterative Algorithm |

| BMIA    | Block Matching Iterative Algorithm |

| SLE     | System of Linear Equations         |

| VCEG    | Video Coding Experts Group         |

| MPEG    | Moving Picture Experts Group       |

| HEVC    | High Efficiency Video Coding       |

| NAL     | Network Abstraction Layer          |

| CTU     | Coding Tree Unit                   |

| PU      | Prediction Unit                    |

| RD      | Rate Distortion                    |

|      |                                              |

|------|----------------------------------------------|

| CPMV | Corner Point Motion Vectors                  |

| MM   | Merge Mode                                   |

| AMVP | Advanced Motion Vector Prediction            |

| AMC  | Affine Motion Compensation                   |

| SMV  | Subblock Motion Vectors                      |

| LT   | Left-Top                                     |

| RT   | Right-Top                                    |

| LB   | Left-Bottom                                  |

| PROF | Prediction Refinement with Optical Flow      |

| FPGA | Field-Programmable Gate Array                |

| ASIC | Application-Specific Integrated Circuit      |

| MCM  | Multiple Constant Multiplication             |

| CTC  | Common Test Conditions                       |

| QP   | Quantization Parameters                      |

| PE   | Power-Efficient                              |

| HE   | Hardware-Efficient                           |

| MMCM | Multiplexed Multiple Constant Multiplication |

| TSMC | Taiwan Semiconductor Manufacturing Company   |

| RTL  | Register-Transfer Level                      |

# CONTENTS

|                                                                                 |    |

|---------------------------------------------------------------------------------|----|

| <b>1 INTRODUCTION . . . . .</b>                                                 | 15 |

| <b>2 BACKGROUND . . . . .</b>                                                   | 18 |

| <b>2.1 Versatile Video Coding . . . . .</b>                                     | 18 |

| <b>2.2 Affine Motion Estimation . . . . .</b>                                   | 21 |

| <b>2.2.1 Interpolation Filters . . . . .</b>                                    | 24 |

| <b>2.2.2 Gradient-Based Iterative Algorithm . . . . .</b>                       | 26 |

| <b>2.2.3 Block Matching Iterative Algorithm . . . . .</b>                       | 31 |

| <b>2.3 Related Works . . . . .</b>                                              | 32 |

| <b>3 SOFTWARE EVALUATIONS . . . . .</b>                                         | 35 |

| <b>3.1 Experimental Setup . . . . .</b>                                         | 35 |

| <b>3.2 Hardware-Oriented Constraints Evaluation . . . . .</b>                   | 36 |

| <b>3.2.1 Results and BD-Rates of Reference Frames Constraints . . . . .</b>     | 36 |

| <b>3.2.2 BD-Rate of PU Size Constraints . . . . .</b>                           | 41 |

| <b>3.2.3 BD-Rate of Iteration Constraints . . . . .</b>                         | 42 |

| <b>3.2.4 BD-Rate of Proposed Approach for the AME Hardware Design . . . . .</b> | 43 |

| <b>3.3 Experiments Conclusions . . . . .</b>                                    | 44 |

| <b>4 PROPOSED AME HARDWARE ARCHITECTURES . . . . .</b>                          | 46 |

| <b>4.1 Affine MC . . . . .</b>                                                  | 46 |

| <b>4.1.1 Vector Generator . . . . .</b>                                         | 47 |

| <b>4.1.2 Interpolation Unit . . . . .</b>                                       | 47 |

| <b>4.1.3 Design Exploration of Filter Core . . . . .</b>                        | 48 |

| <b>4.1.4 Temporal Analysis . . . . .</b>                                        | 53 |

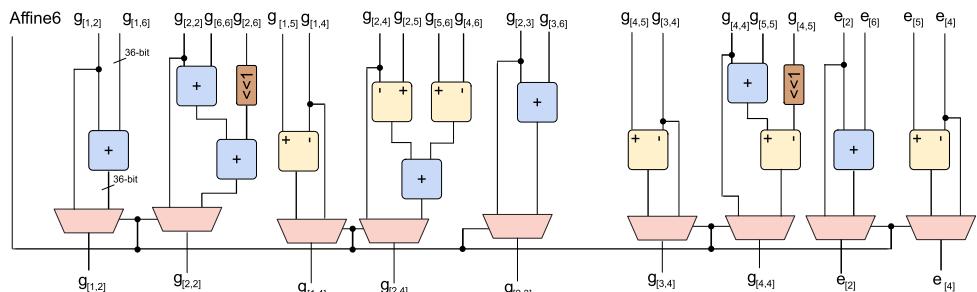

| <b>4.2 Gradient-Based Coefficient Generator Architecture . . . . .</b>          | 54 |

| <b>4.2.1 Row Buffer . . . . .</b>                                               | 54 |

| <b>4.2.2 Sobel Engine . . . . .</b>                                             | 55 |

| <b>4.2.3 Parameter Generator . . . . .</b>                                      | 56 |

| <b>4.2.4 Coefficient Generator . . . . .</b>                                    | 57 |

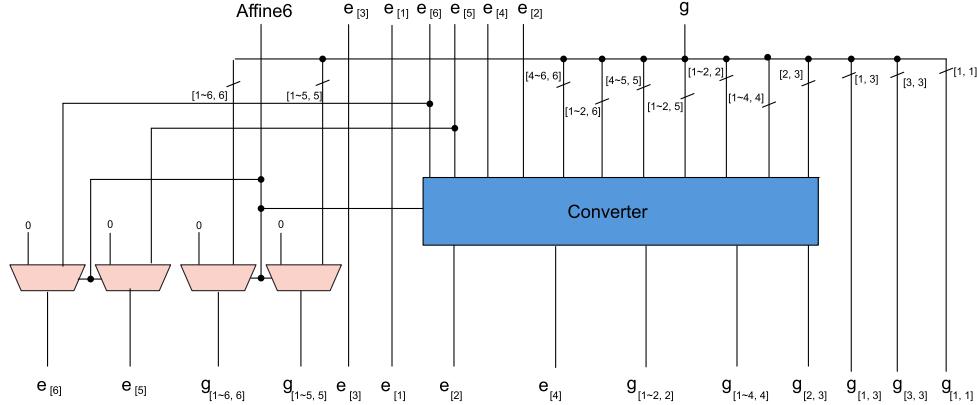

| <b>4.2.5 Affine Mode Adapter . . . . .</b>                                      | 58 |

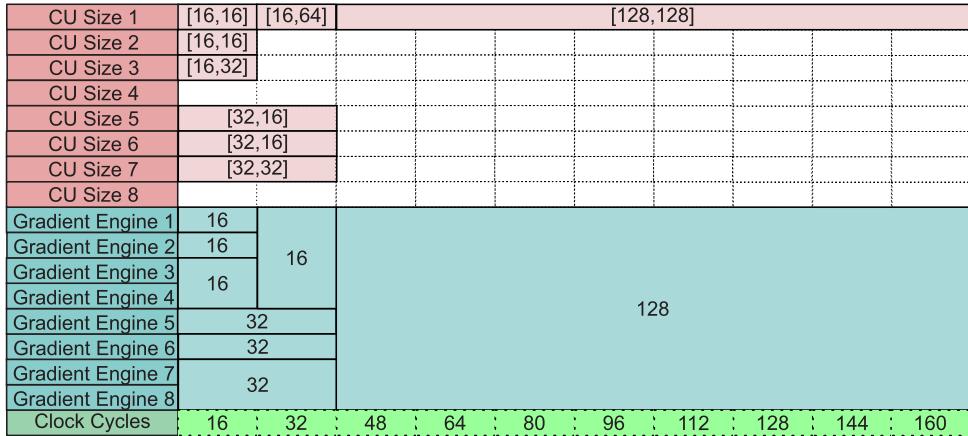

| <b>4.2.6 Temporal Analysis . . . . .</b>                                        | 59 |

| <b>4.3 Affine <math>\Delta MV</math> Architecture . . . . .</b>                 | 60 |

| <b>4.3.1 Gauss-Jordan Elimination Algorithm . . . . .</b>                       | 60 |

| <b>4.3.2 Proposed architecture . . . . .</b>                                    | 61 |

| <b>4.3.3 Temporal Analysis . . . . .</b>                                        | 62 |

|                                                                   |           |

|-------------------------------------------------------------------|-----------|

| <b>5 SYNTHESIS RESULTS AND COMPARISONS . . . . .</b>              | <b>63</b> |

| <b>5.1 Interpolation Unit Results . . . . .</b>                   | <b>63</b> |

| <b>5.2 Affine MC Synthesis Results . . . . .</b>                  | <b>65</b> |

| <b>5.3 Gradient-Based Coefficient Generator . . . . .</b>         | <b>66</b> |

| <b>5.4 Affine <math>\Delta MV</math> Architecture . . . . .</b>   | <b>68</b> |

| <b>5.5 Comparison with related works . . . . .</b>                | <b>69</b> |

| <b>6 CONCLUSION . . . . .</b>                                     | <b>72</b> |

| <b>REFERENCES . . . . .</b>                                       | <b>74</b> |

| <b>APPENDIX A LIST OF PUBLICATIONS DURING THIS MASTERS DEGREE</b> | <b>79</b> |

# 1 INTRODUCTION

The COVID-19 pandemic greatly impacted global internet traffic (bitmovin, 2020). With internet usage continuing to rise, it is estimated that in 2023, 5.3 billion people have had access to the internet (Cisco, 2018), an increase from 3.9 billion in 2018. As a result, data consumption on the internet has also been increasing year after year, with video streaming representing a significant portion of this data transfer volume. Data from the first half of 2021 shows that video streaming dominated internet bandwidth, accounting for 53% of the total data transfer volume (Sandvine, 2022). In addition to the growing demand, there is an increasing evolution in video resolutions and frame rates. Projections estimated that, in 2023, two-thirds (66%) of TVs were 4K UHD (Ultra-High Definition) resolution (Cisco, 2018). In this scenario, the need for greater efficiency in digital video compression becomes evident.

There is an ongoing effort within the scientific community to advance video compressors. In 2020, the Joint Video Experts Team (JVET) released the Versatile Video Coding (VVC) standard (Chen; Ye; Kim, 2021), which represents the state-of-the-art in video coding standards. VVC is the successor to High Efficiency Video Coding (HEVC) (Jct-vc, 2013), also developed by JVET. VVC was designed to efficiently encode 4K Ultra-High-Definition (UHD) with Standard Dynamic Range (SDR) and also encode 8K UHD or even larger resolutions, High Dynamic Range (HDR), and Wide Color Gamut (WCG).

The VVC was designed to reduce bit rate and be versatile by processing different types of content such as process screen content, gaming, and 360° video for immersive and augmented reality (Bross et al., 2021) In VVC, many tools were added to assist in video compression, enabling a 44.4% reduction in the amount of data required to represent videos (also known as bitrate) (Siqueira; Correa; Grellert, 2020), with a 5-fold increase in encoding complexity in terms of encoding time, compared to the HEVC (Pakdaman et al., 2020).

One of the tools of the VVC is inter-frame prediction, which uses a reference frame to predict the current frame samples. The Motion Estimation (ME) is a step inside the inter-frame prediction that determines the motion vectors between the reference frame

and the current frame being encoded. The ME is one of the most essential steps in video encoding because two frames that are temporally near each other may have a lot of redundancies. The ME is divided into Conventional ME (CME) and Affine ME (AME): CME uses one Motion Vector (MV) to describe translation motion, which is motion in which all points move in the same direction and distance. The AME uses two or three MV to represent more complex types of motion, such as rotation, zoom in/out, and shear.

Inter-frame prediction accounts for, on average, 59% of the total encoding time in the VVC standard (Gonçalves, 2021). Inter-frame prediction can be subdivided into unilateral, bilateral, and Affine predictions. Affine prediction has the highest computational cost, representing an average of 54.75% of the total inter-frame prediction time (Park; Kang, 2019). Since AME constitutes a significant portion of the total motion estimation processing time, reducing this complexity becomes crucial for real-time video encoding, especially for high resolutions like UHD 4K and 8K and high frame rates (FPS). Along with reducing complexity, it is also necessary for AME to have low energy consumption for applications on battery-powered mobile devices, making the use of dedicated hardware essential for encoding UHD videos under the H.266/VVC standard.

Only one work in the literature proposes dedicated hardware architecture for the entire AME process, which is (Taranto, 2022). However, it simplifies the algorithm, skipping many steps to reduce the overall computational complexity, which leads to visual degradation not being calculated in the work. Besides that, many works are proposing dedicated hardware architectures that can process one of the many steps of the AME: Sheng et al. (2024) propose solver for System of Linear Equations (SLE) for the Affine ME and Maass et al. (2023) propose an SLE solver and final processing to calculate the new set of MV. Perleberg et al. (2023) proposes a hardware architecture for the Prediction Refinement with Optical Flow (PROF) algorithm. The Affine MC can be compared to the Fraction Motion Estimation (FME) because of the filtering operations, and there are many works for the FME such as Azgin et al. (2018); Canmert; Kalali; Hamzaoglu (2018); Azgin; Kalali; Hamzaoglu (2020); Mahdavi; Azgin; Hamzaoglu (2021); Silva et al. (2021) even though choosing the filter uses Affine equations, which would require an additional calculation.

To understand the throughput necessary to process the AME, this work performed an analysis of the Affine ME done using the reference software of the VVC, the VVC Test Model (VTM). This analysis may also be used to understand how often the AME is processed inside the ME. With the results from the analysis, this work presents dedicated hardware architectures with the objective of processing steps inside the AME algorithm for the Affine 4-parameter and 6-parameter. These architectures were also designed to process any Prediction Unit (PU) size ranging from 16x16 to 128x128. In

addition, this work presents a design space exploration showing different approaches to designing these architectures for different target throughput and area/power constraints.

The main contributions of this Master's dissertation work:

- An analysis of the AME algorithm. This analysis shows the Bjontegaard Delta Rate (BD-Rate) of different constraints, the number of times the AME 4-parameter and 6-parameter are processed, the number of times Gradient-Based Iteration Algorithm (GBIA) and Block-Matching Iterative Algorithm (BMIA) are processed, and these values for each PU size.

- The development of energy-efficient hardware designs for the AME of the VVC encoding standard. These architectures were developed to process all PU sizes supported in VVC AME. These architectures can process 4K Ultra High-Definition (UHD) videos at 60 frames per second.

This work presents three hardware architectures for the Affine ME. The first architecture presented is the Affine MC, which is used by both GBIA and BMIA. The synthesis of this architecture presents an area utilization of 189.2k gates with a power dissipation of 121.15mW with a frequency of 598MHz for processing UHD 4K@60fps. The second architecture presented is the Gradient-Based Coefficient Generator. The synthesis of this architecture presents an area utilization of 4849k gates with a power dissipation of 3932mW with a frequency of 48MHz for processing 4K@60fps. The results are prohibitive for real applications; however, the Gradient-Based Coefficient Generator is the first architecture for this step of the iterative algorithm in the literature. The last architecture presented is the Affine  $\Delta MV$  architecture, which solves the SLE generated by the Gradient-Based Coefficient Generator and generates the Affine  $\Delta MV$ , which is added to the current MV being evaluated, generating the next set of MVs to be evaluated. The synthesis of this architecture presented an area of 262k gates and 74.95mW of power dissipation.

This dissertation is organized as follows: The chapter 2 explains basic concepts of the VVC video coding standard, the AME algorithm, which is the focus of this work, and presents the related works. After, chapter 3 presents the evaluations performed to define the throughput of the developed architectures, while chapter 4 shows in detail the developed architectures. In chapter 5, the obtained syntheses are presented and compared with relevant related works. Finally, the chapter 6 concludes this work.

## 2 BACKGROUND

In this chapter, some background information necessary to understand this dissertation will be presented. Section 2.1 presents the Versatile Video Coding (VVC) and the basic information on how it encodes a video. Section 2.2 presents the AME algorithm, which is a new tool added in VVC and the focus of this work. Section 2.3 discusses the related works, presenting all published hardware architectures that will be compared to the synthesis results achieved in this work.

### 2.1 Versatile Video Coding

The VVC standard (Chen; Ye; Kim, 2021) is the state-of-the-art video compressor. The VVC was developed by the Joint Video Experts Team (JVET), which was formed by the Video Coding Experts Group (VCEG) and the Moving Picture Experts Group (MPEG). JVET issued a call for proposals in October 2017, and the first draft of the VVC was released in April 2018, with the completion of the standard in July 2020 (Jvet, 2018).

The VVC is the successor of the H.265/High Efficiency Video Coding (HEVC) (Jctvc, 2013), and it has an improvement of 50% of bitrate reduction over its predecessor (Bross et al., 2021). The standard is named Versatile because it covers current and emerging media needs:

- Higher resolutions than its predecessor (up to 8K or larger), HDR and WCG.

- Computer-generated or screen content, as occurs in screen sharing and gaming.

- 360° video for immersive and augmented reality.

- Applications requiring ultralow delay, such as wireless displays and online gaming.

The VVC, similar to its predecessor, the HEVC, uses a block-based hybrid video coding scheme and the bitstream structure based on the network abstraction layer (NAL), and the basic processing unit is the Coding Tree Unit (CTU).

The VVC uses the same block-based partitioning scheme as its predecessor. The encoder divides the frame into Coding Tree Units (CTU). The CTU in VVC has a size of 128x128, which is the largest Coding Unit (CU) supported. Each CTU is then further divided into one or more blocks known as CU of varying sizes, and the CU is the basic processing unit of the encoder. Finally, the CU is divided into Prediction Units (PU), the units evaluated in the prediction steps of the video encoders, such as Inter-Frame or Intra-Frame prediction. The PU was chosen by evaluating its rate-distortion (RD) cost. The encoder selects the PU with the smallest RD cost because a smaller RD cost leads to fewer bits needed in the bitstream.

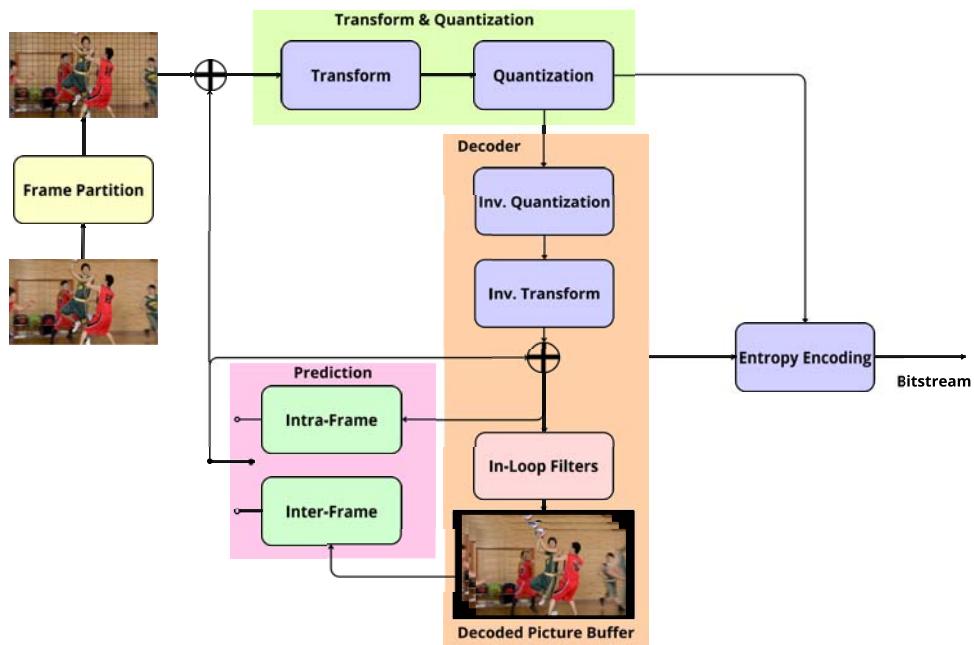

After the frame is split into PU, the VVC encoder uses the encoding steps of its predecessor, the core design of video data compression can be seen in Figure 1 and has five stages: prediction, transform, quantization, in-loop filters, and entropy encoding. The prediction stage can be divided into two: intra-frame prediction, which uses the similarities of the current frame to encode it, and inter-frame prediction, which searches for similarities in previously encoded frames. The transform stage changes the values to the frequency domain. In a lossy stage, the data in the frequency domain gets quantized to reduce information irrelevant to human visual perception. Finally, in the entropy encoding stage, the statistical redundancies are reduced by an entropy encoder applying arithmetic coding.

The Motion Estimation (ME) is a step inside the inter-frame prediction used to describe the motion from two frames, a reference frame and the current frame being encoded. The ME is one of the most essential steps in video encoding because two frames that are temporally near each other may have a lot of redundancies. The ME

Figure 1 – Flowchart of the video compression

is divided into Conventional ME (CME) and Affine ME (AME): CME uses one Motion Vector (MV) to describe translation motion, which is motion in which all points move in the same direction and distance. The AME uses two or three MV to describe more complex types of motion, such as rotation, zoom in/out, and shear.

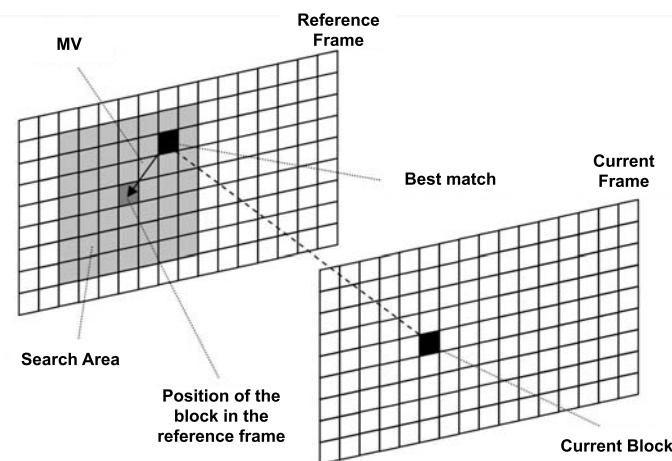

The Figure 2 presents the ME process. The ME searches for the best match for the current block in the reference frame; this search is not performed in all of the positions in the reference frame but only in a search area around the position of the block in the reference frame. A MV describes the motion between the block position in the current frame and the best match. This best match has its cost calculated and compared with the best matches found in the other reference frames.

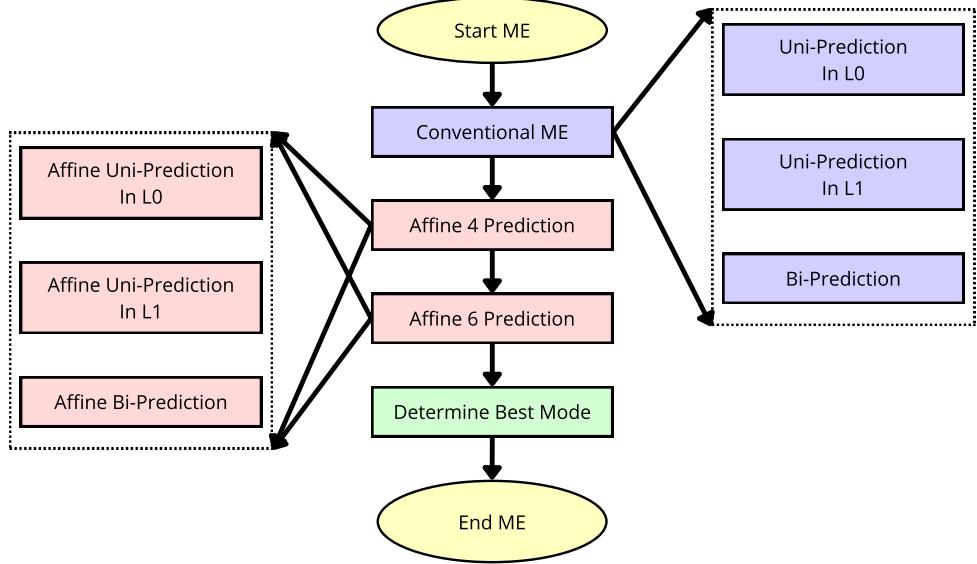

The inter-frame prediction exploits similarities of the frames temporally close to reduce massively the data transferred. The process of finding a match in a reference frame in the inter-frame prediction is called ME. The ME process can be seen in Figure 3. The process applies different types of prediction in succession, however, it can be skipped early depending on the cost calculated. The ME divides the frames into two lists ( $L_0, L_1$ ), one for frames in the past and another for frames in the future then the prediction modes are tested. With the two lists of frames, two types of prediction modes are supported: unilateral and bilateral. Uni-lateral prediction searches the frames in  $L_0$  or  $L_1$  for the best match to encode the PU. The bi-lateral prediction mode uses two frames to encode the PU, using both lists  $L_0$  and  $L_1$ . These prediction modes can be further split into two types of prediction modes: Conventional and Affine. Conventional ME describes translation motion between two frames, that is, motion in which all points have the same direction. The Affine Motion Estimation is a new tool added to the VVC that uses multiple MVs to better encode more complex motions such as rotation and zoom. The Affine Motion Estimation has two different modes, which use two MVs (4-parameters) or three MVs (6-parameters) to describe the motion. Both Conventional ME and Affine ME support uni-lateral and bi-lateral modes.

Figure 2 – Elements present in the ME (Porto, 2012)

Figure 3 – Search process of the ME

The AME can describe more complex motion, leading to reduced error, reducing the bits necessary for transmission, and increasing visual fidelity. However, this reduced bandwidth/size and better visual fidelity have a higher computational complexity cost than Conventional ME.

The many new tools added to VVC enable the gain in coding efficiency. This work focuses on AME, one of the new tools added to the Inter-frame prediction.

## 2.2 Affine Motion Estimation

The Affine Motion Estimation (AME) is a new tool adopted in ME of VVC. The AME is used in inter-frame prediction to identify and represent more complex movements than the traditional translational movement, such as scaling, rotation, and skewing (Bross et al., 2021). As in ME, the AME performs a search for a similar block in a reference frame previously encoded, resulting in a set of two or three MVs that will be used to represent the current block with a non-translational movement (Chen; Ye; Kim, 2021).

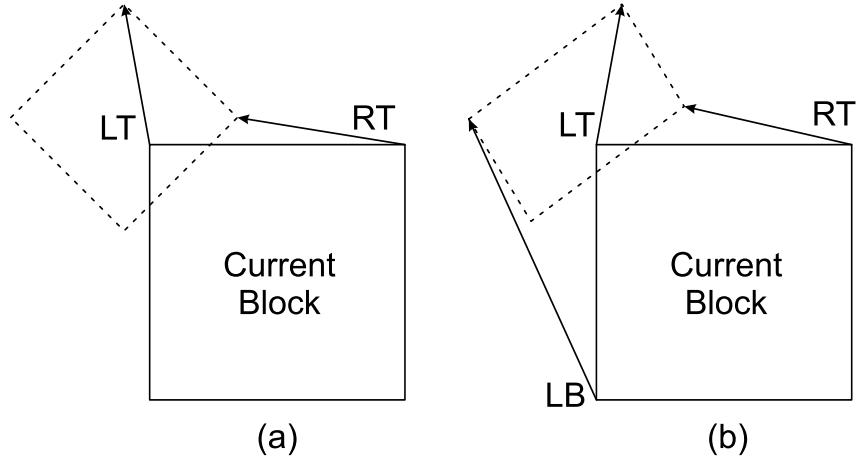

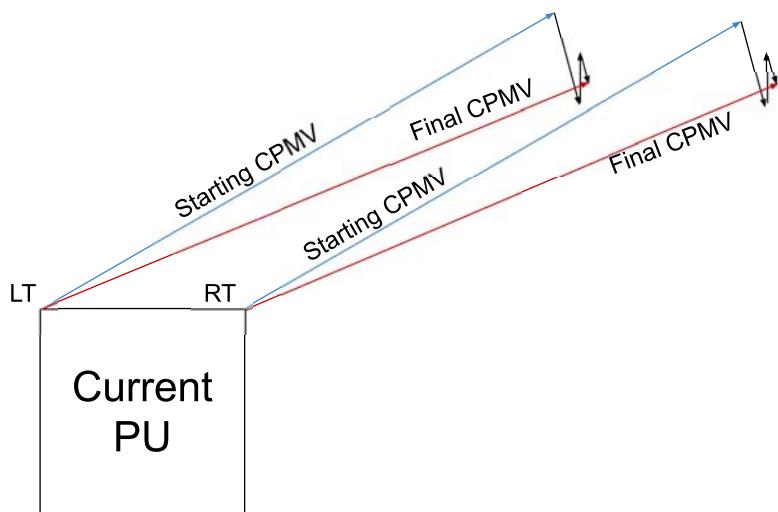

The VVC AME supports two Affine models, with 4 or 6 parameters (Bross et al., 2020), as presented in Figure 4 (a) and (b). The 4-parameter model uses Corner Point Motion Vectors (CPMVs) in the top-right corner and the top-left corner of the PU, while the 6-parameter uses the three CPMVs in the top-left, bottom-left, and top-right corner of the PU as can be seen in Figure 4 (Bross et al., 2020). The AME is applied over 12 Prediction Unit (PU) sizes ranging from 16x16 to 128x128 (Bross et al., 2020).

The Affine MVs can be obtained in two ways: Affine Merge Mode and Affine Advanced Motion Vector Prediction (AMVP) (Chen; Ye; Kim, 2021). Affine Merge Mode inherits the MV from the neighboring PUs that were used to encode either the AME or

Figure 4 – Affine models. (a) 4-Parameter with LT and RT MVs. (b) 6-Parameter with LT, RT, and LB MVs.

ME. Affine AMVP is an iterative algorithm that minimizes the error in the starting MVs of a block, and this algorithm may motion compensate the block up to 82 times, leading to high complexity.

The Affine Merge Mode (MM) requires very few CPMVs to be evaluated. The list of candidate CPMVs that need to be evaluated is formed by using CPMVs from the Affine MM of neighboring PUs, candidates constructed CPMVs that are derived from the CME of neighboring PUs, and Zero MVs. This list has a maximum size of five CPMVs that are required to be evaluated. This algorithm has a very low complexity compared to Affine AMVP, but it may have a higher error, which leads to reduced encoding efficiency.

The Affine AMVP algorithm evaluates only two candidates: the first uses two CPMVs (Affine 4-parameter), and the second uses three CPMVs (Affine 6-parameter). Even though the list of candidates is smaller, it uses a more complex algorithm to minimize the error and find the best CPMVs. This algorithm is divided into two steps: A Gradient-Based Iterative Algorithm (GBIA) and a Block Matching Iterative Algorithm (BMIA). Affine AMVP candidate list of two CPMVs requires higher computational complexity than Affine Merge Mode, with up to 82 CPMVs needing to be evaluated. Also, this does not consider the steps necessary to generate a new set of MVs, which has a high computational complexity and requires a lot of memory access.

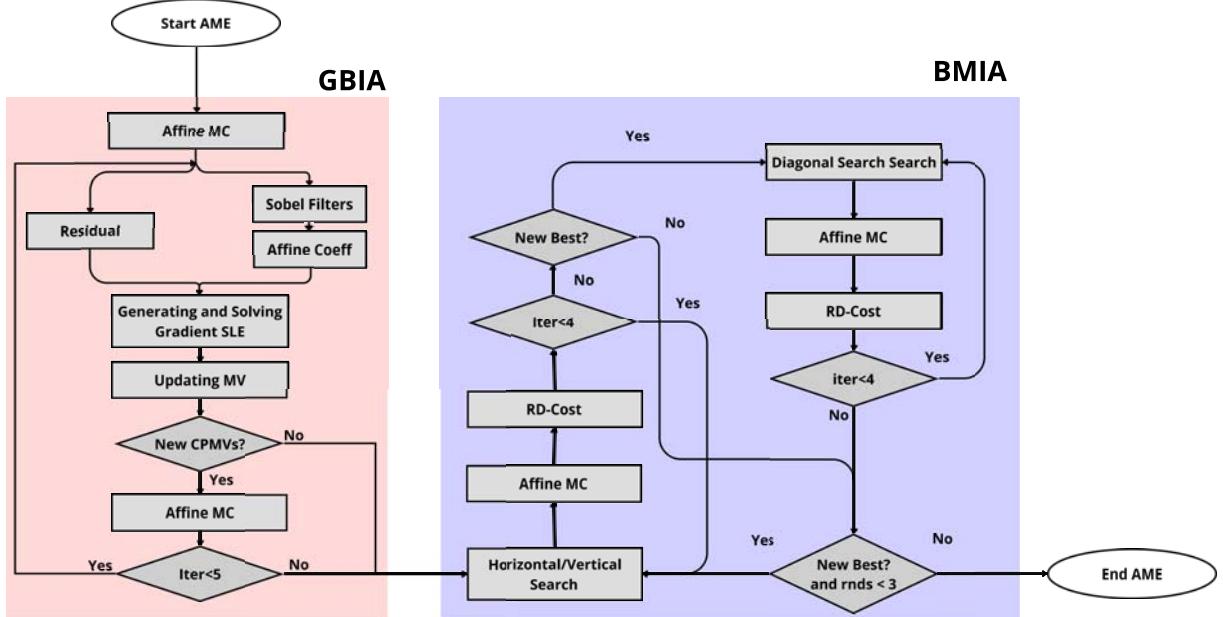

As can be seen in Figure 5, both iterative algorithms in the AMVP require Affine Motion Compensation (MC) of the PU with the starting CPMVs. In each iteration of the algorithms, the CPMVs are updated, either through the use of the error, in the case of the GBIA, or through searching neighboring positions, in the case of the BMIA. The GBIA can repeated up to five times, while the BMIA can be up to 24 times per CPMV (up to 48 times for Affine 4-parameter or 72 for Affine 6-parameter). The AMVP also contains five additional Affine MCs between GBIA and BMIA, one for each CPMV, one to keep rotation/zoom, and one to keep translation (Chen; Ye; Kim, 2021).

The Gradient-Based Iterative Algorithm (GBIA), as can be seen in Figure 5, first

Figure 5 – Affine AMVP Algorithm.

performs the Affine MC the PU with the starting CPMVs, then uses Sobel Filters to calculate four or six Affine parameters depending on the model. These Affine parameters and the residual (error between the predicted and original samples) are then used to generate a System of Linear Equations (SLE) based on the gradient, and this SLE has a size of  $4 \times 5$  or  $6 \times 7$ . This SLE, when solved, generates 4 or 6  $\Delta MV$ , one for each CPMV, depending on the Affine model, which is added to the respective CPMV, generating a new set of CPMVs that are evaluated in the next iteration. This repeats as long as at least one CPMV is updated or up to five times (Chen; Ye; Kim, 2021). After the GBIA, there are five motion compensations: one for each CPMV up to three, one to keep rotation/zoom, and another to keep translation.

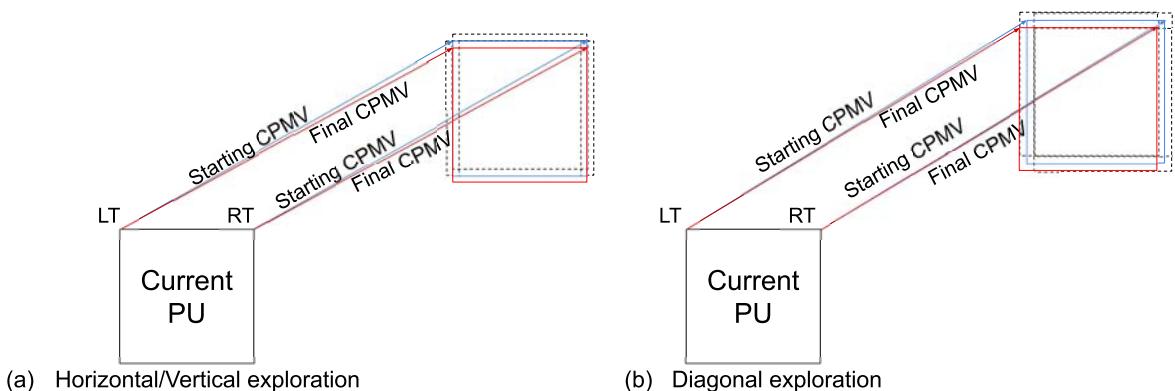

Following the GBIA, the Block Matching Iterative Algorithm (BMIA) is used, as seen in Figure 5. The BMIA contains up to 24 Affine MC for each CPMV. First, there is a horizontal/vertical search of the nearest neighbors. If any neighbor leads to a lower cost, the current CPMV is updated as the new starting CPMV. After the last step, a search is performed in the diagonal neighbors, and the CPMV is updated if any have a lower cost. The horizontal/vertical search, followed by the diagonal search, is repeated three times. The diagonal search is only performed if a better MV is found in the horizontal/vertical search, and the horizontal/vertical is repeated up to three times, as long a better CPMV is found (Chen; Ye; Kim, 2021).

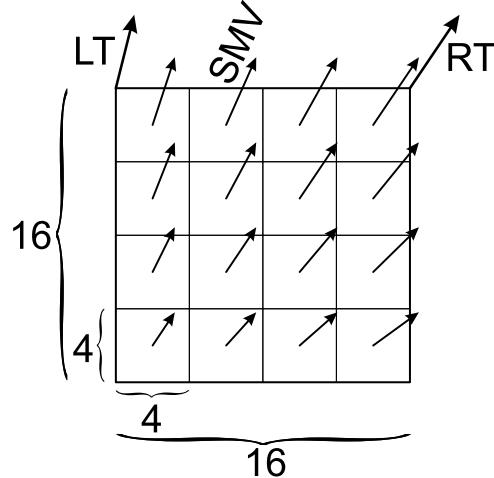

Evaluating each set of MVs requires an Affine Motion Compensation (AMC) to reconstruct the current Prediction Unit (PU) with the samples related to the set of CPMVs (Chen; Ye; Kim, 2021). In the AMC of VVC, the PU is split into subblocks of  $4 \times 4$  samples, and each subblock passes by an individual  $4 \times 4$  MC, similar to the conventional ME (Chen; Ye; Kim, 2021; Bross et al., 2020). This split may be seen in Figure 6,

Figure 6 – Affine representation of the subblock split, where 16 subblocks with 4x4 samples compose one 16x16 PU. Each subblock has its own SMV.

where 16 subblocks of 4x4 samples are used to compose a 16x16 PU. The difference in the AMC is that each subblock receives a Subblock Motion Vector (SMV) that is obtained using the Affine equations defined in 1 and 2, according to the Affine model of 4-parameter or 6-parameter, respectively (Bross et al., 2020).

$$\begin{cases} SMV^H = \frac{RT^H - LT^H}{bW} cx + \frac{RT^V - LT^V}{bW} cy + LT^H \\ SMV^V = \frac{RT^V - LT^V}{bW} cx + \frac{RT^H - LT^H}{bW} cy + LT^V \end{cases} \quad (1)$$

$$\begin{cases} SMV^H = \frac{RT^H - LT^H}{bW} cx + \frac{LB^H - LT^H}{bH} cy + LT^H \\ SMV^V = \frac{RT^V - LT^V}{bW} cx + \frac{LB^V - LT^V}{bH} cy + LT^V \end{cases} \quad (2)$$

In (1) and (2), the  $LT$ ,  $RT$ , and  $LB$  are the Left-Top, Right-Top, and Left-Bottom CPMVs inherited from the PU, where the  $H$  and  $V$  represent the horizontal and vertical parts of those CPMVs. The  $cx$  and  $cy$  are the positions of the center of the subblock, while the  $bW$  and  $bH$  represent, respectively, the width and height of the PU. The output is the horizontal and vertical parts of the SMV, which are used for the MC of each 4x4 subblock.

These SMVs generated using the equation may have a motion that does not align with the samples of the reference frame or a position between samples, making it necessary to interpolate fractional samples. The VVC has a precision of 1/16 (Bross et al., 2021), which means that up to 15 different samples can be interpolated between two samples depending on SMV. These fractional samples are interpolated using filters.

### 2.2.1 Interpolation Filters

In digital videos, the motion that occurs between adjacent frames may not align in integer sample positions, resulting in SMVs having fractional parts. Therefore, VVC requires a Motion Compensation (MC) with 1/16 sample interpolation to interpolate the

4x4 subblock in the fractional positions (Sullivan et al., 2012; Bross et al., 2020).

To reach an MC with 1/16 sample interpolation, the VVC adopts a set of 15 interpolation filters (Bross et al., 2020, 2021). Therefore, between two horizontally neighbor samples, 15 horizontal samples may be interpolated. The horizontal interpolation occurs when the component  $SMV^V$  is equal to zero. In the same way, between two vertically neighbor integer samples, 15 new vertical fractional samples can be generated, which occurs when the component  $SMV^H$  is equal to zero. Besides, when both  $SMV^H$  and  $SMV^V$  are different from zero, the diagonal interpolation process can generate up to 225 diagonal fractional samples. To do this diagonal interpolation, it is required first to interpolate the horizontal fractional samples, and then the fractional samples can be used as input in vertical interpolation (Afonso et al., 2016).

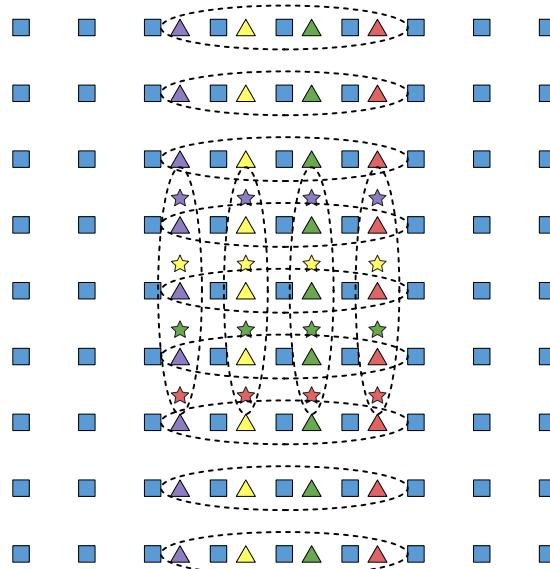

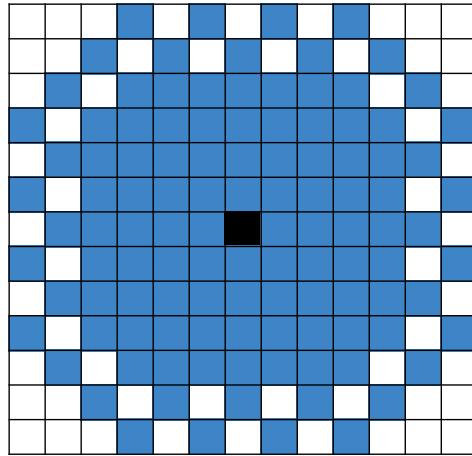

Figure 7 presents the interpolation of fractional samples to reconstruct a 4x4 subblock for a diagonal SMV (when X and Y are different from zero). The blue squares represent the integer samples, and the colored stars represent the samples of the 4x4 subblock to be interpolated, with the triangles being the temporary samples required for the interpolation. Nine horizontal neighboring squared samples are used to interpolate the four triangle temporary samples for each line (colored triangles inside the horizontal ellipses). Then, the colored star samples are interpolated using a similar process. However, using temporary triangle neighboring samples, this process is performed for each of the four columns to generate the diagonal samples (colored stars inside the vertical ellipses). Finally, after processing nine lines and four columns, a 4x4 subblock can be obtained.

The AME adopted 6-tap filters during the interpolation process. Therefore, to interpolate one fractional sample, six input samples are necessary. The interpolation

Figure 7 – Representation of diagonal interpolation of a 4x4 subblock. The blue squares are the integers, the triangles are horizontal, and the stars are diagonal samples.

process involves passing the input samples by a weighted average process, adopting different coefficients. The complete processing to interpolate one sample  $F_n$  can be seen in (3), where the six input samples are given by  $A_x$ , while the six coefficients are given by  $C_x$ . Also, besides the weighted sum of entries, offset and shift operations are performed (Chen; Ye; Kim, 2021). These operations are due to rounding properties and were performed to keep sample precision when consecutive interpolations.

$$F_n = (C_0A_{-2} + C_1A_{-1} + C_2A_0 + C_3A_1 + C_4A_2 + C_5A_3 + \text{offset}) >> \text{shift} \quad (3)$$

The fractional sample  $F_n$  is obtained by giving more weight to the input samples closer to the sample to be interpolated. In addition, the value varies according to the distance between the input and fractional samples (Chen; Ye; Kim, 2021). The Equation (4) represents an example of the use of Equation (3) for the interpolation filter  $F_8$ , which interpolates a sample in 1/2 position. Table 1 shows the coefficients for the  $F_1$  to  $F_{15}$  filters. Note that the  $F_9$  to  $F_{15}$  coefficients are symmetric to the  $F_1$  to  $F_7$  coefficients. The  $F_{15}$  filter uses the same coefficients as the  $F_1$  filter but inverts the input samples order. The same occurs between the  $F_2$  and  $F_{14}$  filters, and so on.

$$F_8 = (3A_{-2} - 11A_{-1} + 40A_0 + 40A_1 - 11A_2 + 3A_3 + 32) >> 6 \quad (4)$$

Also can be seen in Table 1 the sum of the weights of each row of the filter table is equal to 64, which is used to give more weight to a sample. This is also used to calculate the shift and offset values in Equation (3). The shift value is used to divide the final sample interpolated by the row's total weight, so a division by 64 is the same as shifting by 6, and the offset value is equal to half the weight, so 32. For diagonal samples, the values of the offset and shift are not so simple to understand. However, the idea is to return the sample value to an 8-bit sample after the process. In the first interpolation, the shift value is 0, and the offset is -8192. For the second diagonal interpolation, the shift value is 12, and the offset is 526336. Both these values are generated by shifting internal precision values of the VVC.

### 2.2.2 Gradient-Based Iterative Algorithm

This section presents the Gradient-Based Iterative Algorithm (GBIA). Figure 8 presents the visual representation of the GBIA. As can be seen in Figure 8, GBIA starts with a set of CPMVs and generates a new set of CPMVs each iteration (up to five times) using a gradient-based algorithm which will be explained in this section, ending with a final set of CPMVs which have lower error and better encoding efficiency.

The Affine MC with the starting CPMVs will, most of the time, not generate the best block. To find the best block, VVC uses an algorithm based on gradient descent to min-

Table 1 – Affine Filter Coefficients.

|          | $C_0$ | $C_1$ | $C_2$ | $C_3$ | $C_4$ | $C_5$ |

|----------|-------|-------|-------|-------|-------|-------|

| $F_1$    | 1     | -3    | 63    | 4     | -2    | 1     |

| $F_2$    | 1     | -5    | 62    | 8     | -3    | 1     |

| $F_3$    | 2     | -8    | 60    | 13    | -4    | 1     |

| $F_4$    | 3     | -10   | 58    | 17    | -5    | 1     |

| $F_5$    | 3     | -11   | 52    | 26    | -8    | 2     |

| $F_6$    | 2     | -9    | 47    | 31    | -10   | 3     |

| $F_7$    | 3     | -11   | 45    | 34    | -10   | 3     |

| $F_8$    | 3     | -11   | 40    | 40    | -11   | 3     |

| $F_9$    | 3     | -10   | 34    | 45    | -11   | 3     |

| $F_{10}$ | 3     | -10   | 31    | 47    | -9    | 2     |

| $F_{11}$ | 2     | -8    | 26    | 52    | -11   | 3     |

| $F_{12}$ | 1     | -5    | 17    | 58    | -10   | 3     |

| $F_{13}$ | 1     | -4    | 13    | 60    | -8    | 2     |

| $F_{14}$ | 1     | -3    | 8     | 62    | -5    | 1     |

| $F_{15}$ | 1     | -2    | 4     | 63    | -3    | 1     |

imize the error. This is an iterative algorithm that may be processed up to five times or until the generated CPMVs are the same as the previous iteration. The algorithm used in VVC utilizes kernel convolutions with Sobel Filters, which are utilized to generate Affine parameters. These Affine parameters are multiplied by themselves to generate an SLE that generates the  $\Delta MV$ , which will be added to the current CPMVs.

Figure 9 presents the Sobel Filter in the X-direction and Y-direction, which are used in image processing for edge detection. This type of operation is called a kernel convolution. It is a process of adding each image element to its local neighbors multiplied by

Figure 8 – Representation of the Gradient-Based Iterative Algorithm.

| X-direction |  |    | Y-direction |    |    |

|-------------|--|----|-------------|----|----|

| -1          |  | +1 | -1          | -2 | -1 |

| -2          |  | +2 |             |    |    |

| -1          |  | +1 | +1          | +2 | +1 |

Figure 9 – The kernel Sobel Filter in the X- and Y-direction.

the filter value in that location. The Sobel Filters are not applied to the first and last row, as well as the first and last column, because the Sobel value utilizes samples around the target interpolated Sobel value. The first row is a copy of the second; the last row is a copy of the last but one; the first column is a copy of the second column, and the last column is a copy of the last but one. The Sobel filters are used to calculate the Affine coefficients. These Affine coefficients are different depending on the Affine prediction model being utilized.

The coefficients of the Affine 6-parameter prediction model can be seen in Equation (5). The SobelH and SobelV are the Sobel in X- and Y-directions, respectively. The  $cx$  and  $cy$  are the centers of the 4x4 subblock current being processed; this is calculated using the equation  $cy = ((j \gg 2) \ll 2) + 2$  and  $cx = ((i \gg 2) \ll 2) + 2$  where  $i$  and  $j$  are the vertical and horizontal position of the subblock inside the PU, these values may range from 2 to 126.

$$\begin{bmatrix} iC_0 \\ iC_1 \\ iC_2 \\ iC_3 \\ iC_4 \\ iC_5 \end{bmatrix} = \begin{bmatrix} \text{SobelH} \\ cx * \text{SobelH} \\ \text{SobelV} \\ cx * \text{SobelV} \\ cy * \text{SobelH} \\ cy * \text{SobelV} \end{bmatrix} \quad (5)$$

The coefficients of the Affine 4-parameter prediction model can be seen in Equation (6), and they can be seen as adding and subtracting the Affine 6-parameter coefficients. The  $iC_1$  of Affine 4-parameter is Affine 6-parameter  $iC_1$  added to  $iC_5$  and The  $iC_3$  of Affine 4-parameter is Affine 6-parameter  $iC_4$  subtracted from  $iC_3$ .

$$\begin{bmatrix} iC_0 \\ iC_1 \\ iC_2 \\ iC_3 \end{bmatrix} = \begin{bmatrix} \text{SobelH} \\ cx * \text{SobelH} + cy * \text{SobelV} \\ \text{SobelV} \\ cy * \text{SobelH} - cx * \text{SobelV} \end{bmatrix} \quad (6)$$

The Affine coefficients are multiplied by each other, as seen in Equation (7). This is performed over the whole PU. The  $bH$  and  $bW$  are the PU height and width; The row and col choose the Affine coefficient and range from 0 to 5 if it is the 6-parameter mode or 0 to 3 if it is the 4-parameter model; the  $i$  and  $j$  are the current samples being processed in the PU, which ranges from 0 to  $bH - 1$  for  $i$  and 0 to  $bW - 1$  for  $j$ . These values are added up for the whole PU.

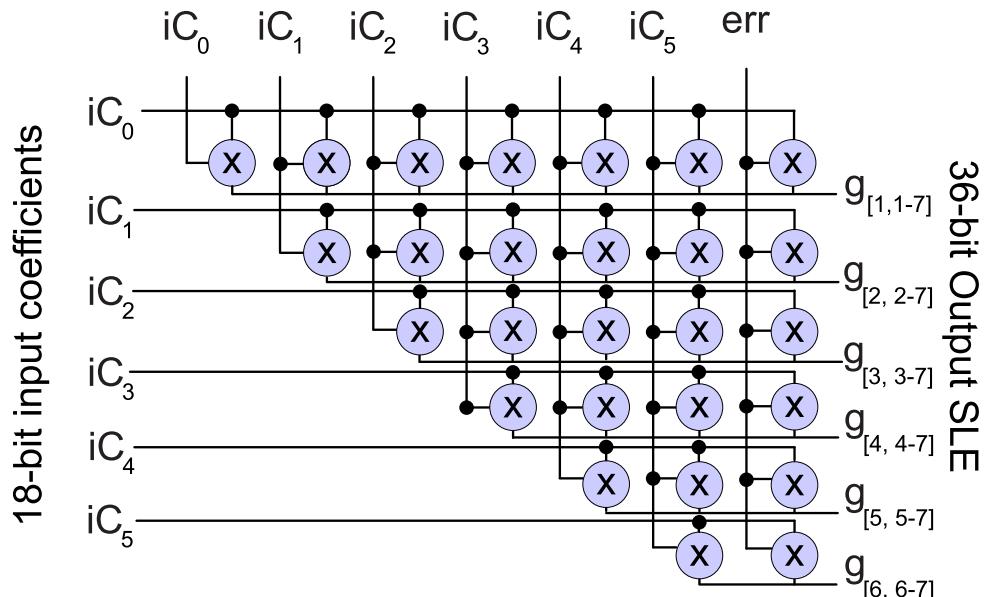

$$g_{[\text{row},\text{col}]} = \sum_{i=1}^{bH} \sum_{j=1}^{bW} iC_{\text{row}}[i][j] \times iC_{\text{col}}[i][j] \quad (7)$$

Table 2 shows the matrix resulting from the Equation (7) for the Affine 6-parameter prediction model where  $h$  and  $v$  are the horizontal and vertical Sobels.  $hx$  and  $vx$  are the horizontal and vertical Sobels multiplied by the position of the center of the subblock in x.  $hy$  and  $vy$  are the horizontal and vertical Sobel multiplied by the position of the center of the subblock in y. Table 3 presents the resulting matrix of the Equation (7) for the Affine 4-parameter prediction mode. The values in Table 2 can be manipulated algebraically to output the values in Table 3.

There is an additional column generated by multiplying the error by the Affine coefficients, as can be seen in Equation (8).

$$e_{[\text{row}]} = \sum_{i=1}^{bH} \sum_{j=1}^{bW} (iC_n[\text{row}] \times \text{error}[i,j]) \ll 3 \quad (8)$$

The error utilized is calculated using the original samples minus the predicted samples, as can be seen in Equation (9), where  $O$  is the original samples and  $P$  is the predicted samples.

Table 2 – SLE of 6-parameters.

|      | $h$   | $hx$         | $v$          | $vx$          | $hy$          | $vy$          |

|------|-------|--------------|--------------|---------------|---------------|---------------|

| $h$  | $h^2$ | $h \cdot hx$ | $h \cdot v$  | $h \cdot vx$  | $h \cdot hy$  | $h \cdot vy$  |

| $hx$ |       | $hx^2$       | $hx \cdot v$ | $hx \cdot vx$ | $hx \cdot hy$ | $hx \cdot vy$ |

| $v$  |       |              | $v^2$        | $v \cdot vx$  | $v \cdot hy$  | $v \cdot vy$  |

| $vx$ |       |              |              | $vx^2$        | $vx \cdot hy$ | $vx \cdot vy$ |

| $hy$ |       |              |              |               | $hy^2$        | $hy \cdot vy$ |

| $vy$ |       |              |              |               |               | $vy^2$        |

Table 3 – SLE of 4-parameters.

|           | $h$   | $hx + vy$                           | $v$                       | $hy - vx$                                               |

|-----------|-------|-------------------------------------|---------------------------|---------------------------------------------------------|

| $h$       | $h^2$ | $h \cdot hx + h \cdot vy$           | $h \cdot v$               | $h \cdot hy - h \cdot vx$                               |

| $hx + vy$ |       | $hx^2 + 2 \cdot hx \cdot vy + vy^2$ | $hx \cdot v + v \cdot vy$ | $hx \cdot hy - hx \cdot vx + vy \cdot hy - vy \cdot vx$ |

| $v$       |       |                                     | $v^2$                     | $v \cdot hy - v \cdot vx$                               |

| $hy - vx$ |       |                                     |                           | $hy^2 - 2 \cdot hy \cdot vx + vx^2$                     |

$$\text{error}[i][j] = O[i][j] - P[i][j] \quad (9)$$

The coefficient matrix and the error column are joined, as in Equation (10). This System of Linear Equation (SLE) can be 4x5 or 6x7, depending on the Affine prediction model being calculated. After solving this SLE, 4 or 6 Affine parameters are generated, one for each row.

$$\left[ \begin{array}{cccc|c} g_{[1,1]} & g_{[1,2]} & \cdots & g_{[1,n]} & e_{[1]} \\ g_{[2,1]} & g_{[2,2]} & \cdots & g_{[2,n]} & e_{[2]} \\ \vdots & \vdots & \ddots & \vdots & \vdots \\ g_{[n,1]} & g_{[n,2]} & \cdots & g_{[n,n]} & e_{[n]} \end{array} \right] \quad (10)$$

The four or six values of the solution to the SLE are the Affine parameters that go through a final step in which the new CPMVs are generated. The equations (11), (12), and (13) present this final step. The  $\text{AffineP}$  is one of the four or six Affine parameters,  $bW$  and  $bH$  are the PU width and height,  $\Delta MV$ . These values are clipped to 14 bits (8.191 to -8.192).

The Equation (11) presents the  $\Delta MV$ , which are common for both prediction models.

$$\begin{bmatrix} \delta MV_0 \\ \delta MV_2 \end{bmatrix} = \begin{bmatrix} \text{AffineP}_0 \\ \text{AffineP}_2 \end{bmatrix} \quad (11)$$

The Equation (12) presents the  $\Delta MV$ , which is used in the Affine 4-parameter prediction model that uses two CPMVs.

$$\begin{bmatrix} \delta MV_1 \\ \delta MV_3 \end{bmatrix} = \begin{bmatrix} \text{AffineP}_1 \times bW + \text{AffineP}_0 \\ -\text{AffineP}_3 \times bW + \text{AffineP}_2 \end{bmatrix} \quad (12)$$

The Equation (13) presents the  $\Delta MV$ , which is used in the Affine 6-parameter prediction model that uses three CPMVs

$$\begin{bmatrix} \delta MV_1 \\ \delta MV_3 \\ \delta MV_4 \\ \delta MV_5 \end{bmatrix} = \begin{bmatrix} \text{AffineP}_1 \times bW + \text{AffineP}_0 \\ \text{AffineP}_3 \times bW + \text{AffineP}_2 \\ \text{AffineP}_4 \times bH + \text{AffineP}_0 \\ \text{AffineP}_5 \times bH + \text{AffineP}_2 \end{bmatrix} \quad (13)$$

The  $\delta MV$  calculated in the previous step is then used to calculate the  $\Delta MV$  that will be added up to the CPMVs currently being evaluated, generating the next set of CPMVs. This can be seen in Equation (14). Where the  $\delta MV$  are the values calculated in the previous step, the  $bW$  and  $bH$  are the PU width and height, and the sign returns 1 if the number is positive or -1 if the number is negative. The  $\Delta MV$  calculated is clipped to 1/16 precision and then added to the current CPMVs, generating the next set of CPMVs.

$$\begin{bmatrix} \Delta MV_0 \\ \Delta MV_1 \\ \Delta MV_2 \\ \Delta MV_3 \\ \Delta MV_4 \\ \Delta MV_5 \end{bmatrix} = \begin{bmatrix} (4 \times \delta MV_0 + 0.5 \times \text{sign}(\delta MV_0)) \ll 2 \\ (4 \times \delta MV_1 + 0.5 \times \text{sign}(\delta MV_1)) \ll 2 \\ (4 \times \delta MV_2 + 0.5 \times \text{sign}(\delta MV_2)) \ll 2 \\ (4 \times \delta MV_3 + 0.5 \times \text{sign}(\delta MV_3)) \ll 2 \\ (4 \times \delta MV_4 + 0.5 \times \text{sign}(\delta MV_4)) \ll 2 \\ (4 \times \delta MV_5 + 0.5 \times \text{sign}(\delta MV_5)) \ll 2 \end{bmatrix} \quad (14)$$

With the new set of the CPMVs calculated, if they are different than the set evaluated, the PU is then Affine MC again, and this process repeats. The GBIA described in this section is repeated up to five times or until all the  $\Delta MV$  calculated are zero, minimizing the error of the predicted block. Then, after this step, the BMIA algorithm is applied over the PU predicted with the last CPMVs calculated in this step, which are the best CPMVs currently found.

### 2.2.3 Block Matching Iterative Algorithm

The BMIA is an algorithm that is applied on the PU with the best CPMVs calculated in the GBIA step. However, this algorithm is much simpler compared to the GBIA. The CPMVs in this step are evaluated by adding  $\pm 1$  to the CPMVs, the block is AMC, and the RD-Cost of the predicted block is calculated. If there are CPMVs with lower RD-Cost, they become the new origin, and the process repeats three times.

The BMIA is divided into two exploration steps in which  $\pm 1$  are added to the CPMVs, one horizontal/vertical and one diagonal. Figure 10 is a visual representation of the horizontal/vertical exploration and the diagonal exploration of the Block Matching Algorithm. As can be seen in Figure 10, BMIA starts with a set of CPMVs and evaluates all neighboring positions of the PU and the position with the smaller RD-Cost is chosen as the final set of CPMVs. Then, a diagonal exploration is done; if any diagonal position has a lower RD-Cost, it becomes the new origin. This repeats three times or

until it does not find any neighboring position with lower RD-Cost.

The BMIA has three rounds of exploration performed for each CPMV, which means that each CPMV can do three horizontal/vertical explorations and three diagonal explorations. This lets the CPMV explore up to radius six around its starting position after the three rounds of exploration. This can be seen in Figure 11, where the black square is the starting position of the CPMV and the blue are all possible ending positions to the CPMV. This heuristic updates the CPMV with the local best neighbor, which may not lead to the best CPMV. However, this algorithm lets the CPMV access 113 possible positions with only 24 iterations. There are 168 positions in a block 13x13 (without counting the origin). The CPMV could access 113 of these positions, or 67% of the search range, with only 24 iterations, or 14% of the iterations, if it were performed an exhaustive search.

For each iteration of the BMIA, an RD-Cost calculation is used to evaluate the new CPMV. If the CPMV evaluation leads to a predicted block with the RD-Cost smaller than the current best-predicted block, the CPMV with the smaller RD-Cost replaces the current CPMV. This step was unnecessary for the GBIA because the error was used to calculate the next set of CPMVs.

### 2.3 Related Works

There are several works in the literature proposing hardware architectures for different video coding standards. However, very few works in the literature present hardware designs for the Affine ME of the VVC standard. Taranto (2022) presents a simplified algorithm and hardware design for the Affine ME on the encoder side. Sheng et al. (2024) presents a SLE solver for the Affine ME.

To achieve a more complete comparison of the hardware designs in the literature, hardware designs for the interpolation filters of the FME were also selected. However, it should be noted that only values related to hardware results, such as area and power

Figure 10 – Representation of the Block-Matching Iterative Algorithm.

Figure 11 – Representation of all the BMIA possible positions explored after three rounds for **one** CPMV.

dissipation, are presented and will be compared as the Affine MC and the FME interpolation filters work similarly. Other results, such as coding efficiency for these works, are not taken into consideration as they are not comparable. These works are Azgin et al. (2018); Canmert; Kalali; Hamzaoglu (2018); Azgin; Kalali; Hamzaoglu (2020); Mahdavi; Azgin; Hamzaoglu (2021); Silva et al. (2021).

The work in Taranto (2022) is the only in current literature presenting a dedicated hardware design for the Affine ME of the VVC standard. This work, however, made a couple of simplifications to the algorithm. The first of the simplifications that will be discussed is the removal of fractional samples. This removes the need for interpolation filters and reduces the computational complexity because a lot of the computational complexity of the interpolation process is processed by intermediate samples. The second simplification discussed is that all PU is broken down to 16x16 blocks and only the corner 4x4 subblocks are processed, processing four subblocks every 16, this reduces the overall computational complexity by 3/4. Also, the architecture only supports PUs in sizes 16x16 up to 64x64. These simplifications are significant changes to the algorithm and lead to an increase in the BD-Rate, which is not provided in the work.

The works Azgin et al. (2018); Canmert; Kalali; Hamzaoglu (2018); Azgin; Kalali; Hamzaoglu (2020); Mahdavi; Azgin; Hamzaoglu (2021); Silva et al. (2021) presents hardware designs for the interpolations filters for the FME. Canmert; Kalali; Hamzaoglu (2018) use offsets to reduce the number of additions and multiplications. The hardware

has eight 8-tap filters, and they present results for both FPGA and ASIC 90nm. Azgin et al. (2018) uses eight 15-tap filters with reconfigurable paths to reduce the number of operations, and the results are presented for both FPGA and ASIC 90nm. Azgin; Kalali; Hamzaoglu (2020); Mahdavi; Azgin; Hamzaoglu (2021) both use 15 4-tap approximate filters, which have low area and power dissipation, and their results are only for FPGA. Silva et al. (2021) presents 15 6-tap approximate filters and MCM approach, which both lead to low area and power dissipation, their present results for ASIC 65nm.

## 3 SOFTWARE EVALUATIONS

This chapter presents the simulations performed on the reference software VTM (VVC Test Model) (Chen; Ye; Kim, 2021). The simulations were performed to evaluate many different constraints:

- Limiting the number of reference frames.

- Limiting PU sizes.

- Limiting the number of Affine MC iterations.

- Combination of constraints.

The number of reference frames increases the number of starting CPMVs that need to be evaluated in the GBIA algorithm. The Affine ME of the VVC standard uses PU sizes from 16x16 to 128x128, so limiting the processed sizes has a great impact because Affine MC is processed on 4x4 subblocks. Limiting the number of iterations in the GBIA and BMIA reduces the number of times the Affine MC is processed. Finally, this chapter presents an analysis of the combination of these constraints regarding the encoding efficiency losses.

### 3.1 Experimental Setup

The simulations presented use the VVC Test Model (VTM), which is the the VVC reference software. The version of the VTM used on all simulations is version 16.2, and the video sequences utilized are the 26 sequences presented in the Common Test Conditions (CTC) (Bossen et al., 2020). Also, the Quantization Parameters (QP) were recommended in the CTC (22, 27, 32, and 37) (Bossen et al., 2020). The simulation uses the default configuration for the sequences, and the temporal profile used is low delay P. The other temporal profiles were not simulated because this simulation is performed focusing on the use in low-power real-time devices, in which low delay is optimal because the future frames are not involved. The setup used for simulation is a Linux server with a CPU XEON Gold 5118 2.30GHz with AMD DIMM 56GB 2400MHz of RAM.

## 3.2 Hardware-Oriented Constraints Evaluation

This section presents the evaluations for the simulations of the constraints utilized, which are:

- Reduction of the reference frames from **four** to **one**.

- PU sizes limited to only **Quadratic** (128x128, 64x64, 32x32, and 16x16) sizes or only 16x16.

- Reduction of iterations to only **GBIA** (which Affine MC up to 5 times, see section 2.2.2) and to only **Affine MC** on the starting CPMVs (GBIA and BMIA disabled).

Then, the combination of these constraints is also evaluated:

- Limiting to only GBIA (see section 2.2.2) and Quadratic PUs

- GBIA and only 16x16 PUs

The reason that the combination only takes into consideration the GBIA is that BMIA significantly increases the overall computational complexity of the algorithm (see section 2.2.3). In contrast, the GBIA iterates very few times and can quickly converge to a minimum error because of the gradient descent (see section 2.2.2). The constraints being changed in the combined evaluation are processing only quadratic PUs and processing only PUs of 16x16.

The recommended test video sequences are divided by classes: A1 and A2 are composed of UHD 4K video sequences; B is composed of FHD 1080p; C, D, and E are composed of low-resolution videos; And F is composed of synthetic videos, of varying resolutions. Also, the results presented in this section are related to the total per frame. The reason for presenting the results per frame is that the framerate of the sequences is variable, with some sequences being 30 fps while others are 50 or 60 fps. Since the data is presented per frame calculating the necessary frequency for different throughputs is straightforward, multiply the data of the desired class by the fps.

### 3.2.1 Results and BD-Rates of Reference Frames Constraints

This section presents data from the Affine ME of VVC, which was extracted from the VTM using the previously mentioned configuration. This section first presents the data for the Affine with four reference frames and then for one reference frame.

The results presented in Table 4 are *ME*, which is how many times the Affine ME is tested in the ME process; *AME*, which means how many times the Affine ME, 4-parameter or 6-parameter, is processed; *Affine-4* and *Affine-6*, which are the number of each model is used; *GBIA* and *BMIA*, which are how many iterations for each algorithm.

Table 4 presents both the average number of occurrences per frame and the standard deviation results considering each class of the recommended test video sequences.

For the most demanding UHD 4K class (A2), as can be seen in Table 4, the Affine ME is to be processed around 30% of the time it the ME is executed. The Affine 6-parameter is processed 23% of the times the 4-parameter is processed. The GBIA processes the Affine MC an average of 5 times per AME. The BMIA processes the Affine MC an average of 2 times. Another important point to pay attention to, especially when calculating the frequency necessary for the processing Affine, is that the standard deviation is as big as the average.

Also, Table 4 shows that Affine computational complexity is extremely high, especially for 4K videos. Ignoring the standard deviation, which is not recommended, and adding the *GBIA* and *BMIA* columns together for the less demanding 4K Class (A1), the result is 5.2M Affine MC per frame, and at 60 fps, this gets to 312M Affine MC per second. This calculation shows that even if the Affine MC of a PU of any size is processed in one clock cycle, which would require an enormous area for parallelism and power dissipation, it would still need 312MHz of frequency.

Table 5 presents the average amount of processing performed by the AME for each PU size considering one frame of each class of the recommended test video sequences. In Table 5, *PU* presents the number of times a PU of that size is processed, *GB* is the number of iterations the GBIA, and *BM* is the number of iterations the BMIA. Table 5 shows that the bigger PU sizes, such as 128x128, use the BMIA more on average than the smaller PUs, such as 16x16.

Table 5 can also be used to show the high bandwidth of the AME. For the UHD 4K Class A1, using the Equation 15, where  $N_{samples}$  are the number of samples interpo-

Table 4 – Results of the Affine Motion Estimation in the VVC for **four** Reference Frames.

| <b>Class</b> |            | <b>ME</b> | <b>AME</b> | <b>AFFINE-4</b> | <b>AFFINE-6</b> | <b>GBIA</b> | <b>BMIA</b> |

|--------------|------------|-----------|------------|-----------------|-----------------|-------------|-------------|

| <b>A1</b>    | <b>Avg</b> | 2.49M     | 720k       | 589k            | 131k            | 3.73M       | 1.47M       |

|              | <b>Std</b> | 2.88M     | 505k       | 407k            | 99.4k           | 2.59M       | 1.38M       |

| <b>A2</b>    | <b>Avg</b> | 2.75M     | 811k       | 659k            | 152k            | 4.09M       | 2.3M        |

|              | <b>Std</b> | 2.65M     | 474k       | 380k            | 94.2k           | 2.35M       | 1.97M       |

| <b>B</b>     | <b>Avg</b> | 708k      | 190k       | 154k            | 36.1k           | 944k        | 573k        |

|              | <b>Std</b> | 705k      | 108k       | 86.5k           | 21.6k           | 531k        | 441k        |

| <b>C</b>     | <b>Avg</b> | 197k      | 41.5k      | 33.5k           | 7.9k            | 210k        | 134k        |

|              | <b>Std</b> | 149k      | 14.1k      | 11.3k           | 2.86k           | 72.7k       | 57.3k       |

| <b>D</b>     | <b>Avg</b> | 55.2k     | 8.82k      | 7.12k           | 1.69k           | 44.1k       | 34.5k       |

|              | <b>Std</b> | 41.8k     | 2.56k      | 2.09k           | 482             | 13k         | 15.5k       |

| <b>E</b>     | <b>Avg</b> | 82.4k     | 41.9k      | 33.7k           | 8.16k           | 189k        | 93.7k       |

|              | <b>Std</b> | 101k      | 31k        | 24.9k           | 6.14k           | 141k        | 84.1k       |

| <b>F</b>     | <b>Avg</b> | 235k      | 71.6k      | 57.9k           | 13.7k           | 330k        | 177k        |

|              | <b>Std</b> | 336k      | 74.5k      | 60.1k           | 14.4k           | 350k        | 211k        |