## ARQUITETURA DE HARDWARE DE FILTRO DE DEBLOCAGEM COM BAIXA DISSIPAÇÃO DE POTÊNCIA E COM SUPORTE A RESOLUÇÕES 8K@60FPS PARA O PADRÃO HEVC DE CODIFICAÇÃO DE VÍDEO

ROBERTA PALAU; JONES GOEBEL; GUILHERME CORRÊA; MARCELO PORTO, LUCIANO AGOSTINI

Universidade Federal de Pelotas - {rcnpalau, jwgoebel, gcorrea, porto, agostini}@inf.ufpel.edu.br

## 1. INTRODUÇÃO

Diante das grandes inovações tecnológicas e da popularização de sistemas eletrônicos de consumo para intercâmbio de dados, cada vez mais recursos de vídeo se fazem presentes em nosso cotidiano. Atualmente os vídeos digitais são utilizados para entretenimento, educação, trabalho e entre outras aplicações. Segundo a CISCO (2016) dados referentes ao acesso de vídeo irão representar 82% de todo tráfego da internet até 2021.

Atualmente a codificação de vídeo é obrigatória para aplicações que utilizam vídeos digitais por causa da grande quantidade de informação necessária para representá-los (AGOSTINI, 2007). Neste cenário, o High Efficiency Video Coding (HEVC) é o estado da arte dos padrões de codificação de vídeo. Este padrão foi desenvolvido com o principal objetivo de duplicar as taxas de compressão atingidas por padrões anteriores e manter a mesma qualidade de imagem, mas as melhorias geraram custos significativos em termos de esforço computacional.

Além da alta qualidade de imagem e altas taxas de compressão, atualmente as aplicações que envolvem a codificação de vídeo devem proporcionar uma taxa de processamento para altas resoluções e baixa dissipação de potência especialmente para equipamentos que capturam/reproduzem este tipo de mídia como plataformas embarcadas com limitação de recursos de energia e computacionais. Desta forma, existem vários trabalhos publicados na literatura com o objetivo de reduzir complexidade e tempo de processamento que gere poucas perdas ou nenhuma em termos de qualidade de imagem e taxas de compressão (FANG, 2015, YE, 2013, OZCAN, 2013, HSU, 2017, DINIZ, 2015).

O processo de codificação do HEVC é baseado em um modelo de codificador híbrido composto por etapa de predição intra-quadros e inter-quadros, transformada, quantização, codificação de entropia, quantização e transformada inversa e dois filtros: filtro de deblocagem e o SAO (Sample Adaptative Offset), cujo objetivo é melhorar a qualidade subjetiva da imagem. O filtro de deblocagem que é o foco deste trabalho tem o objetivo de eliminar o efeito de bloco causado pela etapa de quantização e é aplicado durante a reconstrução do quadro, ele ameniza as bordas entre os blocos e melhora significativamente a qualidade visual do quadro reconstruído e consequentemente a qualidade do vídeo codificado.

Este trabalho apresenta uma arquitetura de hardware do filtro de deblocagem com baixa dissipação de potência e para altas resoluções compatível com o padrão de codificação HEVC. A arquitetura de hardware desenvolvida é baseada no algoritmo do filtro de deblocagem (SZE et al, 2014) e apresenta uma decisão de filtragem que é definida pela análise de características de amostras pertencentes a blocos 8X8 adjacentes em um quadro de vídeo. O filtro de deblocagem opera a partir de três filtros: forte e normal para componentes de luminância e filtro de crominância para componentes de crominância. Dependendo da decisão de filtragem e caso seja necessária, as amostras de

entradas são enviadas para um dos filtros que determina a quantidade de amostras que deverão ser modificadas.

#### 2. METODOLOGIA

A arquitetura de hardware do filtro de deblocagem para o padrão *HEVC* de codificação de vídeo foi descrita em *VHDL*, uma linguagem de descrição de hardware, através do programa *Quartus Prime 16.1 Lite Edition*. Esta arquitetura foi validada a partir do programa *Model Sim Intel FPGA* 10.5b a partir de amostras de entradas baseadas em vetores reais de dados extraídos do software de referência do padrão HEVC Model 16.18. A arquitetura foi sintetizada em *ASIC* (*Application Specific Integrated Circuits*) utilizando uma biblioteca de 45nm *CMOS standard-cell Nangate* em um compilador da marca *Cadence*.

Para atingir o objetivo de suportar uma alta resolução de 8K@60fps (8k *UHD*) foi determinada uma frequência de operação de 186,6 MHz. A frequência de operação foi definida considerando as características da sequência de vídeo (BQTerrace com QP 22) extraída do programa de referência, a qual caracterizou o pior caso em termos de atividade de chaveamento. E foi calculada a partir da equação f = (res x sub x fps x 2) / 32, onde *res* corresponde a resolução, *sub* ao valor da subamostragem, fps ao número de *frames*/quadros por segundo. O filtro deve operar tanto nas bordas verticais quanto nas bordas horizontais dos blocos 8X8 adjacentes, desta forma a multiplicação por dois é necessária. Assim como também é capaz de processar até 32 amostras de entradas por ciclo de *clock*, o que justifica a divisão por 32 na equação.

A Figura 1 apresenta dois blocos 8x8 adjacentes, um bloco P e um bloco Q e em destaque as amostras que são analisadas a partir da borda vertical. O filtro normal modifica até dezesseis amostras (azul e verde), o filtro forte modifica exatamente vinte e quatro amostras (azul, verde e laranja) e o filtro de crominância modifica apenas oito amostras (azul). As amostras circuladas em vermelho são utilizadas para definir a necessidade de filtragem ou não da borda entre os blocos.

| <b>p</b> <sub>3,0</sub> | <b>p</b> <sub>2,0</sub> | <b>p</b> <sub>1,0</sub> | <b>p</b> <sub>0,0</sub> | <b>q</b> <sub>0,0</sub>               | <b>q</b> <sub>1,0</sub> | <b>q</b> <sub>2,0</sub> | $\mathbf{q}_{\scriptscriptstyle 3,0}$ |  |  |

|-------------------------|-------------------------|-------------------------|-------------------------|---------------------------------------|-------------------------|-------------------------|---------------------------------------|--|--|

| <b>p</b> <sub>3,1</sub> | <b>p</b> <sub>2,1</sub> | <b>p</b> <sub>1,1</sub> | <b>p</b> <sub>0,1</sub> | ${\bf q}_{_{0,1}}$                    | <b>q</b> <sub>1,1</sub> | <b>q</b> <sub>2,1</sub> | <b>q</b> <sub>3,1</sub>               |  |  |

| <b>p</b> <sub>3,2</sub> | <b>p</b> <sub>2,2</sub> | <b>p</b> <sub>1,2</sub> | <b>p</b> <sub>0,2</sub> | $\mathbf{q}_{\scriptscriptstyle 0,2}$ | <b>q</b> <sub>1,2</sub> | <b>q</b> <sub>2,2</sub> | <b>q</b> <sub>3,2</sub>               |  |  |

| <b>p</b> <sub>3,3</sub> | <b>p</b> <sub>2,3</sub> | <b>p</b> <sub>1,3</sub> | $p_{0,3}$               | <b>q</b> <sub>0,3</sub>               | <b>q</b> <sub>1,3</sub> | <b>q</b> <sub>2,3</sub> | <b>q</b> <sub>3,3</sub>               |  |  |

|                         |                         |                         |                         |                                       |                         |                         |                                       |  |  |

|                         |                         |                         |                         |                                       |                         |                         |                                       |  |  |

|                         |                         |                         |                         |                                       |                         |                         |                                       |  |  |

|                         |                         |                         |                         |                                       |                         |                         |                                       |  |  |

Figure 1. Amostras de entrada da arquitetura do filtro de deblocagem.

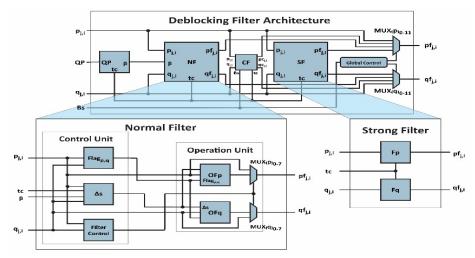

A arquitetura do filtro de deblocagem foi organizada em uma arquitetura principal que é responsável pela decisão de filtragem. Quando a filtragem é necessária é verificado para qual dos três filtros as amostras de entradas serão encaminhadas e há um controle global que define o encaminhamento dessas amostras já modificadas pelo filtro escolhido para a saída da arquitetura principal. Quando a filtragem não é necessária as amostras de entrada são simplesmente enviadas para a saída da arquitetura topo sem nenhuma alteração.

Na Figura 2 é possível observar a arquitetura principal, o bloco NF corresponde ao filtro normal, CF ao filtro de crominância e SF ao filtro forte. As

entradas QP e BS são valores provenientes do processo de codificação e as entradas  $p_{j,i}$  e  $q_{j,i}$  correspondem as amostras de entradas do bloco P e do bloco Q, conforme visto na Figura 1.

Figura. 2 Arquitetura de Hardware do Filtro de Deblocagem

#### 3. RESULTADOS E DISCUSSÃO

Os resultados encontrados neste trabalho estão apresentados na Tabela 1 abaixo, representados por tecnologia (nm), frequência de operação (MHz), taxa de processamento (resolução@fps), área (Kgates) e potência dissipada (mW). Estes resultados são relacionados a outros trabalhos da literatura que também desenvolveram uma arquitetura em hardware do mesmo filtro. Embora não seja possível fazer uma comparação direta com todos os trabalhos relacionados, por envolverem tecnologias diferentes, algumas observações podem ser feitas.

| Trabalho | Tecnologia | Frequência | Resolução@fps | Área     | Potência |

|----------|------------|------------|---------------|----------|----------|

|          | (nm)       | (MHz)      |               | (Kgates) | (mW)     |

| FANG     | 90         | 141,5      | 7682X4320@30  | 12       | -        |

| YE       | 130        | 250        | 3840X2160@60  | 17,6     | -        |

| OZCAN    | 90         | 86         | 1920X1080@86  | 16,4     | 11,55    |

| HSU      | 90         | 100        | 4096X2048@60  | 44,1     | 7,38     |

| DINIZ    | 45         | 200        | 4096X2048@60  | 3,3      | -        |

| Este     | 45         | 186,6      | 7680X4320@60  | 12,1     | 4,32     |

Tabela 1. Resultados encontrados e comparativo com trabalhos relacionados.

Em um comparativo geral com os demais trabalhos podemos destacar que este trabalho atinge uma taxa de processamento muito maior do que todos os trabalhos relacionados, a capacidade de processar 8K *UHD* a 60 quadros por segundo (7680X4320@60) indica um melhor desempenho comparado com as outras arquiteturas. Em termos de consumo em área, a arquitetura proposta utiliza 12,1 Kgates, isto é, utiliza menos área do que YE (2014), OZCAN (2013), HSU (2017). E a arquitetura proposta por FANG (2015) embora consuma 12 Kgates, área ligeiramente menor do que a deste trabalho, atinge apenas a metade da taxa de processamento atingida pelo nosso.

O trabalho de DINIZ (2015) é o único que possui a mesma tecnologia que este trabalho, de 45 nm, comparando diretamente verifica-se que mesmo operando com uma frequência mais baixa é atingida uma taxa de processamento

# ENPOS XX ENCONTRO DE PÓS-GRADUAÇÃO

quatro vezes maior do que a de DINIZ (2015), perdemos em área, porém somos os únicos a atingir essa resolução e processamento em tempo real de 8k *UHD* a uma baixa dissipação de potência. Já a comparação em termos de potência dissipada com o trabalho de DINIZ (2015) não foi possível realizar, pois o trabalho não apresentou esses dados. Com relação a potência dissipada apenas OZCAN (2013) e HSU (2017) apresentaram resultados, respectivamente 11,55mW e 7,38mW comparados aos 4,32mW deste trabalho, porém são baseados em tecnologias de 90nm.

#### 4. CONCLUSÕES

Este trabalho apresentou uma arquitetura de hardware para o filtro de deblocagem de baixa dissipação de potência e com suporte a resoluções 8k@60fps para o padrão HEVC de codificação de vídeo. A proposta implementa três filtros definidos pelo padrão, filtro forte ou normal para componentes de luminância e filtro de crominância para componentes de crominância. Processa 8k *UHD* a uma frequência de 186,6 MHz. E quando comparado com outras arquiteturas encontradas na literatura apresenta uma melhor relação em termos de potência dissipada e taxa de processamento.

# 5. REFERÊNCIAS BIBLIOGRÁFICAS

AGOSTINI, L. "Desenvolvimento de Arquiteturas de Alto Desempenho Dedicadas à Compressão de Vídeo Segundo o Padrão H.264/AVC".2007.172p.Tese (Doutorado em Ciência da Computação) — Instituto de Informática — Universidade Federal do Rio Grande do Sul (UFRGS), Porto Alegre, Brasil.

CISCO, "Cisco Visual Networking Index: Forecast and Methodology, 2016–2021." Acessado em 07 de set. 2018.Online.Disponível em: https://www.cisco.com/c/en/us/solutions/collateral/service-provider/visual-

networking-index-vni/complete-white-paper-c11- \*481360.html# Toc484813989.

DINIZ, C. M; SHAFIQUE, M; DALCIN, F.V; BAMPI, S e HENKEL, J. "A Deblocking Filter Hardware Architecture for the High Efficiency Video Coding Standard," **Design, Automation & Test in Europe Conference & Exhibition (DATE)**. n. 978-3-9815370-4-8. pp. 1509–1514, 2015.

FANG, C.C;CHEN, I and CHANG, T. "A hardware-efficient deblocking filter design for HEVC," **Proc. - IEEE Int. Symp. Circuits Syst.**, vol. 2015, pp. 1786–1789, julho, 2015.

HSU, P e SHEN, C. "The VLSI Architecture of a Highly Efficient Deblocking Filter for HEVC Systems," **IEEE Trans. Circuits Syst. Video Techno**l., vol. 27, n. 5, pp. 1091–1103, 2017.

OZCAN, E; ADIBELLI, Y e HAMZAOGLU, I. "A high performance deblocking filter hardware for high efficiency video coding," **IEEE Trans. Consum. Electron**, vol. 59, n. 3, pp. 714–720, 2013.

SZE, V; BUDAGAVi, M e SULLIVAN, G. Editors, High Efficiency Video Coding (HEVC): Algorithms and Architectures. Texas: Springer Cham Heidelberg New York Dordrecht London, 2014.

YE, X, DING, D e YU,L. "A cost-efficient hardware architecture of deblocking filter in HEVC," **2014 IEEE Vis. Commun. Image Process. Conf**. n. 20120101110032, pp. 209–212, 2014.