# **UNIVERSIDADE FEDERAL DE PELOTAS**

Centro de Desenvolvimento Tecnológico Programa de Pós-Graduação em Computação

Dissertação

**An Evaluation of Memory Controllers for Non-Volatile Memories**

**Giovane de Oliveira Torres**

## **Giovane de Oliveira Torres**

**An Evaluation of Memory Controllers for Non-Volatile Memories**

Dissertação apresentada ao Programa de Pós-Graduação em Computação da Universidade Federal de Pelotas, como requisito parcial à obtenção do título de Mestre em Ciência da Computação

Advisor: Prof. Dr. Maurício Lima Pilla Coadvisor: Prof. Dr. Laércio Lima Pilla

## Universidade Federal de Pelotas / Sistema de Bibliotecas Catalogação na Publicação

## T693a Torres, Giovane de Oliveira

An evaluation of memory controllers for non-volatile memories / Giovane de Oliveira Torres ; Maurício Lima Pilla, orientador ; Laércio Lima Pilla, coorientador. — Pelotas, 2018.

77 f. : il.

Dissertação (Mestrado) — Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, 2018.

1. Memory hieararchies. 2. Computer architectures. 3. Non-volatile memories. I. Pilla, Maurício Lima, orient. II. Pilla, Laércio Lima, coorient. III. Título.

CDD: 005

Elaborada por Maria Inez Figueiredo Figas Machado CRB: 10/1612

## **AGRADECIMENTOS**

É nesta parte da dissertação que preciso agradecer às pessoas que tornaram possível, direta ou indiretamente a realização deste trabalho, pelos mais diferentes motivos. Por mais que eu acredite que seja impossível conseguir resumir em algumas palavras meus mais sinceros agradecimentos, acho importante ainda deixar registradas algumas palavras aqui neste espaço.

O primeiro agradecimento é para a família, especialmente aos meus pais, pelo suporte durante o tempo de mestrado. Ao meu pai, o agradecimento por tudo – não há outra palavra melhor para agradecer, por que senão seria uma longa lista de agradecimentos! À minha mãe (*in memoriam*), que durante nosso tempo de convivência, me deixou diversos ensinamentos que procuro sempre carregar pra minha vida.

Um agradecimento ao meu orientador, Prof. Pilla, que me teve como bolsista durante o tempo do mestrado (e antes já haviam sido quatro na graduação), com quem tive a oportunidade de aprender diversos assuntos. Outro agradecimento ao meu co-orientador, Prof. Laércio, pelas diversas ajudas nas várias etapas durante o mestrado. Mais um agradecimento aos demais professores do curso, por ensinamentos, conversas e outras coisas.

Muitíssimo obrigado ao LUPS, o laboratório que continuei meus estudos para fazer o mestrado, que embora às vezes tenha sido um lugar com diversos problemas para trabalhar, me propiciou boas experiências. Indepentente disso, foi lá que desenvolvi o trabalho escrito nesta dissertação; conheci pessoas incríveis; fiz amizade com algumas poucas pessoas, que me ajudaram demais, além de proporcionar boas histórias, risadas e outras coisas, tanto em atividades dentro quanto fora da faculdade – e estes, vocês sabem quem são, não é mesmo, seus aleatórios?

Mais um agradecimento é necessário, à todas as pessoas que tive a oportunidade de conhecer neste período. Cada um, mesmo não sabendo, me ensinou alguma coisa diferente. A quem eu conheci e foi construída uma amizade neste período, um outro muito obrigado: por ajudas, conversas, e outras tantas coisas feitas. E aos amigos que eu já tinha antes de começar o mestrado, e que ainda continuam sendo meus amigos, vai um grande agradecimento, por todos os tipos de atividades feitas que, sem dúvidas, foram extremamente importantes para mim.

## **ABSTRACT**

TORRES, Giovane de Oliveira. **An Evaluation of Memory Controllers for Non-Volatile Memories**. 2018. 77 f. Dissertação (Mestrado em Ciência da Computação) – Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, Pelotas, 2018.

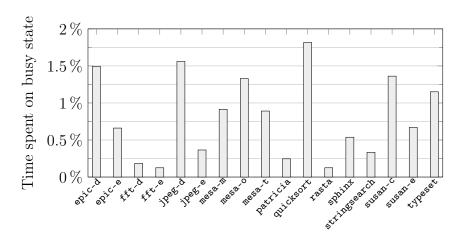

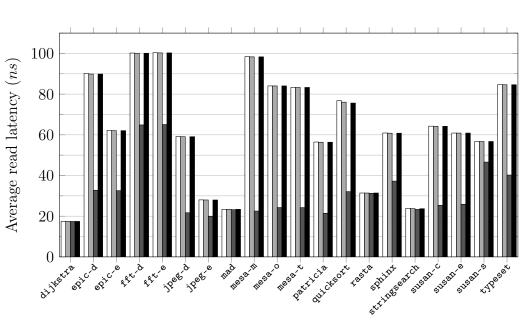

Many demands which include performance and energy consumption are present in current computational systems. In this context, actual memory technologies are critical components which affect directly both performance and energy cost of a system. Thus, memory needs improvements since they could be reaching its scalability limit. One of the alternatives to improve memory subsystems is the use of non-volatile memories (NVMs). These memories have overall low energy consumption and better scalability when comparing with volatile memories. However, NVMs still have issues which need to be overcome in order to allow large-scale use. Those issues include costly write operations (both on latency and energy) and lower material endurance if compared to current memory technologies. Parallel to that, one difficulty to adopt NVMs as main memories in computational systems is related to providing a proper scheduling of memory operations - as it should cope with the particular characteristics of NVMs. With that issues in mind, this work presents a memory controller implementation – in addition to that, a runtime analysis of memory operations in NVM-based systems is performed. To implement a memory controller, we use Gem5 and NVMain simulators, since their combination could reach runtime evaluations that this work aims. Then, the implemented controller was tested by running applications from MediaBench and MiBench benchmark set. With that, the controller was analyzed under different configurations. Tests were performed using the three most well-known and studied NVMs (PCRAM - Phase Change Random Access Memory, RRAM - Resistive Random Access Memory and STT-RAM - Spin Transfer Torque Random Access Memory). The main observations that could be highlighted in this work were: (i) while running the benchmarks in isolation, the time spent in serving memory requests is very low, not surpassing 2% of the total execution time of any application tested, (ii) when running the memory controller under different NVM technologies, latencies of read and write operations in overall were mostly impacted by the different type of memories used, (iii) when using queues with variable sizes to hold memory requests, it made negligible difference in overall performance, due to applications having small busy periods, i.e., generating and serving a small number of memory requests in detriment of other operations. Lastly, a comparison between the implemented memory controller and NVMain default memory controllers was performed, which pointed out that in the majority of the studied cases, the proposed

## **RESUMO**

TORRES, Giovane de Oliveira. **Uma Avaliação de Controladoras de Memória para Memórias não Voláteis**. 2018. 77 f. Dissertação (Mestrado em Ciência da Computação) — Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, Pelotas, 2018.

Existem atualmente diversas demandas nas questões de desempenho e consumo energético em sistemas computacionais. Dentro deste contexto, as tecnologias de memórias usadas atualmente são consideradas componentes críticos que afetam diretamente tanto desempenho quanto consumo energético dentro em um sistema. Com isto, existe a necessidade de que memórias apresentem melhorias, já que estas talvez estejam chegando no seu limite de escalabilidade. Uma das alternativas para melhorar o subsistema de memória é o uso de memórias não voláteis (NVMs). Estas memórias têm em geral baixo consumo energético e melhor escalabilidade ao comparar com tecnologias voláteis. Porém, NVMs apresentam problemas que precisam ser superados para que estas possam ser utilizadas em larga escala. Estes problemas remetem ao alto custo de operações de escrita em memória tanto em latência quanto em consumo energético, além de durabilidade do material usado nas NVMs sendo inferior se comparado à tecnologias de memória atuais. Paralelo a isto, uma das dificuldades para adotar uma NVM como memória principal em sistemas computacionais também inclui dificuldades em propor um escalonamento de operações de memórias, já que torna-se necessário lidar com as características de NVMs. Com estes problemas em mente, esse trabalho apresenta uma implementação de controladora de memória, juntamente com uma análise em tempo de execução em sistemas baseados em NVMs. Para implementação de uma controladora de memória, são utilizados os simuladores Gem5 e NVMain, visto que a combinação destas atende ao desejo do trabalho de efetuar avaliações em tempo de execução. Com isto, a controladora implementada passou por testes com aplicações do conjunto de benchmarks Media-Bench e MiBench. Assim, a controladora foi analisada sobre diferentes configurações. Testes foram feitos usando as três tecnologias de NVMs mais conhecidas e estuadas (PCRAM - Phase Change Random Access Memory, RRAM - Resistive Random Access Memory e STT-RAM - Spin Transfer Torque Random Access Memory). As principais observações feitas por este trabalho foram: (i) executando os benchmarks isoladamente, o tempo gasto em atender requsições de memória foi baixo, não superando 2% do tempo total de execução de qualquer aplicação, (ii) ao executar a controladora de memória com diferentes NVMs, as latências de operações de memória foram impactadas fortemente pelo tipo de tecnologia utilizada, (iii) ao utilizar diferentes tamanhos de filas para atender requisições de memórias, o impacto causado por esta variação foi considerado desprezível, já que as aplicações executadas geraram e atenderam poucas operações de memórias em detrimento de outras operações. Por fim, uma análise de desempenho da controladora implementada com as controladoras de memória fornecidas pelo NVMain, sendo observado que na maioria dos casos a controladora proposta e avaliada talvez necessite de inclusão de outras técnicas para a extração de melhor desempenho.

Palavras-Chave: hierarquias de memória; arquitetura de computadores; memórias não voláteis

# LIST OF FIGURES

| Basic STI-RAM cell structure (MEENA et al., 2014) Conceptual view of the MTJ structure (ZHOU et al., 2009) Example of a basic PCM cell structure (NUMONYX, 2007) Time and current intensity necessary for each memory operation in a PCM cell (WANG; WU, 2009) | 19<br>20<br>21<br>22<br>23                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                | 29                                                                                                             |

| The idle automaton (DASARI; NELIS; MOSSE, 2013)                                                                                                                                                                                                                | 29                                                                                                             |

| Overview of NVMain Architecture: one memory controller for one memory channel (POREMBA; ZHANG; XIE, 2015)                                                                                                                                                      | 34                                                                                                             |

| request queue capacity (IsIssuable method)                                                                                                                                                                                                                     | 36                                                                                                             |

|                                                                                                                                                                                                                                                                | 37                                                                                                             |

| Diagram that schedules requests and turn them into operations (Cycle method)                                                                                                                                                                                   | 38                                                                                                             |

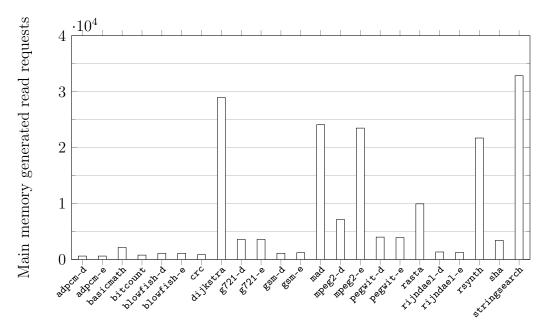

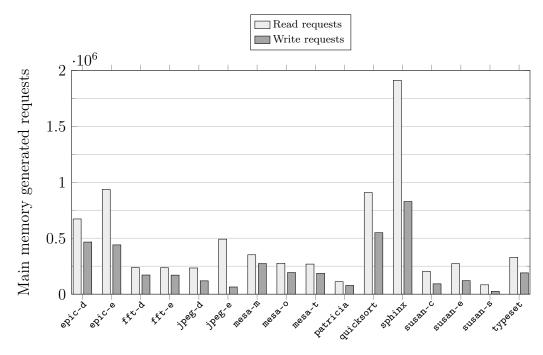

| Total of read main memory requests performed in each benchmark, where the number of read requests $\leq 50,000$                                                                                                                                                | 45                                                                                                             |

| Total of main memory requests performed in each benchmark, where the number of read requests > 50.000                                                                                                                                                          | 46                                                                                                             |

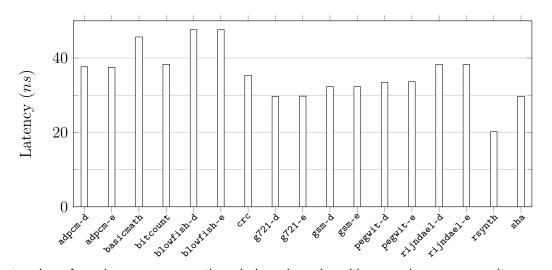

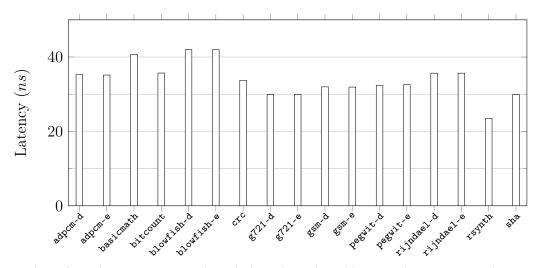

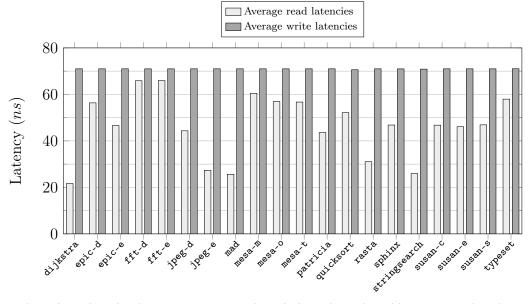

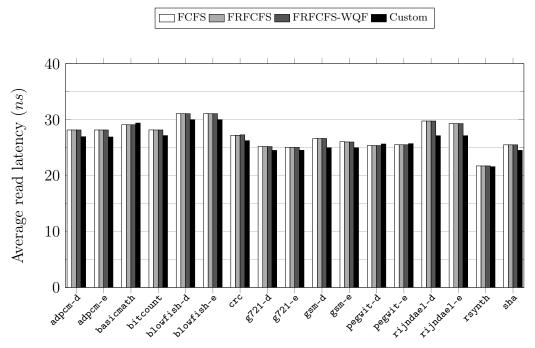

| ·                                                                                                                                                                                                                                                              | 48                                                                                                             |

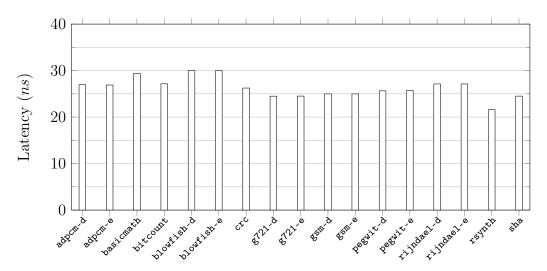

| · ·                                                                                                                                                                                                                                                            | 50                                                                                                             |

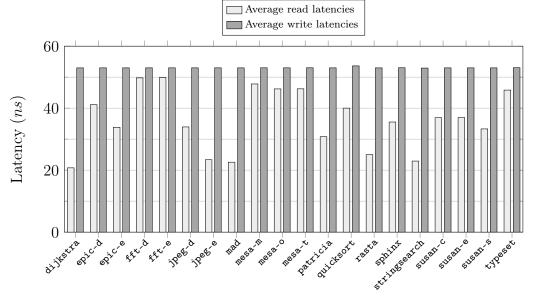

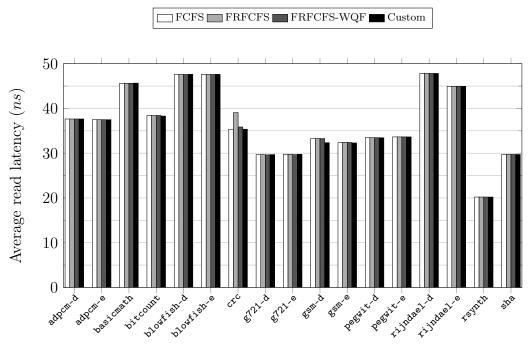

| Latencies of memory operations with an STT-RAM as main memory                                                                                                                                                                                                  | 52                                                                                                             |

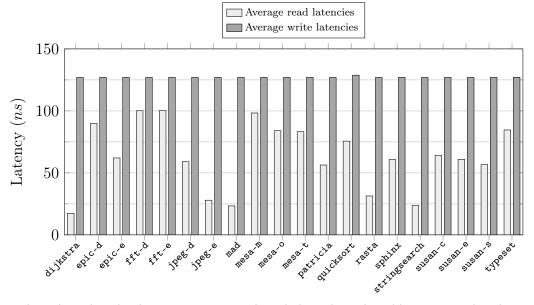

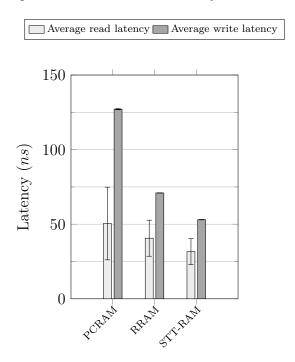

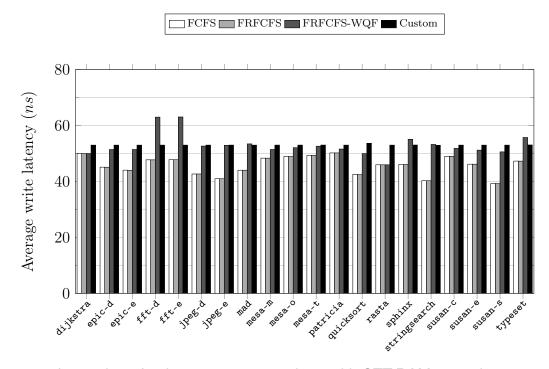

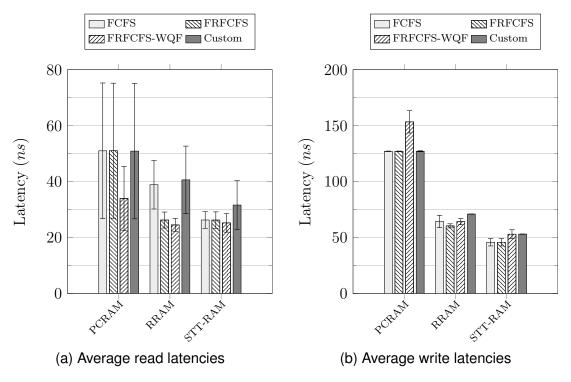

| Averages of read and write latencies for each NVM as main memory                                                                                                                                                                                               | 53                                                                                                             |

| Percentage of time spent in busy state during benchmark executions                                                                                                                                                                                             | 54                                                                                                             |

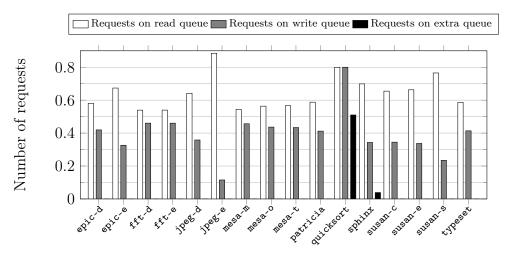

| Average number of requests in memory controller queues while on                                                                                                                                                                                                | 56                                                                                                             |

|                                                                                                                                                                                                                                                                | 50                                                                                                             |

| in multiple memory controllers                                                                                                                                                                                                                                 | 59                                                                                                             |

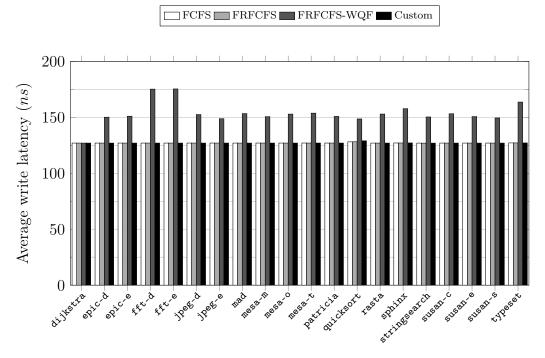

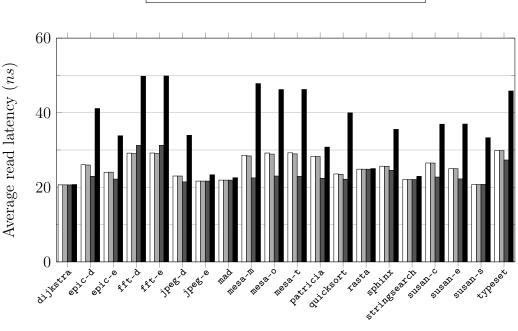

| Latencies of write memory operations with PCRAM as main memory                                                                                                                                                                                                 |                                                                                                                |

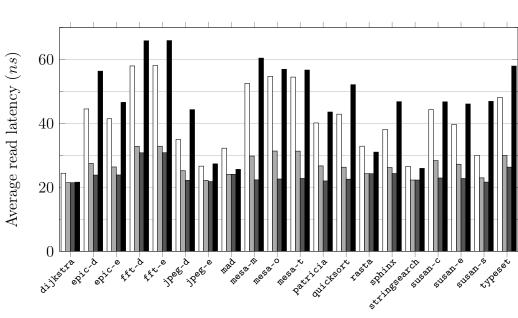

| •                                                                                                                                                                                                                                                              | 60                                                                                                             |

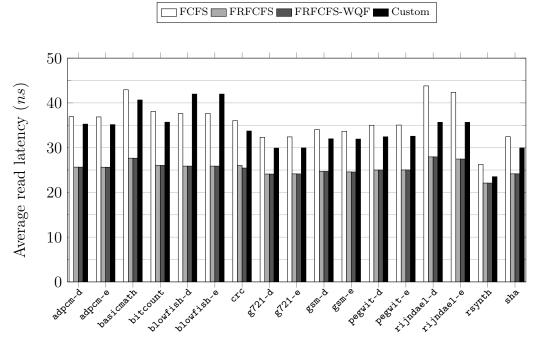

| Latencies of read memory operations with RRAM as main memory in multiple memory controllers                                                                                                                                                                    | 61                                                                                                             |

|                                                                                                                                                                                                                                                                | Conceptual view of the MTJ structure (ZHOU et al., 2009) Example of a basic PCM cell structure (NUMONYX, 2007) |

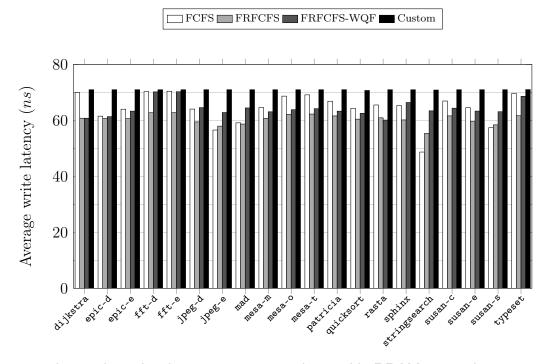

| 24 | Latencies of write memory operations with RRAM as main memory    |    |

|----|------------------------------------------------------------------|----|

|    | on multiple memory controllers                                   | 62 |

| 25 | Latencies of read memory operations with STT-RAM as main mem-    |    |

|    | ory in multiple memory controllers                               | 63 |

| 26 | Latencies of write memory operations with STT-RAM as main mem-   |    |

|    | ory on multiple memory controllers                               | 64 |

| 27 | Latencies of memory operations in different NVM technologies and |    |

|    | memory controllers                                               | 65 |

# **LIST OF TABLES**

| 1      | Comparing NVM and current volatile memories (CHI; LEE; XIE, 2014; ENDOH et al., 2016; LEE, 2016)             | 25 |

|--------|--------------------------------------------------------------------------------------------------------------|----|

| 2      | Notations in busy and idle automata                                                                          | 28 |

| 3<br>4 | Internal parameters used in custom memory controller Notations used in the diagrams of the memory controller |    |

| 5<br>6 | Benchmark compiled and executed status                                                                       |    |

# LIST OF ABBREVIATIONS AND ACRONYMS

BL Base Line

DRAM Dynamic Random Access Memory

FCFS First Come First Served

FRFCFS First Ready First Come First Served

FRFCFS-WQF First Ready First Come First Served with Write Queue

FERAM Ferroelectric Random Access Memory

HRS High Resistance State

LRS Low Resistance State

MIM Metal-Insulator-Metal

MTJ Magnetic Tunnel Junction

MRAM Magnetic Random Access Memory

NVM Non-Volatile Memory

PCM Pulse-code modulation

PCRAM Phase Change Random Access Memory

RRAM Resistive Random Access Memory

SL Source Line

SRAM Static Random Access Memory

STT-RAM Spin Torque Transfer Random Access Memory

WL Word Line

# **CONTENTS**

| 1                                             | INTRODUCTION                                                        | 14                                                                   |

|-----------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------|

| 2<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5          | NON-VOLATILE MEMORIES  STT-RAM  PCRAM  RRAM  Discussion  Conclusion | 18<br>18<br>20<br>22<br>24<br>25                                     |

| 3<br>3.1<br>3.2                               | MEMORY OPERATION SCHEDULING                                         | 26<br>27<br>30                                                       |

| 4<br>4.1<br>4.2<br>4.3<br>4.4                 | MEMORY CONTROLLER FOR NON-VOLATILE MEMORIES                         | 32<br>32<br>33<br>34<br>39                                           |

| <b>5 5.1 5.2 5.4</b> 5.4. 5.4. 5.4. 5.5. 5.5. | Evaluating length of busy periods                                   | 40<br>40<br>41<br>44<br>46<br>54<br>55<br>56<br>57<br>58<br>60<br>62 |

| 5.5.<br><b>5.6</b>                            | 4 Overall Analysis                                                  | 64<br>66                                                             |

| 6<br>6.1                                      | CONCLUSION                                                          | 67<br>68                                                             |

| REI                                           | FERENCES                                                            | 70                                                                   |

## 1 INTRODUCTION

Nowadays, there is a constant need for more computational power. In this context, it is always important to find technological innovations that allow upgrades in both performance and energy consumption. One of the areas that is the target of those updates is the current memory technologies, due to multiple reasons: (i) memories are reaching their scalability limit (POREMBA; XIE, 2012; YOUNG; NAIR; QURESHI, 2015; OUKID; KETTLER; WILLHALM, 2017), (ii) due to the way memories are constructed, leakage current is becoming more of a problem (WANG; ALZATE; AMIRI, 2013; LI et al., 2015; AWAD et al., 2016) and (iii) memory is considered to be a critical component in computational systems (PEREZ; DE ROSE, 2010; ZOU et al., 2015; POURSHIRAZI; ZHU, 2016). With that considered, in order to allow progress in computational systems, it is essential that memories also get improvements.

One possibility to perform upgrades in memories lies in the replacement of current memory technologies used – those being DRAM (Dynamic Random Access Memory) and SRAM (Static Random Access Memory) – by non-volatile memories (NVMs). These memories can provide low energy consumption, as well as better scalability and higher density by memory cell (MEENA et al., 2014; YOUNG; NAIR; QURESHI, 2015; ZHAO et al., 2015). The non-volatility feature of memory allows data to be retained for a long period of time, which varies accordingly to the material used in a memory cell. On the other hand, this does not occur in volatile memories, where refresh operations are necessary to retain data. When performing continuous refreshes over time, the cost to maintain data in memory cells grows. However, NVMs also have issues that must be overcome so that they could be used in large scale. One of the biggest problems are related to NVM endurance: Due to the material used to make NVM cells, they have lower endurance if compared with volatile technologies. Also, both energy consumption and time spent to perform write operations in NVM cells are considered highly costly (MEENA et al., 2014).

In this work, three NVMs were studied: PCRAM (Phase Change Random Access Memory), STT-RAM (Spin Transfer Torque Random Access Memory) and RRAM (Resistive Random Access Memory). These specific memories were picked according

to a study done on NVMs which analyzed that most NVM related work discusses these three memories (MITTAL; VETTER, 2016). In addition to that, these NVMs have the potential for building high-density and power-efficient memory systems, thanks to enhanced scalability and non-volatility properties (YOUNG; NAIR; QURESHI, 2015). NVMs are applicable for a multitude of different computational areas, showing promising results. These include: embedded systems (WANG; ALZATE; AMIRI, 2013; CHANG et al., 2014), real-time systems (DASARI; NELIS; MOSSE, 2013; ZHANG et al., 2013), systems with NVMs as main memory (KÜLTÜRSAY et al., 2013; CHI; LEE; XIE, 2014; ZHANG et al., 2016), hybrid memory architectures (WANG et al., 2014), among others.

The studied NVMs can be inserted at different parts of a memory architecture. PCRAM is considered to be a future candidate for replacing DRAM as main memory (LI et al., 2014; ARJOMAND et al., 2017), plus large PCRAM chips are already available (CHUNG et al., 2011; CHOI et al., 2012). On the other hand, RRAM is tested mainly in cache memories (KOTRA et al., 2016; LI et al., 2017), and STT-RAM has most studies focused also in cache memories (YAZDANSHENAS et al., 2014; KIM; KIM; LEE, 2017). When developing large chips, these memories also present issues regarding reliability, (KANG et al., 2015; MUTLU; SUBRAMANIAN, 2015). Nevertheless, there is work showing that using both STT-RAM and RRAM as main memories show promising results (KÜLTÜRSAY et al., 2013; CHI et al., 2016).

One of the key challenges to improve performance of memories resides in attending read and write instructions in the best instance of time possible. Memory scheduling tends to be a complex problem, due to having to cope with multiple issues (MARTINEZ; IPEK, 2009; KIM et al., 2010; GOOSSENS et al., 2016). In some categories of systems, such as real-time systems, a set of memory operations needs to complete within a fixed deadline (FUJITA, 2014), however that may come with more costs with hardware mechanisms, which leads to more energy consumption. Hence the use of an NVM as a main memory in computational systems is seen as an alternative to improve energy consumption. When dealing with systems with NVM as main memories, a reasonable number of memory operations may not accomplish their deadlines, which can result in unacceptable delays in execution times of memory operations (DASARI; NELIS; MOSSE, 2013). With these exposed problems, memory controller scheduling policies may need to mitigate these issues (ZHOU et al., 2011; DASARI; NELIS; MOSSE, 2013; HU et al., 2014), by taking into account the natural issues found in NVMs – those being asymmetry of read and write operations, plus limited write endurance.

Considering the importance of memory operation scheduling and the use of NVMs, this work explains one of its main contributions: The implementation of a memory controller aware of NVM issues. This controller was based on the work of Dasari, Nelis and Mosse (2013) – in that work, a memory controller was proposed and a static anal-

ysis with traces of already-run benchmarks was performed. Here, the implementation extends the idea to implement the memory controller in a general-purpose simulator, so that it can evaluate the potential performance of memory controller during runtime. In order to do that, two tools were used: NVMain and Gem5, where the first one simulates NVMs, while the second one is a general-purpose simulator. These tools were chosen since their combination allows the runtime analysis this work aims. The main contribution of this work is the behavioral analysis of a different memory controller implementation, plus an evaluation its potential performance.

To provide results for this work, applications were chosen to run over the modified simulator. For this, the sets of benchmarks MediaBench and MiBench were chosen. The first result presented on this work tested the memory controller over three distinct NVMs as main memories (PCRAM, STT-RAM and RRAM), where it was seen that write memory latencies had expected results accordingly to each NVM used. On the other hand, read latencies suffered from great variations, according to the NVM and benchmark simulated. Then, both periods of benchmarks were analyzed – these periods were based on the concept of busy and idle states of the implemented memory controller, where the first one is designed to attend memory requests, while the other one waits for memory requests to come. Performed analysis show that the mean of time spent in busy periods was small, not surpassing 2% of the total execution time. Additionally, the use of queues in the implemented memory controller was analyzed, showing that queues were in overall underused, accompanying the low time spent in busy periods. On average, applications do not keep more than one request in queue when the memory controller is active, which was probably a consequence of benchmarks running in isolation – hence, this not allow the generation of a large number of memory requests. Even though this occurred, it was possible to detect benchmarks which generated bursts of memory operations, which could potentially put more pressure under the memory controller buffers in a full-system simulation.

The implemented controller was compared with already-established controllers provided by NVMain – results were presented evaluating performance on latencies of read/write operations. Regarding write memory operation latencies, when simulating with PCRAM as main memory, the custom memory controller matched these latencies of NVMain memory controllers. On the other hand, in RRAM and STT-RAM simulations write latencies tended to be worse if comparing with already-implemented memory controllers. When evaluating read latencies, on overall the results presented many variations, depending directly of the executed benchmark. This work then concludes that (i) the proposed controller may need improvements or consider other memory scheduling techniques so that better performance can be extracted and (ii) the controller may be used in hybrid memory systems in order to extract the best features each technology of memory can offer.

This work is organized as follows: Chapter 2 makes a brief study of current NVM technologies which are considered by this work (PCRAM, STT-RAM and RRAM), depicting their individual features. Chapter 3 explains the importance of memory scheduling, linking with NVM-based systems. Also, this Chapter exposes a schema for a memory controller, where the implementation is based. Chapter 4 summarizes the main contribution of this work, explaining how it was done, exposing the tools used and how the memory controller implementation was performed. Chapter 5 exhibits the main results reached by this work, and lastly, Chapter 6 explains the main conclusions achieved, also presenting potential future work.

## 2 NON-VOLATILE MEMORIES

NVMs are memory technologies that feature the potential to retain data for long periods without needing constant refresh operations as seen in volatile memories. NVM technologies work due to the materials used as memory cells because they have the possibility to change their state by applying an electric current.

These technologies hold potential to both consume very low power and provide much higher density than current volatile technologies such as DRAM and SRAM. However, NVMs have some issues that need to be overcome, which include poor write endurance (being several orders of magnitude lower than conventional memories) and high latency and energy costs when performing write operations (MITTAL; VETTER, 2016).

The NVM technologies studied for this work are presented in the following Sections: STT-RAM in Section 2.1, PCRAM in Section 2.2 and RRAM in Section 2.3. Then, Section 2.4 makes a short discussion of the three non-volatile technologies. Lastly, Section 2.5 concludes this Chapter.

#### 2.1 STT-RAM

STT-RAM (Spin Transfer Torque Random Access Memory) is an NVM that is listed to be a future candidate to replace SRAM (THOMAS et al., 2014; ZHAN et al., 2016), which is mostly used as cache memories, even though some related work shows that it could be used as main memory (KÜLTÜRSAY et al., 2013; EWAIS et al., 2016). STT-RAM is considered to be an improvement over MRAM (Magnetic Random Access Memory), as STT-RAMs exert the base platform established by MRAMs to enable highly scalable memory, smaller cell sizes and better read and write latencies (MEENA et al., 2014).

An STT-RAM cell is composed of two magnetic storage devices that are different from each other. The first device has fixed magnetic orientation, while the second one holds the possibility to change its orientation. Both devices are also called ferromagnetic layers, where the first one is called **reference layer** and the second one is defined

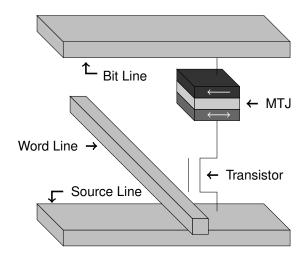

as **free layer** (ZHOU et al., 2009). A third device is also placed between these two layers, which is called tunnel barrier layer. The grouping of the three layers is defined as the magnetic tunnel junction (MTJ), which is the key element to store information. The effect known as **spin transfer torque** occurs when a relatively strong electric current is applied in the MTJ that can flip the free layer magnetic orientation, which happens when an electron with a misaligned spin passes into a magnetized material – that mismatch gives rise to a torque between the electron and the magnet (COALMON, 2009). Figure 1 depicts an example of a basic STT-RAM cell structure. Besides the MTJ, the STT-RAM cell includes a bit line (BL) and a source line (SL). Depending of the current applied over these lines, it performs different memory operations. The word line (WL) is used to connect multiple memory cells, allowing to read an entire row of cells. Lastly, the transistor placed below the MTJ is used to allow the memory operations in a STT-RAM cell.

Figure 1 – Basic STT-RAM cell structure (MEENA et al., 2014)

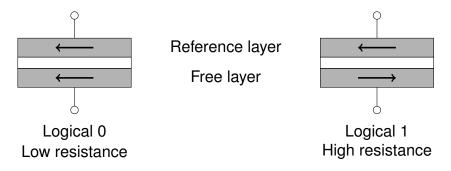

In order to represent a bit value (logical 0 and logical 1), the magnetization difference of the reference layer and free layer is used – which is translated into a resistance difference in the MTJ. When the magnetic field of the free layer and reference layer is parallel, the MTJ resistance is low and can be interpreted as the logical zero. However, when these two layers have opposite magnetic orientations the MTJ resistance becomes high, thus the logical one can be represented. Figure 2 shows a conceptual view of the MTJ and its possible magnetic orientations.

In order to do operations in STT-RAM cells, an NMOS is connected to the WL to allow selection of a row of cells. Thereafter, a voltage is applied between the bit line BL and source line SL. Depending of the voltage applied, a different operation is performed (ZHOU et al., 2009):

• Read: A small voltage is applied between BL and SL. The amount of current that flows through the cell depends of the resistance of MTJ, which may be low or

Figure 2 – Conceptual view of the MTJ structure (ZHOU et al., 2009)

high depending of the magnetic orientation of the free and reference layers. The resistance is sensed by an amplifier to output the value stored in the cell;

- Write (Reset): A larger, positive voltage is applied between SL and BL, creating a current flow from SL to BL;

- Write (Set): A larger but negative voltage is applied between SL and BL, creating a current flow in the opposite direction.

The advantages of using STT-RAM are the same as described in general NVMs: low power consumption and smaller cell sizes. When comparing STT-RAM to a conventional technology such as SRAM, it could certainly achieve 4 times greater density (ZHOU et al., 2009; ZHANG et al., 2015), but it is possible that it can reach even higher densities (KANG, 2010; YAKOPCIC; HASAN; TAHA, 2015).

However, STT-RAMs present issues regarding the asymmetry in latencies and energy consumption in read and write operations in memory cells. When performing a read operation, both latency and energy consumption are comparable to a SRAM cell read. That does not occur in a write operation, where the latency and energy consumption are much higher when comparing to the same SRAM cell (KÜLTÜRSAY et al., 2013).

#### 2.2 PCRAM

Phase-Change Random Access Memory (PCRAM) is other type of NVM that is also considered as a technology for future memories (OIKE et al., 2015; BURR et al., 2016), which is seen as an alternative to the main memory of a computer architecture that offers better density per cell if compared to conventional memories (DU et al., 2013);

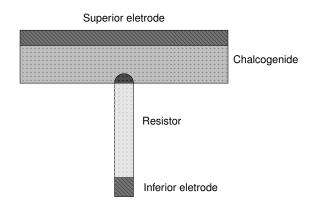

PCRAM cells are composed of two electrodes separated by a resistor, plus a phase change material – which is commonly a chalcogenide (RAOUX et al., 2014; PIROVANO, 2018). The  $Ge_2Sb_2Te_5$  composite (Germanium-Antimony-Tellurium) is the most commonly used (MENG et al., 2016; BURR et al., 2016), although there is related

work that study various doping elements in the  $Sb_2Te_5$  composite that can use titanium, aluminum, gallium, among other metals.

The phase change material layer is responsible for information storage in PCRAM, and it can be in two different states: **amorphous** and **crystalline**. By using these two distinct states it is possible to represent the two logical values of a bit, because each state holds a different resistance which differentiates from the other one. The amorphous state has high resistance, and it is used to represent logical 0, while the crystalline one has low resistance and it represents logical 1. Figure 3 depicts an example of a PCM cell. A layer of phase change material is placed between both electrodes. The lower electrode has a heat-resistant element (resistor) which makes contact with the chalcogenide layer.

Figure 3 – Example of a basic PCM cell structure (NUMONYX, 2007)

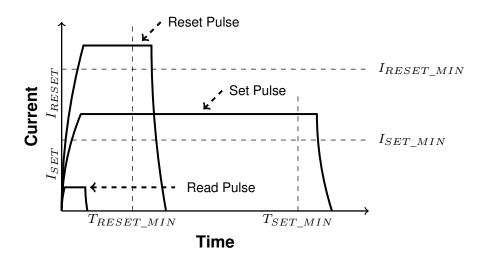

The action of applying a current in the junction of resistor and chalcogenide denotes that an operation over a memory cell is going to be performed. Both intensity and time of an electric current define which memory operation will occur. This is shown in Figure 4, which summarizes the time and current intensity necessary to do read and write (set and reset) operations.

Each memory operation has well-defined parameters of time and current intensities. Below, every operation is explained:

- Read: A current of small intensity and time is applied, so that the phase change

material is not changed in process. Then the material resistance is measured,

which is different according to the current cell state;

- Reset: In this case a short time but intense current must be applied. Due to abrupt interruption of the current, the phase change material resistance increases – and by quickly stopping heat generation, the material turns into an amorphous state;

- Set: A current with longer time and moderate intensity is applied. By reducing the current, the material will reduce its resistance as well. The phase change material will also cool down slowly, turning into a crystalline state.

Figure 4 – Time and current intensity necessary for each memory operation in a PCM cell (WANG; WU, 2009)

Advantages found in PCRAMs can also be seen in those offered by NVMs, which include high scalability and lower energy consumption. PCRAM is also affected by the main problems found on non-volatile technologies, thus performing a write operation in a memory cell is costly on both energy consumption and time. As seen in Figure 4, the maximum time spent in a memory operation is defined by the set operation – and energy consumption peak occurs when a reset operation is done. Constant write operations in PCRAMs tend to deteriorate the phase change material more quickly if compared with conventional technologies – the write endurance of PCRAMs is orders of magnitude lower than DRAMs and SRAMs.

#### **2.3 RRAM**

The Resistive Random Access Memory (RRAM) is pointed to be another future candidate for general-purpose memory due to some of its features. Those include (i) excellent potential to miniaturization – its cell size can reach  $4F^2$  (where F stands for line width), (ii) possibility to replace DRAM as main memory, (iii) and natural integration to 3D memories (ZHOU; KIM; LU, 2014; PAN et al., 2014; SONG et al., 2017).

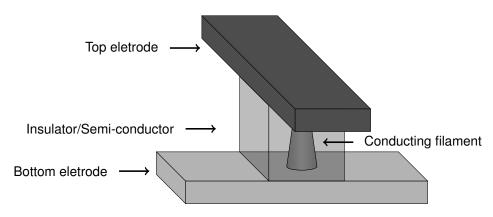

A RRAM cell is usually composed of a device with an isolating or semiconductor material layer placed between two conductive metals – this structure is called Metal-Insulator-Metal (MIM). Figure 5 shows an example of a RRAM cell. The middle layer of an MIM is used as storage of memory information, while top and bottom layers are used as electrodes.

The middle layer of an MIM is commonly made of an oxide due to its natural feature of undergoing resistance change effects. In particular, metal oxides are the most studied alloys in related work (MEENA et al., 2014; IELMINI, 2016). On the other hand, the materials of electrode layers studied are quite varied, since its range can start

Figure 5 – Basic structure of an RRAM cell (PAN et al., 2014)

from pure elements that could be used up to complex alloys, and even some kinds of oxides (PAN et al., 2014).

In order to perform memory operations over RRAM cells, current must be applied in one of the electrodes. Similar to what occurs in a PCRAM, current intensity is the key to determine what operation will be run.

- Read: A small intensity current is applied, which needs to be little enough so it

does not change the state of insulator layer. With that current, it is possible to get

the material resistance and thus getting its value stored;

- Set: A current with more intensity than one used to read from a cell is applied –

which needs to be intense enough to reduce to turn the insulator layer resistance

into a low resistance state (LRS);

- Reset: In this case, the current needs to be sufficiently intense to increase resistance to switch the insulator layer resistance to a high resistance state (HRS).

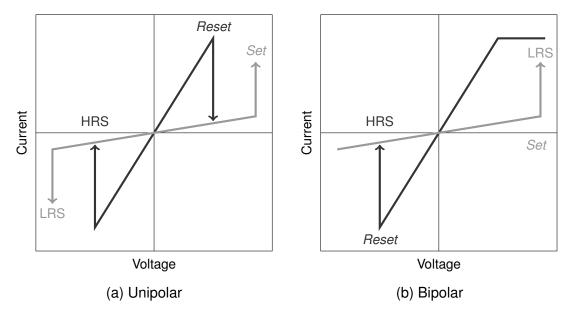

Another important aspect that must be analyzed on metal-oxide RRAMs relates to switching modes. These can be split in two general modes called **unipolar** and **bipolar**. Figure 6 shows a schema explaining how write operations are performed depending of switching modes. Unipolar switching means the switching direction depends on only the amplitude of an applied voltage, and it does not depend on the polarity. Thus, both write operations can occur at the same polarity. On the other hand, bipolar switching means the switching direction depends of the polarity of an applied voltage, which means the set operation can only occur at one polarity, and reset operation must occur at the reverse polarity.

Even though RRAMs are candidates to be largely used future memories, there are several issues that need to be addressed. As seen in previous NVMs, high latency and energy consumption of write operations and low material endurance are problems seen in RRAM cells. Studies on increasing reliability and maintenance of the materials

Figure 6 – Relation between current and voltage on different switching modes of RRAM (WONG et al., 2012)

used in RRAMs are essential to their future (MEENA et al., 2014). One of the main issues to adopt the use of commercial RRAMs is the lack of a thorough understanding of the switching mechanisms: the effect of switching states is hard to locate (because of the tiny device) and it is of random nature (PAN et al., 2014). Also, write endurance problem tends to be one of the long-term challenges to allow RRAMs to be used as large-scale memories (AKINAGA; SHIMA, 2012).

## 2.4 Discussion

With all of the features presented by each NVM, they are promising candidates to replace actual technologies. The features presented by NVMs allow them to be used in many different situations, which is seen in the diversity of related work (MITTAL; VETTER; LI, 2015; MITTAL; VETTER, 2016). The studied memories on this work are composed of different materials implies in unequal characteristics and different ways of performing read and write operations in each NVM. Table 1 shows electrical and physical features of both presented NVMs and actual volatile technologies.

Memory cell sizes are usually measured by the F unit, where it represents the minimum feature size accessible by lithography (IELMINI, 2016). Cell sizes are also measured considering the use of single-level cells (SLC) — which means that each memory cell can represent two different states: logical zero (false) and logical one (true). This description is necessary because NVMs have the possibility to store more than simply two different states in a single memory cell, which can be achieved by using multi-level cells (MLC). This feature greatly increases the storage capacity of memories with the penalty of increased write and read latencies (DONG; XIE, 2011; KHWA et al.,

|                                 | PCRAM         | STT-RAM        | RRAM          | DRAM        | SRAM      |

|---------------------------------|---------------|----------------|---------------|-------------|-----------|

| Minimal cell size (SLC) $(F^2)$ | 4             | 6              | 4             | 6           | 160       |

| Write latency (ns)              | $\approx 100$ | < 10           | $\approx 50$  | 20 - 50     | $\leq 2$  |

| Read latency (ns)               | 5             | 5              | 5             | 20 - 50     | $\leq 2$  |

| Operation voltage $(V)$         | 1.5 - 1.8     | 0.8 - 1.8      | 3.3 - 6.5     | 1.35 - 1.65 | 0.6 - 1.1 |

| Write current (A)               | $10^{-4}$     | $10^{-5}$      | $10^{-4}$     | $10^{-5}$   | $10^{-5}$ |

| Retention (years)               | > 10          | > 10           | > 10          | -           | -         |

| Endurance (no. of writes)       | $\leq 10^{9}$ | $\leq 10^{12}$ | $\leq 10^{6}$ | $10^{15}$   | $10^{15}$ |

Table 1 – Comparing NVM and current volatile memories (CHI; LEE; XIE, 2014; ENDOH et al., 2016; LEE, 2016)

2015).

The values described in Table 1 present many variations, since different related work shows different values. Firstly, PCRAM and RRAM cells could be developed under the smallest sizes. On the other hand, performing a write operation in these memories is costly in terms of energy and specially time. Also, RRAM is classified as a more recent technology (ENDOH et al., 2016) which has the main issue of its endurance – it is inferior in comparison with other NVMs.

As pointed out and seen in the table, all NVMs suffer from poor write endurance. Regarding energy costs, STT-RAM cells have power consumption values which are comparable to DRAM cells. Thus, in comparison with other non-volatile technologies, STT-RAM shows the best overall electrical/physical features, and it meets features that can replace both main and cache memories (KÜLTÜRSAY et al., 2013; YAZDANSHENAS et al., 2014).

Many solutions have been proposed in order to mitigate the issues found on different NVMs (DASARI; NELIS; MOSSE, 2013; MITTAL; VETTER; LI, 2015; MITTAL; VETTER, 2016), which include (i) addition of volatile technology buffers (DRAM and SRAM), (ii) relaxing retention of NVMs, (iii) adopting helpful mechanisms to analyze memory scheduling operations taking in account the asymmetry of read and write operation latencies, (iv) compiler-oriented techniques, among other techniques.

## 2.5 Conclusion

This chapter presented an overview of NVMs. Three main non-volatile technologies (the NVMs that are most promising future memories) were depicted, showing their unique features, strong and weak points. Lastly, a brief discussion was done in the sense of comparison between these NVMs plus DRAM and SRAM, highlighting the issues presented by non-volatile technologies. Lastly, some solutions proposed to mitigate NVM problems were cited, based on studied related work.

## 3 MEMORY OPERATION SCHEDULING

One of the key challenges to get better performance from actual memory technologies resides in serving read and write memory instructions in the best instance of time possible. Scheduling is considered to be a complex problem, since it needs to cope with various issues, which include (MARTINEZ; IPEK, 2009; KIM et al., 2010; GOOSSENS et al., 2016):

- Requiring circumventing access scheduling constraints;

- Prioritizing memory requests properly;

- Avoiding conflicts over memory chip devices, such as banks, row-buffers and buses;

- Efficiently deal with changes in application states, i.e., they do not generate memory operations all the time.

These issues occur over all categories of memory controllers considering actual technologies. When considering using an NVM as main memory, problems found in these memories are also issues that need to be considered by memory controllers – those include asymmetry of read and write operations, plus limited write endurance.

In order to approach these problems, some related work have proposed memory controller scheduling policies and designs that mitigate these issues, thus making it more feasible to adopt an NVM as main memory (ZHOU et al., 2011; HU et al., 2014). Other solutions include increasing of cache sizes which absorb more writes and reads that would be done over the main memories. Other solutions include the adoption of hybrid architectures, i.e., by using an NVM as main memory, there may be additional buffers (usually with current technologies) used to mitigate the impact of write operations.

Other possible solutions include the programming of memory controllers that are aware of the particular characteristics of each NVM. Thus, these controllers may perform different scheduling decisions when dealing with unequal operations (read-s/writes). When modifying memory controllers considering the use of current technologies, fixed latencies for both write and read operations are assumed – a method that is appropriate in DRAM-based-systems (DASARI; NELIS; MOSSE, 2013). However, on NVM-based systems, memory write operations are more costly on both time and energy. Hence, better timing control of scheduling memory operations may make it feasible to adopt NVM as a main memory in real-time systems. These type of systems have strict timing requirements, which include meeting operational deadlines (BURNS et al., 2015; KUMAR; KARSAI, 2015). In addition, NVMs could be also used in embedded systems, since they are usually have energy constraints (SALEHI; EJLALI, 2015). Therefore, better arrangement of memory requests is seen as an option to aid NVM-based systems. Dasari, Nelis and Mosse (2013) proposed a mechanism to help analysis of memory requests timing, which has a primary objective of estimating tight timing for memory requests taking in account of the asymmetry of read and write operations. This method is better detailed in the section below.

## 3.1 Analysis of memory requests timing mechanism

The proposed method of memory requests timing goals to make it practical to deploy real-time applications over PCRAM main memory based systems, taking in account the differences between latencies on read and write operations (DASARI; NELIS; MOSSE, 2013). In order to perform a better and more detailed analysis, some constraints on evaluated tasks (which are simply sets of one or more memory requests) have been imposed. Those include:

- Tasks cannot migrate from one core to another, in case of multiple core architectures:

- Tasks have a fixed level of priority;

- Once a task is dispatched, it must complete its execution without being interrupted or preempted;

- If a task is designed to run at a certain time, even though it completes its execution earlier, the core remains idle until that time – no matter if other jobs are waiting execution.

Including these constraints over the sets of memory requests, some limitations on individual memory operation requests were also forced.

Read requests: Once a read request has been issued by a single core, that core

cannot issue a new read request until it receives the response of the previous

request;

## • Write requests:

- Once a write request is issued, it is directed to write buffers, so that a task can proceed without waiting for the operation finishing;

- If the write queue is not full, the controller serves pending read requests in the case of having only write requests waiting to be issued, those are also served;

- When the write queue is full, all pending requests are sorted according to priority (includes both writes and reads) – and then the controller serves them until the write queue is not full.

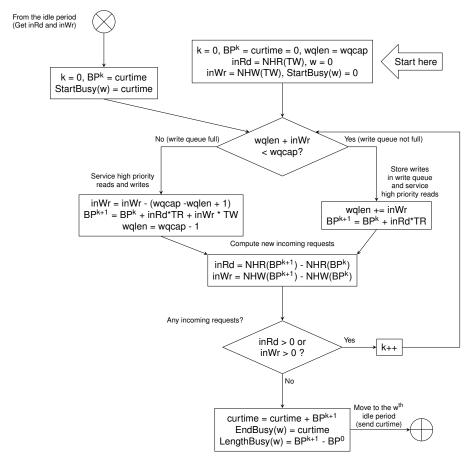

The imposed restraints over both read and write operations dictate the logic to the scheduling mechanism that is proposed. With that rationale, the memory controller can have two different states, being called the **busy** and the **idle** periods. These states can be visualized in two automata: In the **busy** automaton (shown in Figure 7), the algorithm iterates as long as memory requests can be generated. When no further requests can be generated, the algorithm switches to the **idle** automaton (depicted in Figure 8), where it waits for a memory request to be generated so that it can switch back to the busy automaton. Additionally, Table 2 contains all notations used in both automata.

Table 2 – Notations in busy and idle automata

| Notation        | Meaning                                                  |

|-----------------|----------------------------------------------------------|

| wqcap           | Write queue capacity                                     |

| wqlen           | Number of slots used in write queue                      |

| inRd            | Number of incoming read and write requests,              |

| inWr            | respectively                                             |

| k               | Iteration index and the current time respectively        |

| curtime         | , ,                                                      |

| BP <sup>k</sup> | Current time after the kth iteration in busy period      |

| ID <sup>k</sup> | and idle period, respectively                            |

| StartBusy(w)    | Stores the time at which the w <sup>th</sup> busy period |

| EndBusy(w)      | starts and ends, respectively                            |

| StartIdle(w)    | Stores the time at which the w <sup>th</sup> idle period |

| EndIdle(w)      | starts and ends, respectively                            |

| LengthBusy(w)   | Length of the w <sup>th</sup> busy and idle period,      |

| LengthIdle(w)   | respectively                                             |

| TR              | Upper bounds on the time to serve a read and a           |

| TW              | write request by the memory module                       |

The flowchart shown in Figure 7 models the controller when in busy period, where at least one read or write request needs to be issued. Once the busy period starts, the moment this happens is stored. After that, the main iteration of this period begins: It is

Figure 7 – The busy automaton (DASARI; NELIS; MOSSE, 2013)

Figure 8 – The idle automaton (DASARI; NELIS; MOSSE, 2013)

checked if the write queue is full, including the arriving of one or more incoming write requests. Two independent actions can be done depending on the condition:

• Write queue not full: The controller simply deals with pending read requests. This branch of the algorithm prioritizes read over write operations;

• Write queue full: The controller will serve both read and write pending requests according to their priority – once the write queue has available slots, the controller switches back to the reads-over-writes schema.

Taking either action, the algorithm then computes if there are any more incoming read or write memory requests. Once again, two actions can occur:

- Any incoming memory requests arrived: The controller simply increments the iteration of the busy period, and returns back to the main iteration of the algorithm;

- No incoming memory requests arrived: This denotes the end of the busy period. Some variables are set here, which include the time the busy period ends, and how long the busy period was.

When the busy period ends, then the algorithm switches to idle period, where its flowchart is seen in Figure 8.

The idle period automaton has a simple iteration. Firstly, the start of the period is stored (this occurs at the same time the busy period ends). Then, the main loop of the automaton starts, where it checks for any incoming memory requests. Two independent actions can occur depending on the condition:

- Any incoming memory requests arrived: This denotes the end of the idle period. Some variables are set here, which include the time the idle period ends, and how long the idle period was.

- No incoming memory requests arrived: The controller simply increments the iteration of the idle period, and returns back to check if any memory requests have arrived.

In short, the memory controller implementing this algorithm works by switching its state from busy to idle, and vice-versa – trying to schedule memory requests as they come, taking in account the discrepancy of write and read latencies. All of the working logic of this memory controller is essential and dictates the logic to the implementation presented on this work, which is explained in the next chapter.

## 3.2 Conclusion

This chapter showed the importance of memory controllers in computing systems, citing their main issues. Assuming the use of a NVM as a main memory, new problems in memory controllers arose – which makes scheduling of memory requests being more challenging due to natural characteristics found in NVMs.

An explanation on a method that proposes a memory controller aware of the NVM issues (specially the increased latency when performing a memory write operation) was done. This method is the base to the development of this work, as it will be seen in the next chapter.

# 4 MEMORY CONTROLLER FOR NON-VOLATILE MEMO-RIES

Based on both subjects studied, NVMs and scheduling of memory operations, this work shows an implementation of a memory controller in simulation for NVM-based systems. In order to do this, a controller was implemented and tested considering previous analyses of memory controllers and NVMs. This Chapter explains the main contribution of this work (Section 4.1), then showing how it was done: Section 4.2 shows the tools used for this work (NVMain and Gem5) and Section 4.3 explains the implementation of a memory controller directed for NVMs. Lastly, Section 4.4 concludes the Chapter.

## 4.1 Main Contribution

Previous analysis show that taking the NVM characteristics in account could reach better results. However, these studies were done based on memory operation traces of applications, which means the analysis were done following two steps:

- 1. Applications were run in order to generate traces of memory operations, keeping track of its type (read or write) and instance of time that it executed;

- Based on the type and time of operation, a static analysis over the traces was done so that it could be possible to evaluate where it was possible to get improvements in memory operations.

Hence, it was important to extend that analysis to the runtime, i.e., letting memory controller decide the scheduling while an application is being executed. By implementing a memory controller, it was possible to perform the runtime analysis which previous work (DASARI; NELIS; MOSSE, 2013) did not have. With dynamic analysis, it was possible to evaluate the behavior of the controller as the requests arrived – allowing for more realistic results on simulations.

Additionally, with three different NVMs studied, the implemented memory controller had to be tested with different non-volatile technologies. Each NVM has its particu-

lar characteristics, hence the impact of memory controllers in a specific NVM can be different if comparing with another NVM.

Different behavioral analyses of the implemented memory controller were done. The evaluated features included (i) time spent in generating memory requests, (ii) use of memory request queues, (iii) latencies of read operations considering different non-volatile technologies and (iv) comparison with NVMain default memory controllers.

#### 4.2 NVMain and Gem5

To make this work feasible, two tools were used. An NVM simulator was necessary in order to implement the different memory controller that is being proposed. For this, NVMain (POREMBA; XIE, 2012) was chosen. The Gem5 (BINKERT et al., 2011) simulator was also chosen to aid the development of the work, because NVMain can be used in conjunction with Gem5 to provide closer to full system simulation.

The NVMain simulator (POREMBA; XIE, 2012) is a tool that is introduced to help the community on the modeling of both commodity DRAMs but also emerging memory technologies, which include NVMs. It is an architectural-level simulator for both types of main memory, which can model energy plus cycle-accurate operation of DRAMs and NVMs – including hybrid designs. It is considered more of a higher-level simulator, since it is more interested in the set of cells that compose the main memory, which is the hierarchy of columns, rows, banks, ranks and channels.

This tool was programmed using C++, and it has its source code available in an online repository (POREMBA, 2012), which can be given permission to get if one contacts the author (POREMBA, 2015). The current version of NVMain (2.0) added more features to support both main memory simulations, which include fine-grained memory bank model, MLC support, more flexible address translation and hooks to encourage users to explore new memory system designs (POREMBA; ZHANG; XIE, 2015).

The reasons to choose NVMain as the NVM simulator include its continuous updates over the years that keeps itself up-to-date with technology improvements. NVMain also has well documented code, and it is flexible enough to implement different memory controllers, hierarchies, prefetchers, and other memory objects used in the tool. Another key factor to choose NVMain resides in its possibility to merge itself with the general-purpose simulator Gem5, where it can provide closer to full system simulation – by using only NVMain itself, it is only feasible to perform trace simulations.

Gem5 (BINKERT et al., 2011) is a general-purpose simulator which merges some aspects of two tools: M5 and GEMS simulators – as both tools were used in many previous publications. Gem5 aims to be a community tool focused on architectural modeling, providing flexibility on different CPU, memory and interconnect models.

This tool is implemented mostly under the C++ language, with some parts pro-

grammed using Python. The source code of Gem5 is also freely available on an online repository. (BINKERT, 2012). Besides the integration with NVMain as an important factor to choose Gem5, its constant updates and fixes are also significant to pick this tool. Gem5 is also used in a myriad of published work, which makes itself relevant to the academia.

## 4.3 Memory Controller Implementation

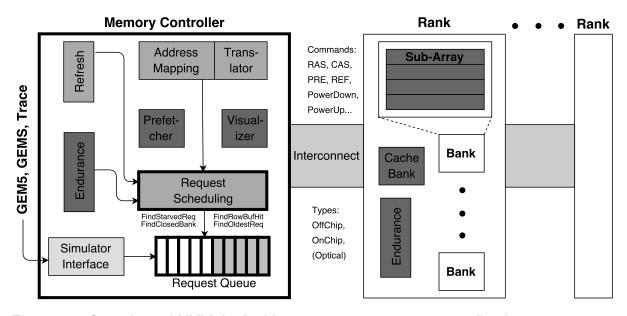

With the chosen tools, a memory controller was coded in order to evaluate it, and then comparing with already implemented NVMain memory controllers to check its performance. Firstly, an understanding of the NVMain architecture is presented. An overview of the high-level design of NVMain is shown in Figure 9. Each box presented in the figure represents a memory base object, which represents either functions or classes in the source code of NVMain. In order to develop a different memory request scheduler, the boxes with **thicker** borders are considered to be the key objects.

Figure 9 – Overview of NVMain Architecture: one memory controller for one memory channel (POREMBA; ZHANG; XIE, 2015)

In the NVMain source code context, Memory Controller is a base class with preimplemented methods, called MemoryController. This class also extends from a superclass called NVMObject, which portrays a memory base object. In order to create a new memory controller, it is necessary to create a new class based on MemoryController. NVMain already comes with some main memory controllers for testing purposes, which are based on the simple schema of FCFS (First come first served) algorithm, which shows the basic idea of how a memory controller can deal with memory requests. The first important step to set up a new memory controller is its internal variables. Table 3 shows the variables used in the implementation. Variable state determines what state is the memory controller, working like the two possible states a memory controller can have in the mechanism explained in Section 3.1. — when busy, it is in a state where memory requests are being generated, which means there is still a memory request waiting in a queue to be issued. When the state is idle, the memory controller does not have requests in a queue. When a state changes, the instance of time of this event is registered, using the variables startBusy, endBusy, startIdle and endIdle. Their variable types are paired with the one used to register instances of time (in NVMain they are called cycles), so an unsigned, 64-bit integer is used.

Type Variable Purpose state Controls what state memory controller is (Busy bool or idle). Instance of time that the busy state started. uint64\_t startBusy Instance of time that the busy state ended. uint64 t endBusy Instance of time that the idle state started. uint64 t startIdle Instance of time that the idle state ended. uint64 t endIdle How many queues memory controller has. This int queueNumber is always 3. Maximum size of write request queue, in slots. int writeQueueSize Maximum size of read request queue, in slots. int readQueueSize extraQueueSize Maximum size of extra request queue, in slots. int By default, this is the sum of writeQueueSize

Table 3 – Internal parameters used in custom memory controller

Variable queueNumber has a constant value – it is always 3, since it denotes how many queues are used in the memory controller. There are read and write queues, which simply are reserved to keep read and write memory requests respectively. In addition, there is an extra queue that is able to receive both read and write requests, only used when the write queue becomes full. The role of this queue will be discussed in detail further.

and readOueueSize

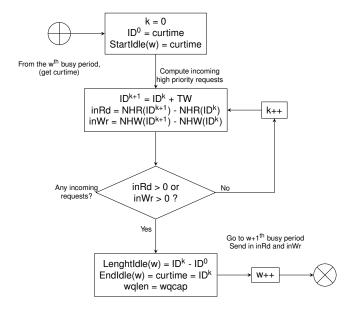

The next step of implementation is the definition of the working logic of the memory controller. In this work, some diagrams were drawn in order to show this logic, using some notations to show the actions the controller takes. Table 4 summarizes all notations used on Figures 10–12.

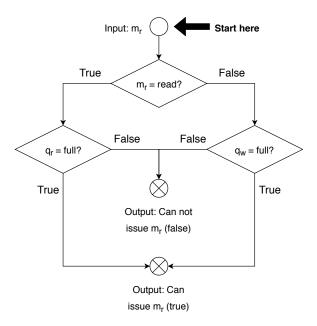

The next step of implementation is based off from already established memory controllers — a method called IsIssuable. This method simply receives a memory request and returns a boolean value that indicates whether the request can be issued or not. Figure 10 shows a diagram of the IsIssuable method. If the request that arrives is a read from memory, it checks if the read queue is not full. In case this is

| Notation             | Description                                                   |  |  |

|----------------------|---------------------------------------------------------------|--|--|

| $m_r$                | A main memory request                                         |  |  |

| $q_r$                | Queue used to hold read main memory requests                  |  |  |

| $q_{w}$              | Queue used to hold write main memory requests                 |  |  |

| enqueue $(q_x, m_r)$ | Method to enqueue a main memory request in a queue,           |  |  |

|                      | where $x = \{r, w\}$                                          |  |  |

| state                | The state the controller is currently in. Can be busy or idle |  |  |

| $q_e$                | Extra queue which is used when qw is full                     |  |  |

| $findRequest(q_x)$   | A method that tries to retrieve a memory request from a       |  |  |

|                      | queue, where $x = \{r, w, e\}$                                |  |  |

Table 4 – Notations used in the diagrams of the memory controller

true, the request can be issued. However, when that queue is full, it cannot accept more requests, thus returning false. The same logic works for the arrival of a write request — it checks for the write queue instead. This method is implemented here since the base method IsIssuable from MemoryController always returns true, i.e., a memory request can be always issued. However, since memory requests need to be put in a queue, it may be already full. Thus, this method can inform that the memory request cannot be issued.

Figure 10 – Diagram to check if a memory request can be issued based on the request queue capacity (IsIssuable method)

When a request can be issued, it has to be put in its respective queue so that the scheduler can organize what memory requests will turn into operations. Method IssueCommand is responsible for these actions, and its diagram is depicted in Figure 11. The first action taken by IssueCommand is call the previously explained method IsIssuable in order to check if a memory request can be issued. If it cannot be issued, then the methods stop its execution. Else, the controller is ready to put a request in its

Input: m<sub>r</sub> Start here False IsIssuable? Output: Can not True issue m<sub>r</sub> (false) True False  $m_r = read?$ enqueue(q<sub>r</sub>, m<sub>r</sub>) enqueue(q<sub>w</sub>, m<sub>r</sub>) False state = idle? True state = busy Output: Issued and enqueued m<sub>r</sub> (true)

respective queue, depending of the type of the request.

Figure 11 – Diagram that checks if a memory request will be issued (IssueCommand method)

Additionally, here the memory controller can change its state. This can occur when the controller is in idle state, which represents no memory requests being generated. However, if this method is called and a memory request was enqueued, it is necessary to change the state to the busy one. The instance of time this occurred is registered – where the busy state started and the idle state ended. After changing the state, IssueCommand ends its execution successfully.

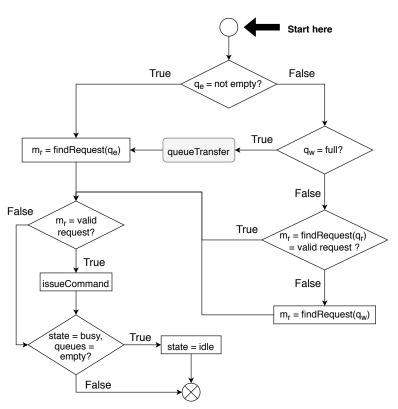

The next implemented method, named Cycle is also extended from the MemoryController class, and it looks for enqueued memory requests. Its diagram is shown in Figure 12. The first step of this method is to check if the extra queue is not empty, which is always true when the controller receives the first main memory request. In this case, the controller will then check if the write queue is full of requests — firstly, it is assumed that this case does not occur. Considering that, the controller then tries to get a request from the read queue. If not possible, the code then tries to retrieve a memory request from the write queue. Thus, the scheduler prioritizes read requests over write requests.

Eventually, when attending many read requests the write queue may be filled with requests. When this occurs, all stored write requests have to be attended. In this case, the method called queueTransfer is executed. This takes all requests from both read and write queues to the extra queue, following this procedure:

- 1. All requests from both write and read queues are removed from their respective queues;

- 2. These requests are sorted by priority. It is considered that a request which arrived earlier in a queue has a higher priority than another request that was enqueued later;

- 3. The sorted requests are put in the extra queue, ending the method execution.

The last case that can attend a memory request occurs when there is at least one request that can be retrieved from the extra queue. The extra queue gets the priority over all other queues, since it represents the attending of all requests when the write queue is full.

Figure 12 – Diagram that schedules requests and turn them into operations (Cycle method)

In any of the cases explained before, the algorithm will try to get a memory request using the method findRequest, which can store either a valid memory request or a null value. After trying to retrieve a memory request from any queue, the controller will check if the request gotten is valid or not. If it is valid, then the next step is to turn it into a memory operation, which is done by calling an already implemented MemoryController method called IssueMemoryCommands.

Lastly, after performing the memory operation the controller may change its state. This is possible whenever the controller is in busy state and all queues are empty. This

means no memory requests were generated to be scheduled, so the state is changed to the idle one. The time of this event is registered, denoting the start of idle state and the end of busy state. Finally, Cycle ends its execution.

Considering the work logic of the implemented memory controller, the code for it was developed and inserted in NVMain. It is important to point that any technology of memory can be simulated using this controller. This is possible since in order to perform an execution using a certain memory technology, a configuration file describing the memory needs to be specified. In addition to that, NVMain already comes with examples of memory technologies that can be executed.

## 4.4 Conclusion

This Chapter pointed the need of expanding timing analysis of memory requests in systems with an NVM as a main memory – runtime analysis is preferred over static analysis. The Chapter explained the main contribution of this work, and how it was reached – which was possible to use NVMain and Gem5 tools were chosen, since they can work together to reach the desired results.

Additionally, this chapter presented how the analysis of Section 3.1 could be translated in a practical environment – which was possible to do by coding a custom memory controller in NVMain, so that it could be attached to Gem5, turning it possible to perform a runtime behavior analysis.

## 5 RESULTS

This Chapter shows the main results reached by this work. With the modifications performed to include the implemented memory controller, both simulators were configured. This is explained in Section 5.1. Then, a set of applications were chosen to run in the simulator. For this job, two sets of benchmarks were picked: MiBench (LEE; POTKONJAK; MANGIONE-SMITH, 1997) and MediaBench (GUTHAUS et al., 2001). Applications were tested and selected to evaluations of the memory controller. In addition to that, some changes in the input data were performed to reflect more realistic and stressful executions – this is explained in Section 5.2. Then, a profiling of the chosen benchmarks was done and explained in Section 5.3. In Section 5.4 the behavioral analyses of the implemented memory controller were exposed. Section 5.5 compares the implemented memory controller with NVMain default memory controllers, and lastly, Section 5.6 concludes the Chapter.

# 5.1 Simulation configurations

In order to obtain results, it is important to highlight the configurations of the tools. On Gem5, one of the configuration relates to memory hierarchy. For all simulations it was considered the use of two levels of cache, reflecting default configurations found on Gem5. Firstly, the L1 cache is composed of two caches: a 32KB cache for instructions, plus a 32KB cache for data. Then, there is a L2 cache with 2MB. The CPU used on simulation was the TimingSimpleCPU, which reflects a simple model of a CPU, which uses timing memory accesses. This model connects the CPU to the cache, defining the necessary functions to handle memory accesses, which allowed to perform a better merge with NVMain memory system. Furthermore, Gem5 was compiled using the fast option, which allowed for code optimization and better performance and the instruction set architecture (ISA) x86 was used.

With NVMain, parameters regarding the main memory system were set. For each NVM technology, the original configuration files for each memory (PCRAM, RRAM and STT-RAM) were used. However, some changes in the general memory system config-

uration were done regarding the main memory schema. All NVMs followed the same schema found in the PCRAM configuration file – this was done in order to allow tests under the same memory system configuration, preserving its natural characteristics, which include device timing parameters and energy parameters. These parameters were extracted from (CHOI et al., 2012) (PCRAM), (KAWAHARA et al., 2012) (RRAM) and (EVERSPIN, 2015) (STT-RAM).

The implemented memory controller also had parameters which needed to be defined in order to perform tests. Since the memory controller is based on memory requests queues, they needed to have limited sizes. Observing the already implemented memory controllers on NVMain, the default queues could hold 16 requests – a value maintained in the implemented memory controller for both read and write queues. For the extra queue, it was used a queue which could hold 32 requests, as it can potentially hold all requests from both write and read queues due to the scheduling used in the memory controller.

# 5.2 Benchmark checking and manipulation

Firstly, a check-up of the applications of both sets of benchmarks was done — Table 5 summarized each application status, pointing out if the application could be compiled and executed. Applications that occurred in both sets of benchmarks (cases of adpcm, ghostscript, jpeg and pgp) were only shown in the MediaBench benchmark set. Some of the benchmarks have multiple execution stages, which are either decode/encode (decodification/codification stages) or a specific process (Applications mesa and susan have three different forms of execution, each one with a specific functionality). The majority of benchmarks executed normally, with some exceptions that need to be pointed out:

- ghostscript had some incompatibilities with some library files, which were fixed on compilation. However, it gives a segmentation fault error when running. This probably occurred due to the use of old libraries that are no longer supported;