# UNIVERSIDADE FEDERAL DE PELOTAS Centro de Desenvolvimento Tecnológico Programa de Pós-Graduação em Computação

Dissertação

An Energy-Efficient Hardware Design for the 3D-HEVC Motion Estimation Adopting Reuse Strategies for Data and Operations

**Murilo Roschildt Perleberg**

# **Murilo Roschildt Perleberg**

An Energy-Efficient Hardware Design for the 3D-HEVC Motion Estimation

Adopting Reuse Strategies for Data and Operations

Dissertação apresentada ao Programa de Pós-Graduação em Computação do Centro de Desenvolvimento Tecnológico da Universidade Federal de Pelotas, como requisito parcial à obtenção do título de Mestre em Ciência da Computação.

Advisor: Prof. Dr. Marcelo Schiavon Porto

Coadvisors: Prof. Dr. Luciano Volcan Agostini

Prof. Dr. Vladimir Afonso

# Universidade Federal de Pelotas / Sistema de Bibliotecas Catalogação na Publicação

P426a Perleberg, Murilo Roschildt

An energy-efficient hardware design for the 3D-HEVC motion estimation adopting reuse strategies for data and operations / Murilo Roschildt Perleberg; Marcelo Schiavon Porto, orientador; Luciano Volcan Agostini, Vladimir Afonso, coorientadores. — Pelotas, 2020.

88 f.: il.

Dissertação (Mestrado) — Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, 2020.

1. Hardware design. 2. Motion estimation. 3. 3D-HEVC. 4. Operations reuse. 5. Data reuse. I. Porto, Marcelo Schiavon, orient. II. Agostini, Luciano Volcan, coorient. III. Afonso, Vladimir, coorient. IV. Título.

CDD: 005

#### **Murilo Roschildt Perleberg**

# An Energy-Efficient Hardware Design for the 3D-HEVC Motion Estimation Adopting Reuse Strategies for Data and Operations

Dissertação aprovada, como requisito parcial, para obtenção do grau de Mestre em Ciência da Computação, Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas.

Data da Defesa: 6 de abril de 2020

#### **Banca Examinadora:**

Prof. Dr. Marcelo Schiavon Porto (orientador)

Doutor em Computação pela Universidade Federal do Rio Grande do Sul, Brasil.

Prof. Dr. Leomar Soares da Rosa Jr.

Doutor em Microeletrônica pela Universidade Federal do Rio Grande do Sul, Brasil.

Prof. Dr. Felipe Martin Sampaio

Doutor em Computação pela Universidade Federal do Rio Grande do Sul, Brasil.

Prof. Dr. Sergio Bampi

Doutor em Engenharia Eletrica Microeletronica pela Stanford University, Estados Unidos.

## **AGRADECIMENTOS**

Agradeço aos meus pais, Marilene Roschildt Perleberg e Almiro Perleberg, e também aos demais familiares, por toda a motivação para que eu mantivesse o foco nos estudos após a graduação, além de sempre me apoiaram e acreditaram no meu sucesso.

Agradeço imensamente a minha namorada e companheira, Analice Megiato da Silva, por estar comigo tanto nos momentos felizes como também por ter me aguentado nos diversos momentos conturbados do mestrado.

Agradeço aos meus orientadores, Marcelo Porto, Luciano Agostini, Vladimir Afonso, e também ao professor Bruno Zatt, por todo o auxilio e idéias compartilhadas que possibilitaram o desenvolvimento deste trabalho.

Ainda, agradeço aos diversos amigos e colegas de grupo, tanto do ViTech como do GACI, por toda a ajuda e conhecimento compartilhado, além dos diversos momentos de descontração que guardo na memória. Vocês são fera piazada! #12

Follow the party.

— Gaucho Proverв

## **ABSTRACT**

PERLEBERG, Murilo Roschildt. An Energy-Efficient Hardware Design for the 3D-HEVC Motion Estimation Adopting Reuse Strategies for Data and Operations. Advisor: Marcelo Schiavon Porto. 2020. 88 f. Dissertation (Masters in Computer Science) – Technology Development Center, Federal University of Pelotas, Pelotas, 2020.

Currently, there is a growing demand for video streaming through the internet, and also a crescent number of portable devices capable of capture and reproduce those videos. Moreover, the 3D videos allow an improved user experience when compared with traditional videos, since in the 3D videos the scene is simultaneously captured from different points of view. However, due to the amount of data required to represent digital videos, compression techniques are mandatory, which are a series of tools responsible for reducing the redundancies present in video data. 3D-High Efficiency Video Coding (3D-HEVC) standard, the most complex tool is the Motion Estimation (ME), while it is also responsible for a huge part of the compression efficiency of this standard. The ME is divided in Integer ME (IME), which performs the comparison a block from the frame being encoded with several candidate blocks from already encoded frames, searching for the candidate block most similar with the block being encoded, and the Fractional ME (FME), which performs a refinement around the candidate result of the IME. By default, the 3D-HEVC adopts the Test Zone Search (TZS) algorithm to select the candidates to be evaluated in the IME, since the TZS evaluates a reduced number of candidates without result in huge losses in image quality when compared with a full search algorithm, which compares all possible candidate blocks. Also, in 3D-HEVC the IME was applied in up to 24 different block sizes. This implies several redundant operations, where parts from a specific candidate can be compared with part of the block being encoded several times, besides a huge memory communication to perform the processing of several block sizes of each candidate block. Aiming at reducing these operation redundancies, it is possible to reuse the operations performed to small block sizes to compose the result of higher block sizes. This strategy also allows data reuse, since it reduces the memory access needed to obtain the samples to process all block sizes. There have only a few works on literature proposing hardware architectures for the IME of the 3D-HEVC standard. Between the IME works of other video coding standards, only a few presents solutions considering data and operations reuse strategies and a fast algorithm as TZS. Therefore, this work presents an IME hardware design adopting the TZS algorithm, with support to all block sizes supported by 3D-HEVC standard and with operations and data reuse strategies to take advantage of already processed

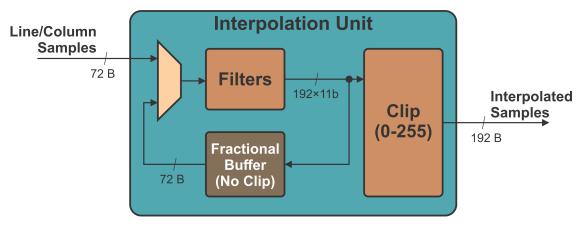

operations and reduce the memory communication. The 3D-HEVC IME algorithm was modified aiming at an efficient hardware implementation, and the evaluations show that these modifications present an increase of 9.016% in the BD-rate metric. The developed IME architecture was synthesized for an ASIC with TSMC 40nm standard cells technology, and the results show that the hardware requires 269 K gates, while dissipates 108.48 mW when processing 3 views from different cameras, where each view is composed by the video of the two channels (Texture and Depth Maps) with FHD 1920x1080p resolution with 30 frames per second. The synthesis results have also indicated that the IME hardware design can process up to 3 views with UHD 3840x2160p resolution with 60 frames per second. Moreover, an FME architecture was also presented, which is able to evaluate all possible 48 fractional blocks around the IME result.

Keywords: Hardware Design. Motion Estimation. 3D-HEVC. Operations Reuse. Data Reuse.

## **RESUMO**

PERLEBERG, Murilo Roschildt. Uma arquitetura de Hardware Energéticamente Eficiente para a Estimação de Movimento do padrão 3D-HEVC Adotando Estratégias de Reúso de Dados e de Operações. Advisor: Marcelo Schiavon Porto. 2020. 88 f. Dissertation (Masters in Computer Science) — Technology Development Center, Federal University of Pelotas, Pelotas, 2020.

Atualmente existe uma grande demanda por streaming de vídeos digitais através da internet, além de um crescente número de dispositivos móveis capazes de gravar e reproduzir estes vídeos. Além disso, vídeos em 3 Dimensões (3D) permitem ainda uma experiência maior do usuário se comparado com os videos tradicionais, visto que nos videos 3D a cena é capturada de pontos de vista diferentes. Contudo, devido a grande quantidade de dados necessários para representar os vídeos digitais, técnicas de compressão se tornam obrigatórias, as quais são uma série de ferramentas responsáveis por reduzir as redundâncias presentes nos dados dos vídeos. padrão 3D-High Efficiency Video Coding (3D-HEVC), a etapa mais complexa é a Estimação de Movimento (ME), a qual é também a etapa responsável por grande parte da eficiência de compressão deste padrão. A ME é divida em Estimação de Movimento Inteira (IME), a qual realiza a comparação de um bloco do quadro que está sendo codificado com diversos blocos candidatos de quadros já codificados em busca do bloco candidato mais similar ao bloco sendo codificado, e a Estimação de Movimento Fracionária (FME), a qual realiza um refinamento sobre o candidato resultante da IME. Por padrão, o 3D-HEVC utiliza o algoritmo *Test Zone Search* (TZS) para escolher os candidatos a serem avaliados pela IME, visto que o TZS realiza a avaliação de um número reduzido de candidatos sem resultar em grandes perdas na qualidade da imagem quando comparado com o algoritmo de busca completa, que avalia todos os blocos possíveis. Além disso, no 3D-HEVC a ME pode ser aplicada sobre blocos de até 24 diferentes tamanhos. Isso implica na ocorrência de diversas operações redundantes, onde uma parte de um dos blocos candidatos pode ser comparada com uma parte do bloco sendo codificado inúmeras vezes, além de uma enorme comunicação com a memória para realizar o processamento dos diferentes tamanhos de bloco de cada bloco candidato. Visando a redução das operações redundantes, é possível reutilizar as operações realizadas em blocos pequenos para compor o resultado dos blocos maiores. Esta estratégia também permite o reuso de dados, visto que será reduzindo o número de acessos a memória necessários para obter as amostras de todos os tamanhos de bloco. Existem apenas poucos trabalhos na literatura propondo arquiteturas de hardware para a IME do padrão 3D-HEVC. Dos trabalhos de IME para outros padrões de codificação, apenas poucos apresentam

soluções considerando estratégias de reuso de dados e operações e um algoritmo rápido como o TZS. Portanto, este trabalho apresenta uma arquitetura de IME adotando o algoritmo TZS, com suporte a todos os tamanhos de bloco suportados pelo 3D-HEVC e utilizando estratégias de reuso de operações para obter vantagem das operações já processados. O algoritmo de IME do 3D-HEVC foi alterado visando uma implementação de hardware eficiente, e experimentos mostraram que essas modificações apresentam um aumento de 9,016% na métrica BD-rate. A arquitetura de IME desenvolvida foi sintetizada para ASIC utilizando a biblioteca de células padrão de 40nm da TSMC, e os resultados mostraram que a arquitetura requer 269 K gates, enquanto dissipa 108,48 mW quando processa 3 vistas de diferentes câmeras, sendo cada vista é composta pelo video dos 2 canais (textura e mapas de profundidade) com resolução de FHD 1920x1080p com 30 quadros por segundo. Os resultados de síntese também mostraram que a arquitetura de IME é capaz de processar até 3 vistas com resolução UHD 3840x2160p e com uma taxa de mostragem de 60 quadros por segundo. Além disso, uma arquitetura de FME também é apresentada, capaz de avaliar todos os 48 possiveis blocos fracionarios ao redor do resultado da IME.

Keywords: Arquitetura de Hardware. Estimação de Movimento. 3D-HEVC. Reuso de Operações. Reuso de Dados.

# **LIST OF FIGURES**

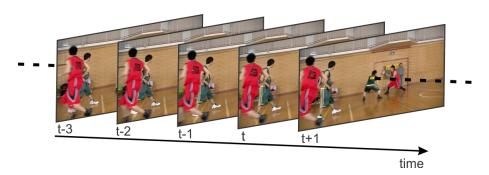

| Figure 1<br>Figure 2 | Sequence of frames that compose a digital video                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 21             |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

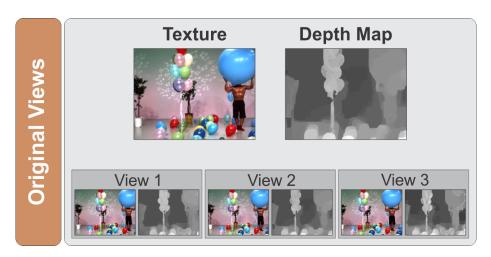

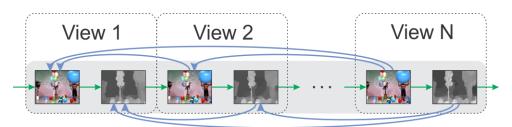

| 9                    | same scene                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 24             |

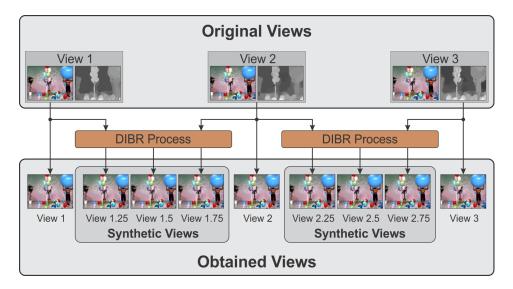

| Figure 3             | DIBR process to generate intermediary texture views                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 24             |

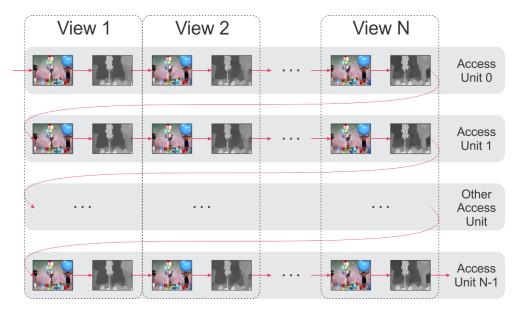

| Figure 4             | Sequence of Access Units to be encoded                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25             |

| Figure 5             | Normal Coding Orders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 25             |

| Figure 6             | Flexible Coding Orders                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 25             |

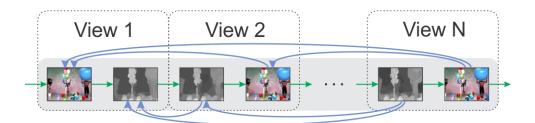

| Figure 7             | Encoding flow of 3D-HEVC standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 26             |

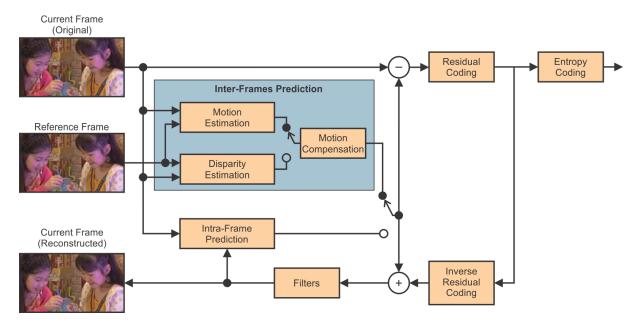

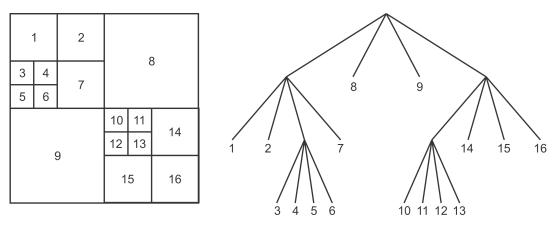

| Figure 8             | Example of the splitting of one CTU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 27             |

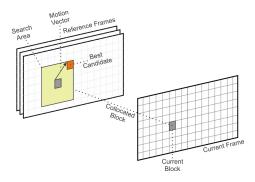

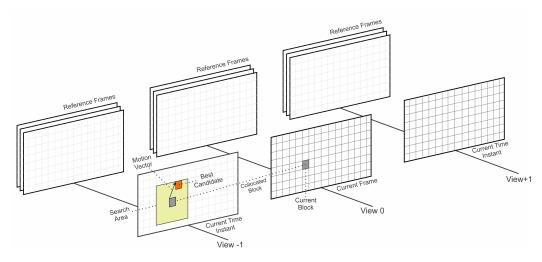

| Figure 9             | Motion Estimation Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 28             |

| Figure 10            | Disparity Estimation Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 29             |

| Figure 11            | Neighboring blocks information available for AMVP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 31             |

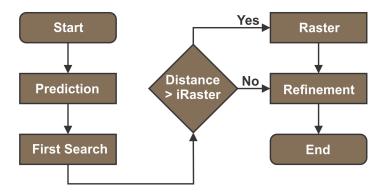

| Figure 12            | Flowchart of TZS steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 33             |

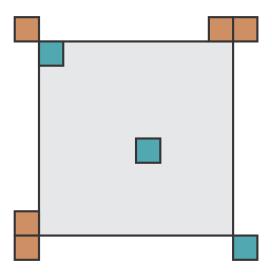

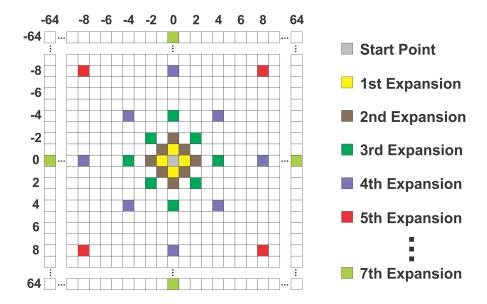

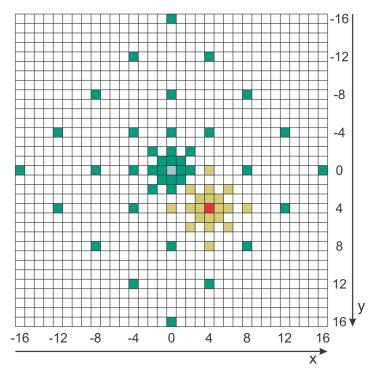

| Figure 13            | Expansive diamond scheme adopted by TZS algorithm to selects                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 00             |

| rigule 13            | the candidate blocks for evaluation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 34             |

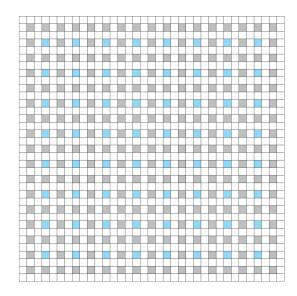

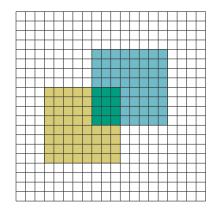

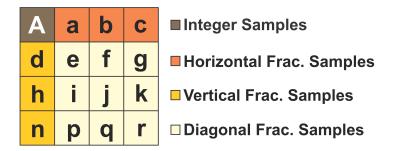

| Figure 14            | Fractional samples around a $8x8$ block size. Blue samples represent                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | J <del>4</del> |

| rigule 14            | the integer $8x8$ block, while gray and white samples represent the                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

|                      | fractional samples generated at half and quarter position                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 36             |

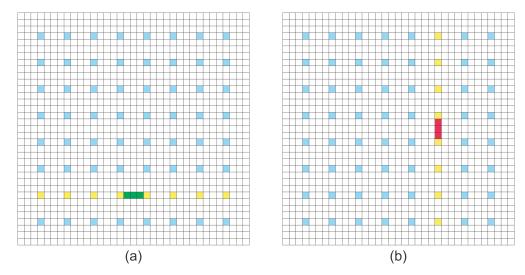

| Figure 15            | Input samples (yellow squares) required for generating the fractional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 30             |

| rigule 15            | samples (green and red squares)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37             |

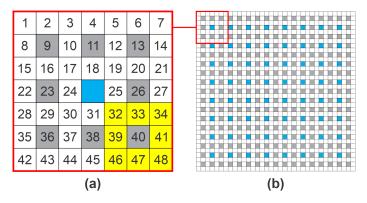

| Figure 16            | FME algorithm assuming that the best half block is the block 40                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 37             |

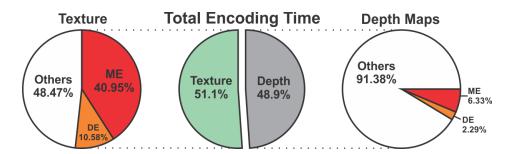

| Figure 17            | Encoding time portions of prediction steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 38             |

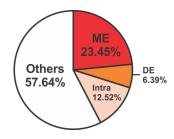

| Figure 18            | Accumulated encoding time portions of prediction steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 39             |

| rigule 16            | Accumulated encoding time portions of prediction steps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 39             |

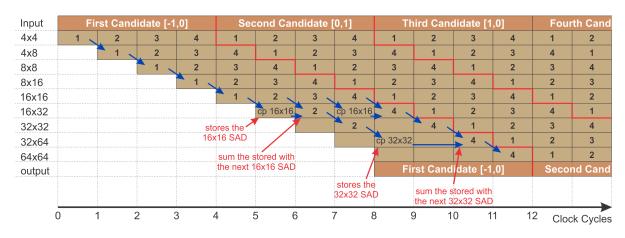

| Figure 19            | TZS processing: Candidates from the First Search and from the first                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                |

| _                    | Refinement                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 50             |

| E: 00                | The state of the s |                |

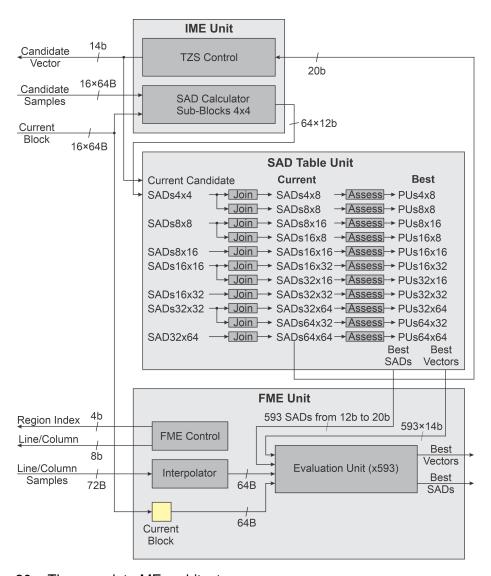

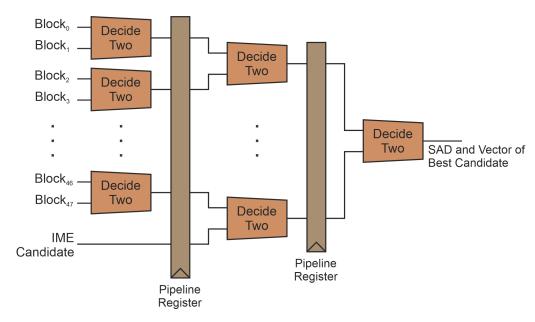

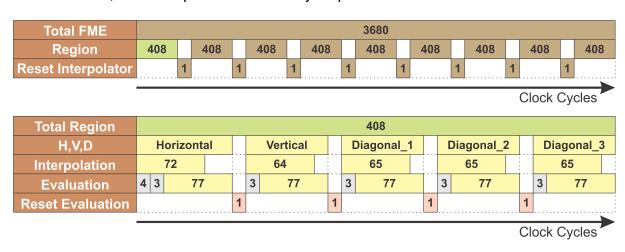

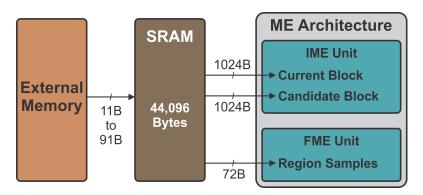

| Figure 20            | The complete ME architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 57             |

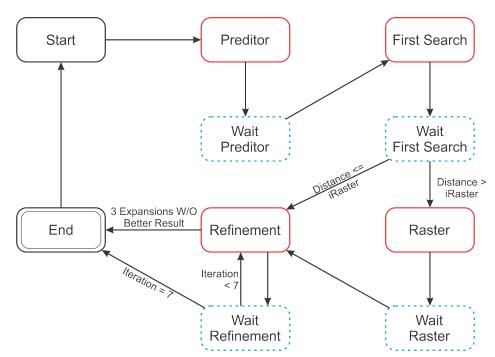

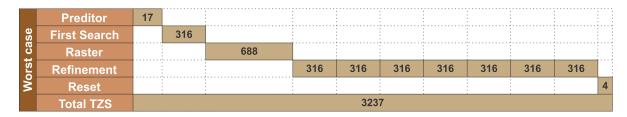

| Figure 21            | Finite State Machine that process the TZS algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 58             |

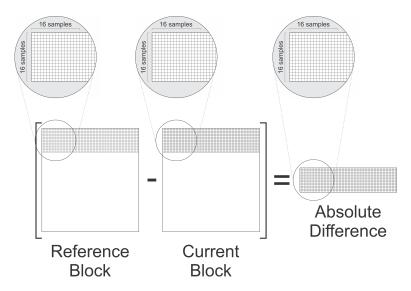

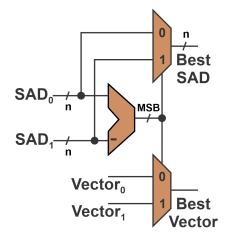

| Figure 22            | Scheme for obtaining the Absolute Difference between Reference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                |

| <b>-</b> : 00        | and Current Blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 59             |

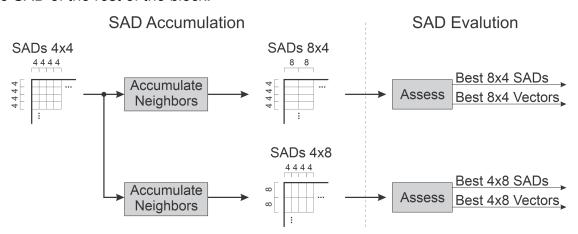

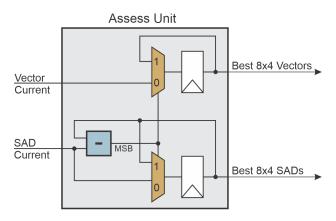

| Figure 23            | Scheme that join the Absolute Difference between two neighboring                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                |

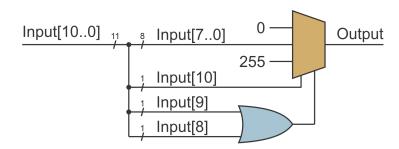

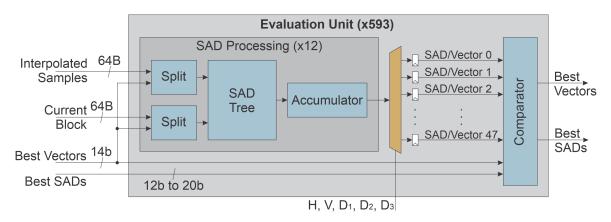

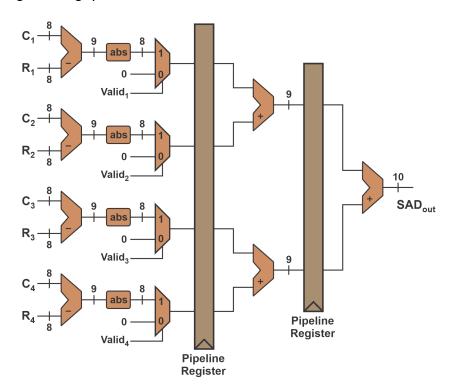

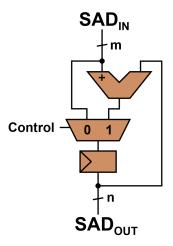

|                      | samples to obtain the SAD of $4x4$ sub-blocks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 59             |