# UNIVERSIDADE FEDERAL DE PELOTAS Programa de Pós-Graduação em Computação

Tese

SmartDR: Algorithms and Techniques for Fast Detailed Routing with Good Design Rule Handling

Stèphano M. M. Gonçalves

## Stèphano M. M. Gonçalves

# SmartDR: Algorithms and Techniques for Fast Detailed Routing with Good Design Rule Handling

Tese apresentada ao Programa de Pós-Graduação em Computação da Universidade Federal de Pelotas, como requisito parcial à obtenção do título de Doutor em Ciência da Computação.

Orientador: Felipe de Souza Marques

Co-Orientador: Leomar Soares da Rosa Jr.

# Universidade Federal de Pelotas / Sistema de Bibliotecas Catalogação na Publicação

G635s Gonçalves, Stèphano Machado Moreira

Smartdr: algorithms and techniques for fast detailed routing with good design rule handling / Stèphano Machado Moreira Gonçalves; Felipe de Souza Marques, orientador; Leomar Soares da Rosa Jr., coorientador. — Pelotas, 2020. 130 f.: il.

Tese (Doutorado) — Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, 2020.

1. Roteamento detalhado. 2. Acesso a pinos. 3. Busca de caminhos. 4. Regras de projeto. 5. ISPD 2018 Contest. I. Marques, Felipe de Souza, orient. II. Jr., Leomar Soares da Rosa, coorient. III. Título.

CDD: 005

## Stèphano M. M. Gonçalves

| SmartDR: Algorithms and | Techniques for F | Fast Detailed | Routing with | h Good |

|-------------------------|------------------|---------------|--------------|--------|

|                         | Design Rule Har  | ndling        |              |        |

Tese aprovada, como requisito parcial, para obtenção do grau de Doutor em Ciência da Computação, Programa de Pós-Graduação em Computação, Universidade Federal de Pelotas.

Data da Defesa: 15 de janeiro de 2020

#### Banca examinadora:

Prof. Dr. Felipe de Souza Marques (Orientador, PPGC UFPEL)

Prof. Dr. Leomar Soares da Rosa Jr. (Co-Orientador, PPGC UFPEL)

Prof. Dr. Bruno Zatt (PPGC UFPEL)

Prof. Dr. Marcelo Johan (UFRGS)

Dr. Renato Fernandes Hentschke (Intel)

#### Resumo

GONÇALVES, Stèphano Machado Moreira. SmartDR: Algorithms and Techniques for Fast Detailed Routing with Good Design Rule Handling. 2020. 130p. Tese (Doutorado em Ciência da Computação) — Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, Pelotas, 2020.

O roteamento detalhado é uma das etapas mais desafiadoras e demoradas do projeto de circuitos integrados. A solução do roteamento deve obedecer a todas as regras de projeto para que o circuito possa ser corretamente fabricado. No entanto, o tratamento de regras de projeto pode ser muito desafiador, quanto a suas soluções algorítmicas e sua implementação, e pode facilmente levar a tempos de execução inviáveis. Para tornar a resolução do roteamento detalhado mais factível, ele é dividido em duas etapas, onde, na primeira, chamada de roteamento detalhado inicial, uma solução quase completa é obtida mediante a flexibilização das regras de projeto. Na segunda etapa as violações remanescentes de regras de projeto são resolvidas. No entanto, quanto mais o tratamento dessas regras é deixado para a segunda etapa, maior é a chance de elas não serem resolvidas completamente, e isto costuma ocorrer. Assim, é necessário enfrentar o desafio de lidar com o maior número possível de regras na etapa inicial sem comprometer o desempenho do roteamento. Dessa forma, este trabalho propõe um roteador detalhado inicial, chamado SmartDR, para atender essas necessidades, isto é, apresentar uma boa lida com regras de projeto ao mesmo tempo que mantendo um bom desempenho. As principais características do roteador, que atendem a esses objetivos, são técnicas de acesso a pinos e de busca de caminhos. Este trabalho propõe um novo método de acesso a pinos, em que os caminhos de acesso a pinos compartilham os mesmos recursos de roteamento e são legalizados e implementados dinamicamente. Também é proposto um novo algoritmo de busca de caminhos, baseado na busca A\* com intervalos, o qual é ciente de várias regras de projeto. É proposto também um novo método para melhorar a função heurística da busca A\* levando em consideração peculiaridades do roteamento detalhado, o que leva a um melhor desempenho. Utilizando os benchmarks da competição ISPD 2018, todos os métodos propostos foram avaliados separadamente e em conjunto no roteador proposto, o qual foi comparado com os roteadores estado-da-arte. Os experimentos mostram que as técnicas propostas contribuem para uma melhoria em desempenho e um bom tratamento de regras de projeto, assim como demonstra que o SmartDR é superior aos roteadores estado da arte nesses mesmos quesitos.

Palavras-chave: Roteamento detalhado. Acesso a pinos. Busca de caminhos. Regras de projeto. ISPD 2018 Contest.

#### **Abstract**

GONÇALVES, Stèphano Machado Moreira. **SmartDR: Algorithms and Techniques for Fast Detailed Routing with Good Design Rule Handling**. 2020. 130p. Thesis (Doctorate in Computer Science) – Postgraduate Program in Computer Science, Technology Development Center, Federal University of Pelotas, Pelotas, 2020.

Detailed routing is one of the most challenging and time-consuming steps of the design of integrated circuits. The routing solution must obey all of the design rules so that the circuit can be properly manufactured. However, design rule handling may be very challenging, regarding its algorithmic solutions and implementation, and may easily lead to unfeasible runtimes. In order to make the detailed routing resolution more feasible, it is divided into two steps, where in the first, called initial detailed routing, an almost complete solution is achieved by relaxing design rules. In the second step the remaining design rule violations are solved. However, the more these rules are left to be handled in the second stage, the greater is the chance that they will not be completely solved, and this usually occurs. Thus, it is necessary to face the challenge of dealing with as many rules as possible in the first step without compromising the runtime. Thus, this work proposes an initial detailed router, called SmartDR, to meet these needs, that is, to provide a good design rule handling while keeping a good runtime. The main features of the router that meet these goals are pin access and path search techniques. This work proposes a novel pin access method, in which the pin access paths share the same routing resources and are dynamically legalized and implemented. It is also proposed a new path search algorithm, based on A \*-interval search, which is aware of several design rules. A new method to improve the A \* heuristic function is also proposed, taking into account the peculiarities of detailed routing, which leads to a better runtime. Using ISPD 2018 Contest benchmarks, all proposed methods were evaluated separately and altogether in the proposed router, which was compared with state-of-the-art routers. The experiments show that the proposed techniques contribute to runtime and design rule handling improvement, as well as it demonstrates that SmartDR is superior to the state-of-the-art routers in these metrics.

Keywords: Detailed routing. Pin access. Path search. Design rules. ISPD 2018 Contest.

# **Summary**

| 1 Introduction                                                                      | 13 |

|-------------------------------------------------------------------------------------|----|

| 2 Background and Context                                                            | 19 |

| 2.1 Design Styles                                                                   | 19 |

| 2.2 Standard Cell Design Flow of Integrated Circuits                                | 20 |

| 2.3 Routing                                                                         | 21 |

| 2.3.1 Global Routing                                                                | 23 |

| 2.3.2 Detailed Routing                                                              | 26 |

| 2.3.2.1 Design Rules                                                                | 28 |

| 3 Detailed Routing Literature                                                       | 32 |

| 3.1 Detailed Routing Approaches and Techniques                                      | 32 |

| 3.1.1 Channel and Switchbox Routing                                                 | 33 |

| 3.1.2 Over-the-Cell Routing Using Gcells as Switchboxes                             | 34 |

| 3.1.3 Sequential Routing Using Path Search for Long Connections                     | 35 |

| 3.1.4 Track Assignment                                                              | 37 |

| 3.1.5 Multicommodity Flow and Integer Linear Programming                            | 39 |

| 3.1.6 Multilevel Routing                                                            | 40 |

| 3.1.7 Search Space Representation                                                   | 41 |

| 3.1.7.1 Grid-Based                                                                  | 41 |

| 3.1.7.2 Gridless                                                                    | 42 |

| 3.1.8 Multiple Patterning Compliant Detailed Routing                                | 44 |

| 3.2 Path Search                                                                     | 46 |

| 3.2.1 Lee's algorithm                                                               | 46 |

| 3.2.2 A* Algorithm                                                                  | 47 |

| 3.2.3 Line Probe Algorithms                                                         | 52 |

| 3.2.4 A*-interval-based Path Search                                                 | 53 |

| 3.2.5 Improved Heuristic Function for A*-based Path Search in Detailed Routing $\!$ | 55 |

| 3.2.6 Design Rule Aware Path Search                                                 | 58 |

| 3.3 Pin Access                                                                      | 60 |

| 3.3.1 Escape Routing                                                                | 61 |

| 3.3.2 Intra-cell with Conflict-Free Solution and Static Implementation              | 62 |

| 3.3.3 Inter-cell with Conflict-Free Solution and Dynamic Implementation             | 64 |

| 4 SmartDR Overview                                                                  | 66 |

| 4.1 Modeling Routing Information                                                    | 66 |

| 4.2 Routing Flow                                                                    | 68 |

| 5 Pin Access                                                                        | 72 |

| 5.1 Calculating Pin Access Paths                                                    | 74 |

| 5.1.1 Overall Procedure                                  | 74  |

|----------------------------------------------------------|-----|

| 5.1.2 Design Rule Handling                               | 75  |

| 5.2 Dynamic Manipulation                                 | 77  |

| 5.3 Thick Metal Shape Detection                          | 78  |

| 5.4 Comparison with Related Work                         | 82  |

| 5.5 Experiments                                          | 83  |

| 5.6 Conclusions and Future Works                         | 90  |

| 6 Path Search                                            | 91  |

| 6.1 Path Search Mechanics                                | 91  |

| 6.2 Handling PAP Costs in the Source and Target Points   | 93  |

| 6.3 Tunnel Lowerbound                                    | 95  |

| 6.3.1 The Proposed Technique                             | 95  |

| 6.3.2 Algorithm and Implementation                       | 97  |

| 6.4 Design Rule Handling                                 | 99  |

| 6.4.1 Via Checking                                       | 100 |

| 6.4.1.1 Efficient Via Queries                            | 101 |

| 6.4.2 Cut Spacing on Same-Path Vias                      | 103 |

| 6.4.3 Minimum Area                                       | 104 |

| 6.5 Comparison with Related Work                         | 105 |

| 6.5.1 DRAPS                                              | 105 |

| 6.5.2 Improved Lowerbounds for the A* Heuristic Function | 107 |

| 6.6 Experiments                                          | 107 |

| 6.6.1 PAP Cost Aware Path Search                         | 107 |

| 6.6.2 Tunnel Lowerbound                                  | 108 |

| 6.6.2.1 Comparison with (PEYER, 2009)                    | 109 |

| 6.6.3 Design Rule Aware Path Search                      | 112 |

| 6.7 Conclusions and Future Works                         | 114 |

| 7 Comparison with State-of-the-Art Routers               | 115 |

| 8 Conclusions                                            | 122 |

| References                                               | 122 |

# Figure List

| Figure 1- Flowchart of the design process of integrated circuits, emphasizing phy      | sical |

|----------------------------------------------------------------------------------------|-------|

| synthesis.                                                                             | 21    |

| Figure 2- Illustration of a routed circuit layot                                       | 22    |

| Figure 3– Illustration of the global routing                                           | 23    |

| Figure 4– Illustration of a MRST (a), a RMST (b) and a Hannan grid (c), with a 4-      | pin   |

| net                                                                                    | 24    |

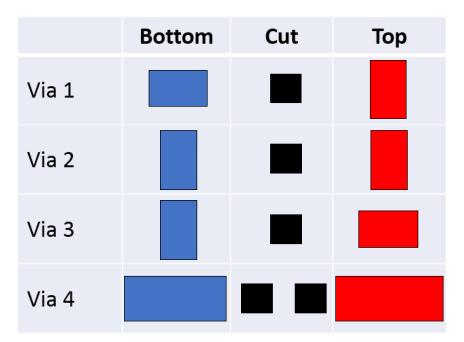

| Figure 5- Illustration of via shape configurations of a via library                    | 26    |

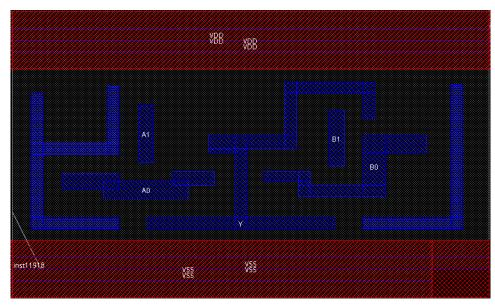

| Figure 6- Picture of a standard cell in Cadence Innovus tool                           | 27    |

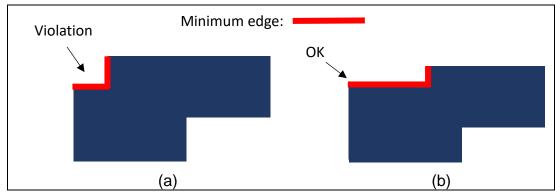

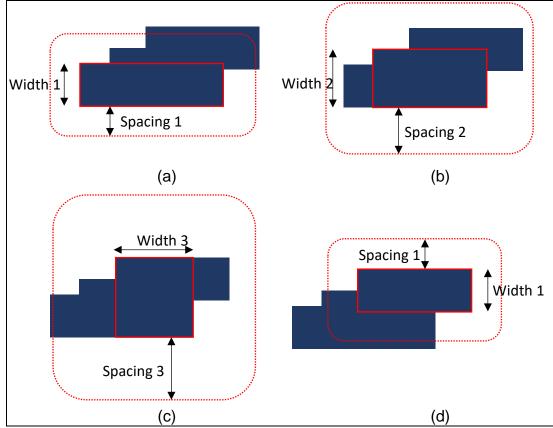

| Figure 7- Illustration of minimum edge rule.                                           | 28    |

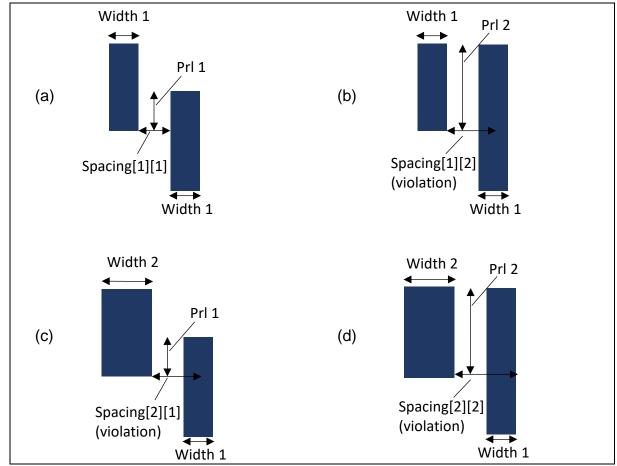

| Figure 8- Illustration of the parallel runlength rule.                                 | 29    |

| Figure 9- Illustration of the parallel runlength rule with a polygon with multiple     |       |

| rectangles                                                                             | 29    |

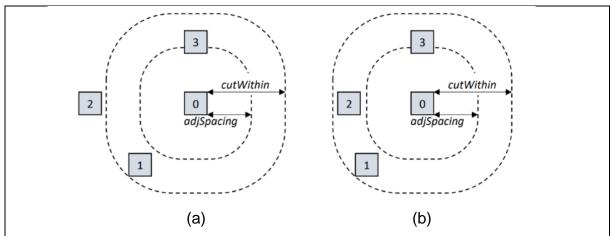

| Figure 10- Illustration of the cut spacing rule with adjacent via cuts constraint      | 30    |

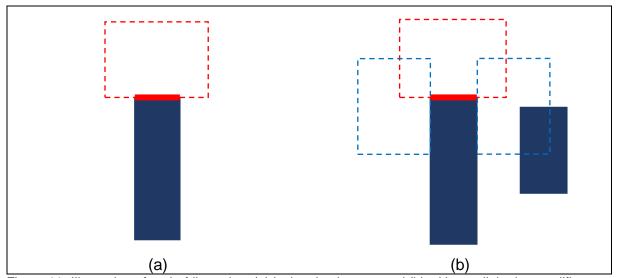

| Figure 11- Illustration of end-of-line rules                                           | 30    |

| Figure 12 – Illustration of a switchbox routed                                         | 33    |

| Figure 13- Illustration of routing each gcell as a switchbox and the problem involv    | 'ed   |

| in the crosspoint assignment                                                           | 35    |

| Figure 14 – Illustration of the Track Assignment problem.                              | 37    |

| Figure 15 – Illustration of the graphs used in the TA technique                        | 38    |

| Figure 16 – The V-shaped multilevel routing framework.                                 | 41    |

| Figure 17 – The shape grid, proposed in BonnRoute                                      | 42    |

| Figure 18 - Illustration of the search space representation using slit tree and inter- | rval  |

| trees                                                                                  | 43    |

| Figure 19 - Illustration of connection graph (a) and tile-based (b) (c) approaches.    | 43    |

| Figure 20 – Illustration of the layout decomposition and stitch generation             | 45    |

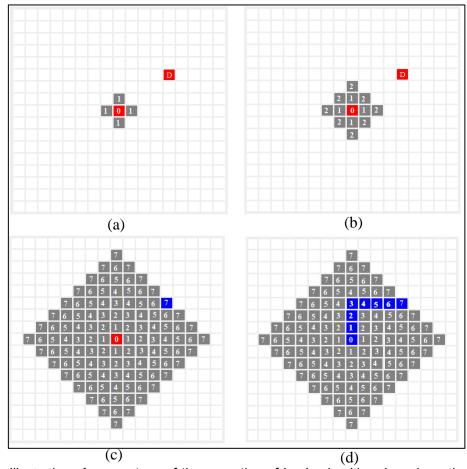

| Figure 21 – Illustration of some steps of the execution of Lee's algorithm             | 47    |

| Figure 22 – Pseudocode of A* algorithm                                                 | 49    |

| Figure 23 - Comparison of the search space of A $^{\star}$ (a) and Lee's algorithm (b) | 50    |

| Figure 24- Illustration of the impact, in the number of search nodes, of the gap       |       |

| between $h(n)$ and $h^*(n)$                                                            | 51    |

| Figure 25 – Illustration of Mikami and Tabuchi's algorithm                             | 53    |

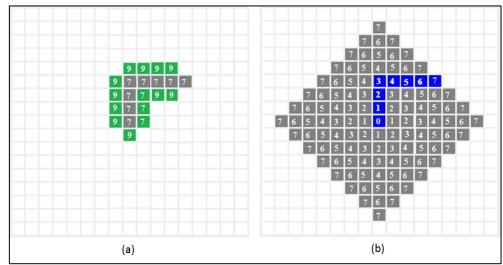

| Figure 26 – Illustration of the principle of merging a group of redundant nodes into    |    |

|-----------------------------------------------------------------------------------------|----|

| intervals5                                                                              | 4  |

| Figure 27 – Illustration of the interval expansion of Hetzel's algorithm5               | 5  |

| Figure 28: Illustration of the expanded search nodes using L1 distance (a) and TL       |    |

| (b), using an A*-interval-based path search (as Hetzel's algorithm), restricted by a    |    |

| tunnel of 3 rectangles5                                                                 | 6  |

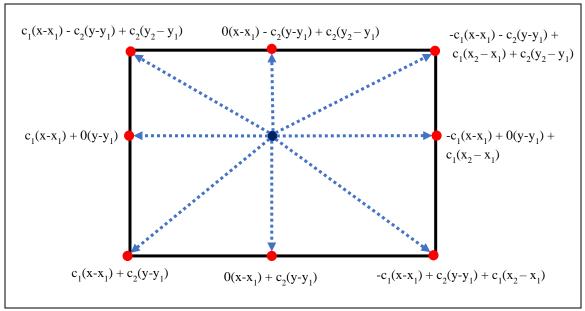

| Figure 29- Illustration of the manipulation of the coefficients and the corresponding   |    |

| offset points (in red)5                                                                 | 7  |

| Figure 30- Illustration of the rectangle partitioning in a tunnel5                      | 8  |

| Figure 31- Illustration of the pin access problem6                                      | 0  |

| Figure 32- Illustration of an escape routing solution6                                  | 1  |

| Figure 33- Illustration of circuitclasses (bottom) and their corresponding instances    |    |

| (top)6                                                                                  | 3  |

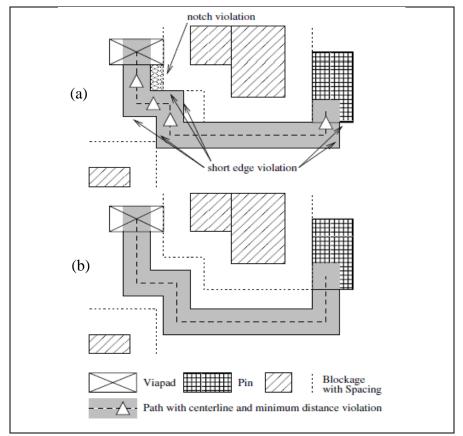

| Figure 34- Illustration of PAP creation with (a) and without (b) violations6            | 3  |

| Figure 35- Illustration of inter-cell conflicts6                                        | 4  |

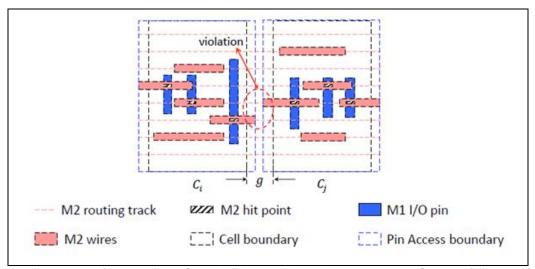

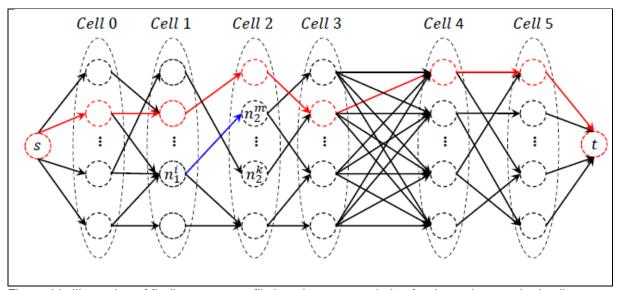

| Figure 36- Illustration of finding a non-conflicting pin access solution for the entire |    |

| standard cell row6                                                                      | 5  |

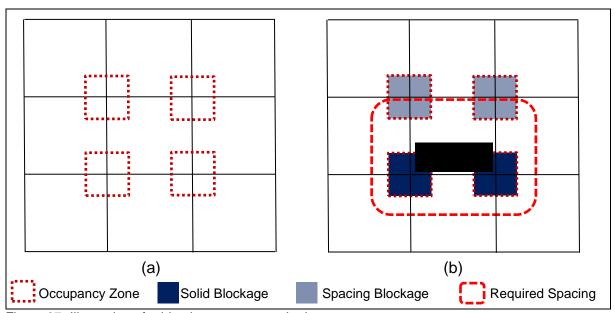

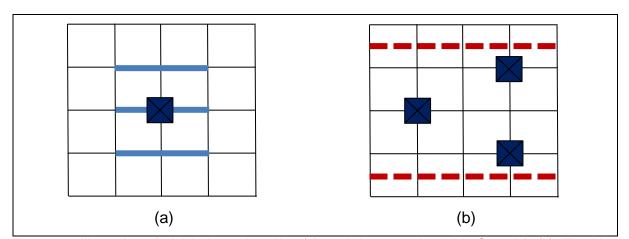

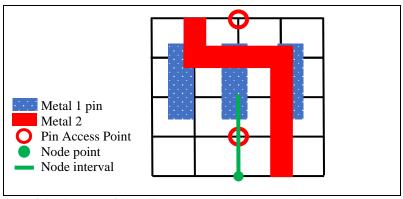

| Figure 37- Illustration of grid point occupancy criteria6                               | 6  |

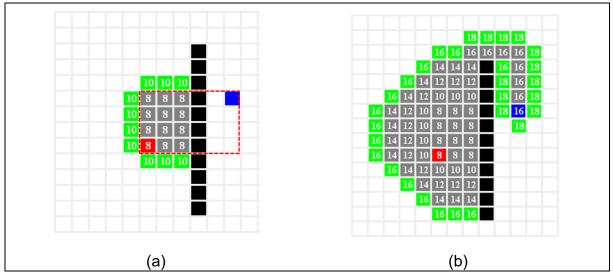

| Figure 38- Illustration of trivial via cut handling (a), and the one adopted in SmartDR |    |

| (b)6                                                                                    | 7  |

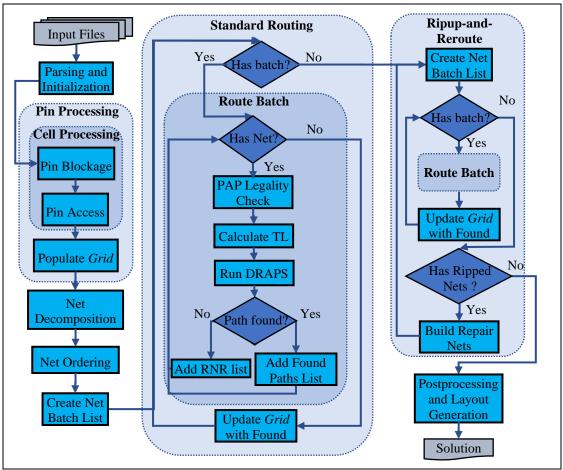

| Figure 39- Flowchart of SmartDR detailed routing flow6                                  | 9  |

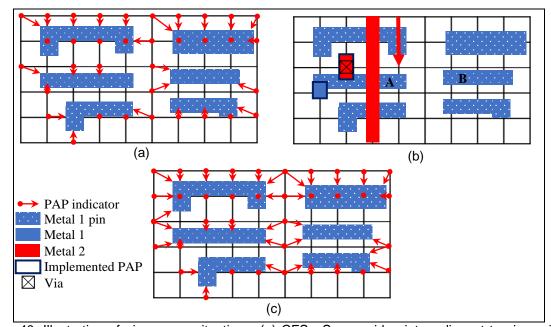

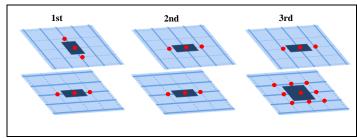

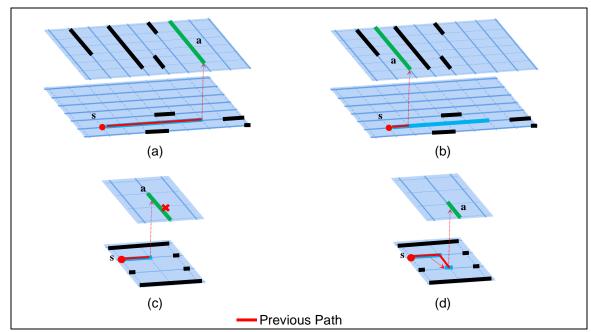

| Figure 40: Illustration of pin access situations7                                       | 3  |

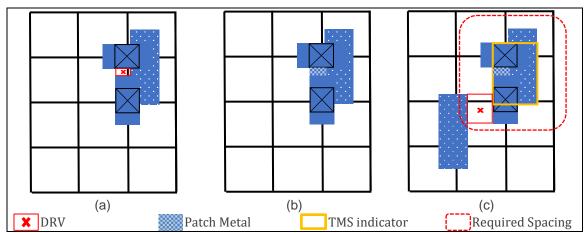

| Figure 41: Illustration of patch metal insertion and TMS creation7                      | 5  |

| Figure 42: Illustration of same-pin PAP conflicts7                                      | 6  |

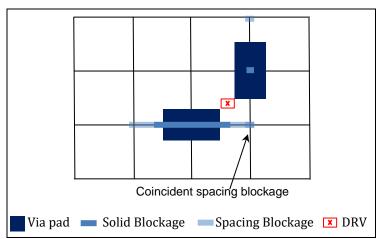

| Figure 43: Illustration of the PAP blockage information and cache usage in metal1. 7    | 7  |

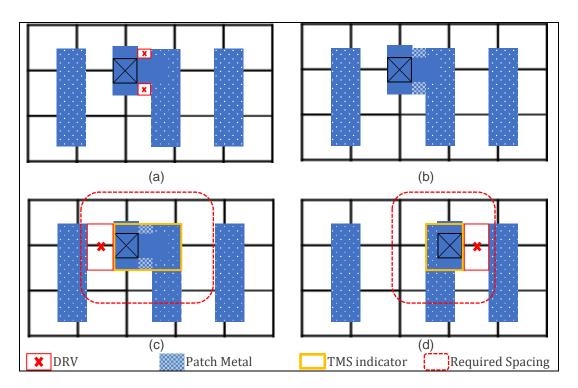

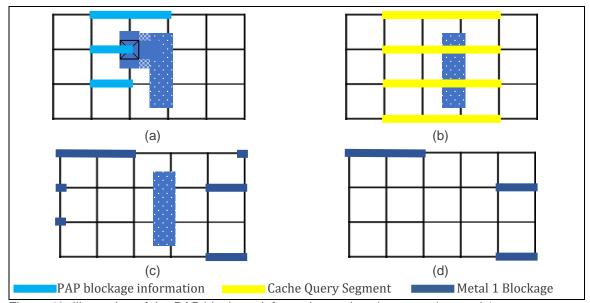

| Figure 44: Illustration of our TMS detection algorithm7                                 | 9  |

| Figure 45- Pseudocode of the proposed TMS detection algorithm8                          | 1  |

| Figure 46- Pseudocode of the method to create a CFS from the RS solution of             |    |

| SmartDR8                                                                                | 5  |

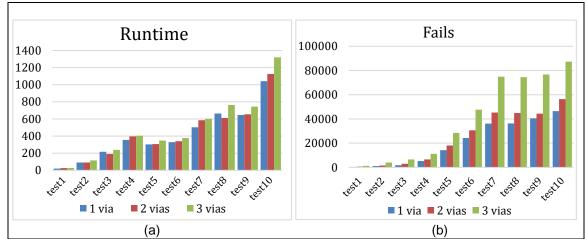

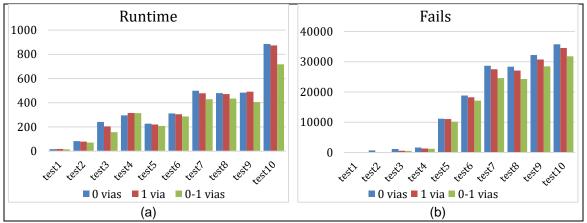

| Figure 47: Comparison of the CFS implementing 1, 2 and 3 via-PAPs, regarding total      | ιl |

| routing runtime (a) and number of failed searches (b) in Standard Routing step8         | 6  |

| Figure 48: Comparison of different strategies of via-PAP implementation, and results    | ;  |

| in total routing runtime (a) and failed searches (b) in Standard Routing step8          | 8  |

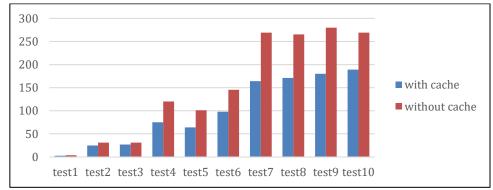

| Figure 49: Runtime results of PAP legality check with and without cache8                | 8  |

| Figure 50- Pseudocode of DRAPS                                                         | 92  |

|----------------------------------------------------------------------------------------|-----|

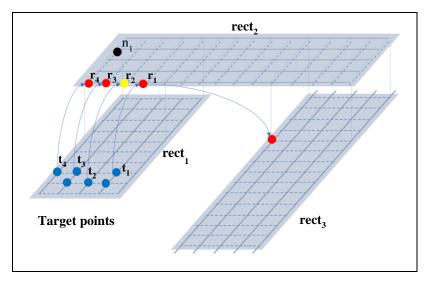

| Figure 51: Illustration of the issues of handling costs in the target points           | 94  |

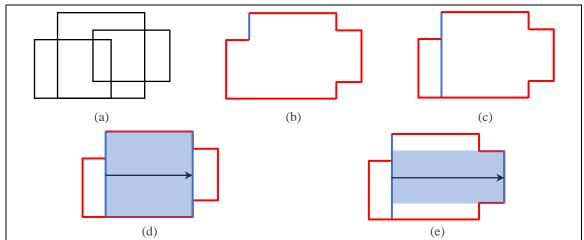

| Figure 52: Illustration of the <i>TL</i> technique. Ref points are red and yellow      | 96  |

| Figure 53- Pseudocode of the proposed algorithm to precompute the tunnel               |     |

| lowerbounds                                                                            | 98  |

| Figure 54- Pseudocode of the DRC function                                              | 100 |

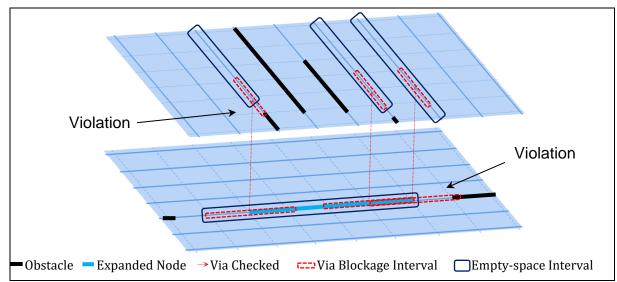

| Figure 55: Via selection order and via blockage information (red dots)                 | 101 |

| Figure 56- Illustration of a situation where querying the grid with the via blockage   |     |

| information is not enough to avoid DRVs                                                | 102 |

| Figure 57- Illustration of the via check using the empty-space intervals stored by     |     |

| DRAPS                                                                                  | 103 |

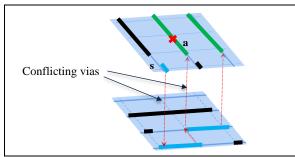

| Figure 58: Illustration of a path search scenario with a cut-cut spacing violation wit | hin |

| the path                                                                               | 104 |

| Figure 59: Illustration of situations of min area check                                | 105 |

## **Table List**

| Table 1: Differences Between the Proposed Method and (NIEBERG, 2011)            | 82   |

|---------------------------------------------------------------------------------|------|

| Table 2: Benchmark Information                                                  | 84   |

| Table 3: Comparison Between RS and CFS Approaches                               | 86   |

| Table 4: TMS Usage Results                                                      | 89   |

| Table 5: Comparison with design rule aware path search algorithms in literature | .106 |

| Table 6: Results of Using PAP Costs in the Path Search                          | .108 |

| Table 7: Results of the Proposed Tunnel Lowerbound Technique                    | .109 |

| Table 8: Results of the method proposed in (PEYER, 2009)                        | .110 |

| Table 9: Comparison of relative results between TL and the method in (PEYER,    |      |

| 2009)                                                                           | .111 |

| Table 10: Results of Design Rule Violations of DRAPS                            | .113 |

| Table 11: Detailed Design Rule Violation results over (KAHNG, 2018) and (CHEN   | ٧,   |

| 2019b)                                                                          | .116 |

| Table 12: Area Short and Total Violation Results                                | .116 |

| Table 13: Runtime Results                                                       | .116 |

| Table 14: Results of WL, Vias and Out-of-Guide Usage                            | .117 |

| Table 15: Results of Wrong-Way WL, Off-Track Usage and Scores                   | .117 |

| Table 16: ISPD18 Score Metrics                                                  | .119 |

| Table 17: ISPD18 Score Results                                                  | .120 |

### **List of Abbreviations and Acronyms**

**ASIC** Application Specific Integrated Circuit **Breadth-First Search BFS** CAD Computer Aided Design Conflict-Free Solution **CFS Cross Point Assignment CPA** Depth-First Search **DFS** Design Rule Checking **DRC Design Rule Violation DRV** Field Programable Gate Array **FPGA** Global cell gcell **HPWL** Half-Perimeter-Wire-Length Hardware Description Language **HDL** Integer Linear Programming **ILP Integrated Circuit** IC International Symposium on Physical Design of 2018 ISPD18 LUT Lookup Table Maximum Weight Independent Set **MWIS MCF** Multicommodity Flow PAP Pin Access Path Rectilinear Minimal Spanning Tree **RMST** RS **Resource Sharing** Ripup-and-Reroute RNR Self-Aligned Multiple Patterning **SAMP TMS** Thick Metal Shape Track Assignment TΑ Wire-Length WL

#### 1 Introduction

As technology advances, integrated circuits have become increasingly complex. The shrinking of the transistors size, and consequently of other components, allowed the design of circuits with a huge number of logic gates, limited to very small physical spaces. In addition, the market has increased the demand for the technology, requiring greater agility in the production of integrated circuits. Therefore, due to their high complexity, the design of integrated circuits is performed by CAD (Computer Aided Design) tools, which automate the synthesis process of the circuits.

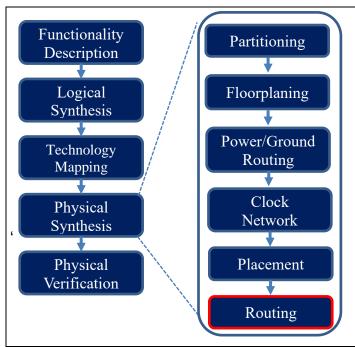

There are several design styles to perform the circuit synthesis. The most eminent design style is called standard cell. The standard cell synthesis process begins with the description of the logic behavior of the circuit using hardware description languages (HDL). After that, the set of logical functions that describe the circuit are optimized in the *logical synthesis* design step. Then, the *technology mapping* design step defines which available logic gates will be used to implement these logic functions. The next design step is *physical synthesis*, which aims to provide a geometrical description of the circuit. The physical synthesis is subdivided into two main steps: *placement* and *routing*. The placement determines the positions of the logic cells aiming to minimize some cost functions and alleviate the effort of the next design step. The routing design step obtains the wire routes needed to connect the components, while also minimizing some cost functions. Finally, a physical verification step is performed to ensure that all electrical and logical functionality are met.

Due to its high complexity, routing is subdivided into two stages: *global* and *detailed* routing. The global routing defines the areas in which the wires of nets should pass through, while controlling wire congestion to improve routability for detailed routing. Thus, the main purpose of global routing is to provide instructions for detailed routing, in addition to reducing its effort. The detailed routing finds the exact location of the wires inside the areas delimited by the global routing. Detailed routing must take into account a number of manufacturing constraints, referred as design rules.

In the old days, when there was no global routing, the first routers relied entirely on Lee's algorithm (LEE, 1961) or the line probe methods of (MIKAMI, 1968) and (HIGHTOWER, 1969). However, the circuit's layout had specific characteristics that could be exploited in order to perform a more efficient routing. The cells were grouped in rows, and between each row there was a space, called *channel*, which was used for routing between two adjacent rows. Thus, the *channel* (HASHIMOTO; DEUTSCH,

1971, 1976) and *switchbox* (JOOBBANI; LUK; MAREK-SADOWSKA; HAMACHI, 1986, 1985, 1985, 1984) routers emerged to solve the routing problem more efficiently. As the complexity of the circuits increased, global routing was proposed to alleviate the routing problem. Later, this complexity reached a level such that the channels had to be very large in order to support all wires, and this was a problem, since the circuit area had to increase. Thereby, it was necessary to change the circuit layout paradigm, removing the channels between the rows of cells, and assigning the routing to take place above the cells. This paradigm is called *over-the-cell* routing, and it is used nowadays.

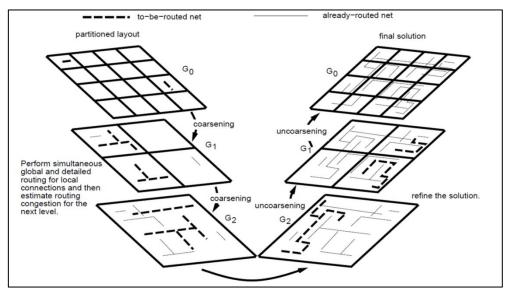

With the end of channel routing, several routing approaches have emerged. In the time of channel routers, global routing divided the circuit layout in irregular regions, which were channels and switchboxes, and most connections were performed inside each region. In over-the-cell routing, global routing partitions the layout in a regular grid of global cells (gcells), and most connections must cross the boundaries of the gcells. One approach to perform detailed routing in this new paradigm is to route each gcell of a global route separately. In order to do this, it is necessary to define the connecting interface between gcells. The problem to define such interfaces was performed as an intermediate step between global and detailed routing and was known as the Cross Point Assignment (CHANG, 2001) (KAO, 1995). Another new approach is the track assignment (BATTERYWALA, 2002), which was proposed as an intermediate step between global and detailed routing. It consists in assigning the segments of global routes to the routing tracks. It is followed by detailed routing, which connects the missing pieces of the nets. The detailed routing handling long connections with fast and optimal path search was introduced by Hetzel (HETZEL, 1998). In this approach, a single path search is performed for an entire path of gcells. This was possible due to the path search algorithm proposed (HETZEL, 1998), which combined the benefits of the maze search and line probe algorithms. At the first half of the past decade, the multilevel routing frameworks (LIN; HO; CONG; CONG, 2002, 2003, 2001, 2005) became popular. They consist in further decomposing the routing problem in even more levels of abstraction beyond global and detailed routing, also combining topdown and bottom-up methodologies.

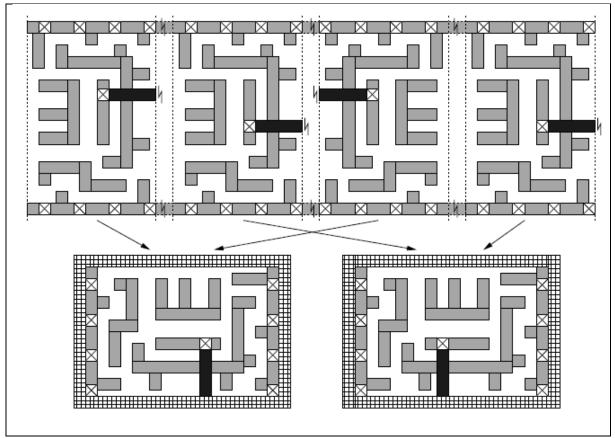

Most recent detailed routing approaches combined previous techniques and specialized some of them. The multilevel routing frameworks did not persevere. Li et al. (2007) proposed a gridless router combining two common gridless routing

techniques, tile expansion and connection graphs. In (LI, 2011), the approach of (LI, 2007) was combined with track assignment (BATTERYWALA, 2002), which was aimed for grid-based routing. Ozdal (2009) proposed efficient algorithms for escape routing for dense pin clusters. Zhang et al. (2013) proposed RegularRoute, a detailed router that uses a track-assignment-based technique (BATTERYWALA, 2002) inside detailed routing, providing full connections, rather than the original track assignment, which was an intermediate step between global and detailed routing and which provided a partial solution. The GDRouter routing tool (ZHANG, 2012) combined a global router (XU, 2009) with RegularRoute (ZHANG, 2013) in an interleaved global and detailed routing procedure. Gester et al. (2013) proposed efficient data structures to handle design rules in a grid-based routing using a path search algorithm based on Hetzel's algorithm (HETZEL, 1998) for long connections. Jia et al. (2017) proposed a detailed router based on the multicommodity flow graph problem and used Integer Linear Programming (ILP) to solve the routing problem. TritonRoute (KAHNG, 2018) proposed an intra-layer parallel routing scheme and also solved it using ILP. In (SUN, 2018), a via location aware track assignment and a multi-thread two stage detailed routing algorithm is proposed. (CHEN, 2019b) proposed a technique to make the path search run in an optimized local graph, based on the obstacles inside the global routing guide. Considering the peculiarities of advanced technology nodes, many works have emerged addressing multiple-patterning compliant detailed routing (DING; YU; YUAN; GAO; MIRSAEEDI; MA; LIU, 2018, 2018, 2009, 2010, 2011, 2012, 2016).

Detailed routing also holds an important problem, which is pin access. The pin shapes are often irregular and not aligned on the routing grid, requiring special treatment when connecting with the wires. Also, this connection often leads to design rule violations (DRVs) between the wire and the pin, and within the pin access path itself. Since one of the main goals of detailed routing is to avoid DRVs, this problem deserves considerable attention. There are few works on literature that addressed the pin access problem. Nieberg (2011), proposed an approach that uses gridless pin access paths free of DRVs within the paths themselves. The method also explores redundancies in the cell instances such that it is not necessary to calculate pin access solutions for every placed cell instance, saving runtime. In (OZDAL, 2009), scape routing is proposed, aiming to provide pin access paths that possibly run out of the cell boundary, escaping from the pin access congestion, increasing routability. In (XU,

2016) and (XU, 2017), pin access considering self-aligned double patterning compliant detailed routing is proposed.

Almost all detailed routing approaches rely on path search algorithms. The goal of such algorithms is to find a path between two sets of points in a search space. There are two classes of path search algorithms in detailed routing: the maze search and the line probe algorithms. The maze search algorithms derive from Dijkstra's algorithm (CORMEN, 2001). They work on a graph, which is usually a grid, and expand the search point by point, while the line probe algorithms use line segments. Usually, the maze algorithms guarantee the optimal path, but they are slow, while the line probe algorithms are usually fast but do not guarantee the optimal path. The Lee's algorithm (LEE, 1961) is equivalent to the Dijkstra's algorithm in the specific context of grid graphs with uniform cost edges. Later, Rubin (RUBIN, 1974) used the A\* search (HART, 1968) technique to speed up Lee's algorithm. The first line probe algorithm was proposed by Mikami and Tabuchi (1968). Later, Hightower (1969) proposed a modification on this algorithm. Finally, Hetzel (1998) united the advantages of both classes of algorithms, proposing an A\*-based algorithm using intervals of grid graph vertices as search nodes. The algorithm was shown to be faster than A\*, and it is optimal, unlike (MIKAMI, 1968) and (HIGHTOWER, 1969). Later, the algorithm was generalized in (PEYER, 2009) to handle more generic scenarios.

The mentioned path search algorithms are not aware of the design rules that detailed routing must attend to. These rules are commonly treated outside of the path search. Part of them are handled after routing, in post-processing steps. However, the attempt of solving DRVs after routing may either result in the inability of their resolution or in the creation of new violations. A good way to handle this situation is to make the path search algorithm aware of some design rules, so that it is able to provide DRV free paths in a correct-by-construction fashion.

There are few works in literature that propose design rule aware path search algorithms. MANA (CHANG, 2013) is aware of the minimum area design rule, but it is a maze algorithm, and such algorithms present high runtime. In (CHEN, 2019b), a maze algorithm that attends the minimum area rule is also proposed. It runs in a reduced graph, constructed on-the-fly, which mitigates the maze routing runtime problem, but there is still a time overhead to construct such graph. In (AHRENS, 2015), it is proposed a multi-label algorithm which also handled this design rule, and different-

mask rules for multiple patterning detailed routing approaches. The runtime was also high, making the algorithm worth to be used only in some circumstances.

Although detailed routing has been extensively studied in the past decades, there are still research possibilities. One of the biggest challenges of detailed routing is design rule handling. The routing solution must respect all design rules, since the circuit depends on it to properly work. Considering that design rule handling is hard, detailed routing is yet subdivided. The first step, called initial detailed routing, performs the majority of the effort, finding all routes and considering the simplest design rules. The last step solves the remaining DRVs and may perform some refinement on the routing solution. This subdivision is due to the fact that considering all design rules at once is hard and increases the likelihood of causing large runtime overheads. However, leaving more violations for the final step makes the DRV cleanup harder, and possibly unfeasible. Thus, it is ideal to try to solve as many violations as possible in the initial phase. However, eminent routers (GESTER; ZHANG, 2013, 2013) have shown to be unable to handle all design rules in the initial step, delegating industrial routers to perform DRV cleanup. Even so, the industrial routers are not always able to solve all violations. Also, runtime is another important objective to be optimized, since detailed routing is naturally time consuming, and making high effort to handle design rules is unfavorable for it.

Mantik et al. (2018), members of Cadence Design Systems, pointed another issue in part of the detailed routing works in the literature, which is the fact that they relied on small instances of the routing problem. Considering these issues, the Initial Detailed Routing Contest of the International Symposium on Physical Design of 2018 (ISPD18) (MANTIK, 2018) emerged, encouraging research in detailed routing field and bringing the first set of detailed routing academic benchmarks to the literature. Also, although the reality of the industry is probably far more advanced than in the literature, it is indeed pertinent to do research in detailed routing to provide public knowledge. Besides, although less likely, the academy research may even contribute to the industry.

Considering that time is an important metric for detailed routing, and having a design with no violations is essential, this work proposes an initial detailed router, called SmartDR, addressing these objectives. The key features of SmartDR that attend to these objectives are the pin access algorithm and path search techniques. The main contributions of this work are:

- 1. a novel pin access approach of flexible pin access path selection with resource sharing and dynamic legality check;

- 2. a design rule checking algorithm, used in pin access, to detect thick metal shapes that require higher spacing;

- a new A\*-interval-based design rule aware path search (DRAPS) algorithm capable of handling the minimum area rule, cut-to-cut spacing rules of same-path vias, and is aware of the via library, performing efficient via checking;

- adaptations in the path search to properly incorporate costs in the source and target points to reduce pin access path usage, which impacts in via count and other routing metrics;

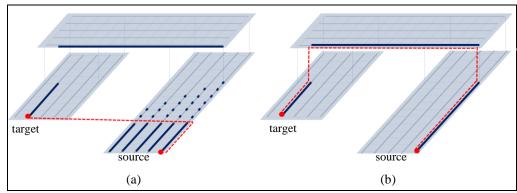

- 5. an efficient technique to improve the A\* heuristic function (*h*) by making it aware of the global routing guides, providing a substantial speedup to the path search;

- 6. experimental results, using ISPD 2018 Contest benchmark suite (MANTIK, 2018), evaluating the proposed techniques, and comparing SmartDR with other state-of-the-art routers that were also tested using the same benchmarks. The results show that the proposed router is superior in runtime and design rule handling.

This work is structured as follows. Section 2 clarify the context of this work and presents some background information. Section 3 presents a review of the detailed routing literature. Section 4 presents an overview of SmartDR. Section 5 presents the proposed pin access method and the related experiments. Section 6 presents the proposed path search techniques and experiments. Section 7 presents the comparison of SmartDR with state-of-the-art routers and section 8 are the conclusions.

### 2 Background and Context

First, let us define some common nomenclature. An *integrated circuit* (IC) consists of *logic gates*, which are interconnected by wires. A *logic gate*, or *cell*, is the building block of the logical functionality of the circuit. Since it is a component that implements a logic function, it has inputs and outputs, which are called pins or terminals. An output pin carries the electrical signal through wires, which connect to input pins of other logic gates. This set of pins is called *net*. A *block*, or *logical block*, or *macro block*, is a circuit of logic gates that acts as a black-box component of the chip functionality, and commonly presents a functionality that is easily reusable. The term macro block is commonly used to designate a block with a large number of cells.

### 2.1 Design Styles

There are several ways to design integrated circuits. The design styles impact in time-to-market, cost and in the quality of the IC. Also, some design styles depend on the application of the IC.

The *Full Custom* design style allows the design to be highly customizable. For example, macro blocks can be placed anywhere in the chip. The high freedom in the design makes the IC more optimized. However, the development time is also high, due to a relative lack of automation, making the design more expensive. Also, due to the high manual interaction, this style is more susceptible to present errors. It is worth using when the IC production is high enough to compensate the large design effort, such as in microprocessors and FPGAs (Field Programable Gate Arrays) (KAHNG, 2011a).

In *Gate Array* design style, all logic components have the same structure and a generic logical functionality, and there is no wiring connecting the components. The wire routing is performed after defining the application of the IC. Due to the standardization of the logic components, the only major design effort is in routing, and, consequently, time-to-market and design costs are favorable. However, since the placement of the components does not take into consideration routing, this may cause routing problems (KAHNG, 2011a).

Similarly to gate arrays, the *FPGAs* use standardized logic components, but also with prefabricated wiring. All logical functionality is configurable by the user. The design cost and time-to-market is even lower than in the gate array style. However, the

IC runs slower and dissipates more power than application specific integrated circuits (ASICs) (KAHNG, 2011a).

The *Standard Cell* design style is the more popular for ASICs. It uses a library of logical cells, and possibly some macro blocks, to implement the IC functionality. The cells have standardized height and are placed, in the chip, side by side in rows. Between the rows, power and ground rails feed the cells. The conception of the cell library may take substantial effort. Still, with design freedom reduced, this design style provides a good time-to-market and design cost (KAHNG, 2011a). The scope of this work is within standard cell-based design.

#### 2.2 Standard Cell Design Flow of Integrated Circuits

The design of standard cell ICs is a complex procedure, containing many steps. Figure 1 presents a simplified scheme of the design flow. The procedure begins with the specification of the of the goals and the requirements of the system that the IC will implement. The logic behavior of the circuit is defined using hardware description languages (HDL). Some common HDLs are Verilog and VHDL.

In the *Logical Synthesis* step, a data structure called *netlist* is generated based on the circuit description. This structure stores all the information regarding the logical connectivity of the circuit. Then, the netlist is optimized by boolean algebra optimization techniques. Once the logical synthesis is finished, *Technology Mapping* step is started. This step consists in defining which available cells will be used to implement the logic functions that define the netlist.

The next design step is the Physical Synthesis, which aims to define a geometrical description of the circuit. The physical synthesis is subdivided in the following steps. *Partitioning* breaks up a circuit into smaller subcircuits or modules, which can each be designed or analyzed individually. *Floorplanning* determines the shapes and arrangement of subcircuits or modules, as well as the locations of external ports and IP or macro blocks. *Power and ground routing*, often intrinsic to floorplanning, distributes power and ground nets throughout the chip. *Placement* finds the spatial locations of all cells within each block, while minimizing the estimated wire-length (WL). *Clock network synthesis* determines the buffering, gating (e.g., for power management) and routing of the clock signal to meet prescribed skew and delay requirements. *Routing* provides the wire routes needed to connect the components, while also minimizing the WL and attending to other objectives (KAHNG, 2011b).

Figure 1- Flowchart of the design process of integrated circuits, emphasizing physical synthesis.

After the physical synthesis, the *Physical Verification* step is performed to ensure that all electrical and logical functionality are met. Here, a netlist is extracted from the layout and compared to the original netlist. Also, design rule checking (DRC) is performed to ensure all design rules are respected. The same way, electrical rule checking is performed to validate the correctness of the electrical signals and their timing.

### 2.3 Routing

The main goal of the routing problem is to determine the wire routes of all nets of the IC. Also, the routing solution *must* respect all design rules. The design rule attendance is necessary to ensure that the IC can be manufactured and will be electrically reliable.

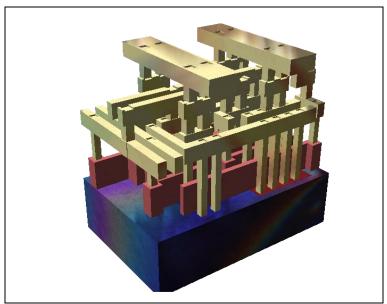

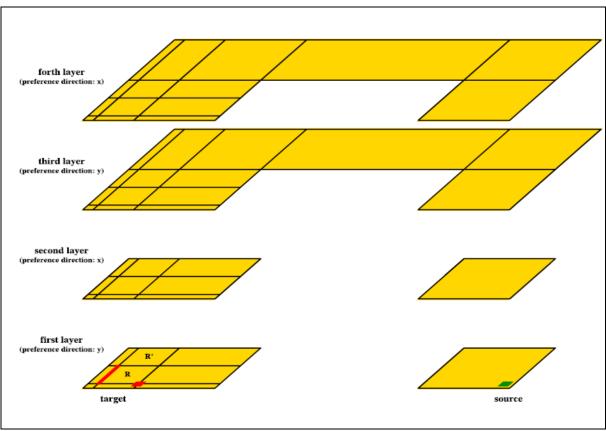

The routing occurs in a tridimensional space with parallel planes, where each plane refers to a metal layer in which the wires are placed. Metal layers have a preferred routing direction, which is either horizontal or vertical. Adjacent layers have different preferred directions. This is to avoid capacitance effects of nearby parallel wires of adjacent layers and to improve routability. Between each metal layer, there is a cut layer. The cut layers hold the vias, which are the components that connect wires from different metal layers. This stack of metal and cut layers is placed above the standard cells. Figure 2 illustrates a section of a routed circuit layout.

Figure 2- Illustration of a routed circuit layot. The red and blue layer belong to the standard cell, and the metal layers are above. Source: public domain.

Routing also tries to optimize some objective functions, such as runtime, WL, number of vias, timing and yield. The runtime is important because routing is a very time-consuming process, accounting for much of the time spent on physical synthesis. WL impacts power consumption, delay and signal degradation. The number of vias also contributes to signal degradation since the vias have high electrical resistance. Timing is related to the delay of the propagation of the electrical signal in the IC. Yield represents the likelihood of a circuit to be manufactured correctly, without presenting any defects. Some good practices may be beneficial to yield.

The number of wire connections that routing must complete may reach the millions. When modeled by a grid graph, the routing space may present billions of vertices (SCHULTE, 2012). This makes impracticable, in runtime terms, to perform the wire connections just by using path search algorithms, even the line probe ones, which are the fastest. Also, simply routing the wires without any planning will make many wires to unnecessarily congest routing areas needed to complete some wire connections, which compromises routability. Finally, the lack of planning will make the solution, even if possible to exist in a feasible time, to present low quality due to large wire detours, increasing WL, via count and timing.

These facts require routing to adopt a divide and conquer strategy. Thus, routing is divided into *global* and *detailed* routing. Global routing works on a simplified version of the problem and serves as an orientation to detailed routing. This separation in two steps is not always precise, since there are some works that propose multilevel routers

(LIN; HO; CONG; CONG, 2002, 2003, 2001, 2005), with more intermediate steps, or interleaved approaches (ZHANG, 2012), which will be mentioned in section 3.1.

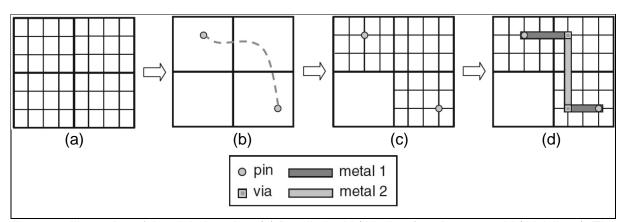

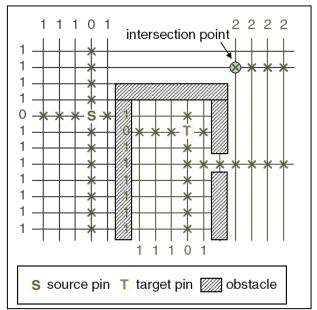

#### 2.3.1 Global Routing

The goal of global routing is to reduce the complexity of the problem by providing a pre-solution to detailed routing, which defines the final routing. Also, objective functions as WL, via count and timing are optimized. This complexity reduction occurs through a use of coarse-grained grid (Figure 3a and b), where each grid point covers many points of the real grid, used in detailed routing. Thus, each point represents an area, called the global cell (gcell). The grid can be both two-dimensional or three-dimensional. Each edge of the graph, which represents the grid, models the borders between two gcells. Each edge has a capacity, which represents the maximum number of wires that can pass through both regions. As routing occurs, the congestion level of each edge is calculated based on the capacity of the edge and the amount of wires passing through it. The global routing output are the gcell routes of each net. A gcell route of a given net, called *global routing guide*, is a region that restricts, with some flexibility, the detailed routing solution for this net as shown in Figure 3b, c and d.

The method to route a net depends on the its number of pins. The approaches can be divided into two categories: for two-pin nets and for nets with more than two pins (multi-pin nets). Considering two-pin nets, there are two ways to solve the problem: using maze routing or using pattern routing. In maze routing the A \* algorithm (section 3.2.2) or some variation of it is used. In pattern routing, the search is restricted specifically to considering path patterns that follow the format L (one bend), Z (two

Figure 3– Illustration of the global routing. (a) Detailed grid (thin lines) and coarse grid (thick lines). The coarse grid contains four gcells. (b) Global routing determines the connection path, in gcells, between two pins. (c) The detailed routing area is restricted according to the resulting global routing path. (d) The connection is made in detailed routing. Source: (CHEN, 2009).

bends, as in Figure 3d) or U (a detour with two bends). This approach was proposed by Chen (1999) and Kastner (2002). Both search styles (maze and patterns) guarantee the optimal path, but pattern routing is restricted to a much smaller search space, presenting a superior performance in runtime. Thus, pattern routing is widely used in global routing of two-pin networks (CHEN, 2009).

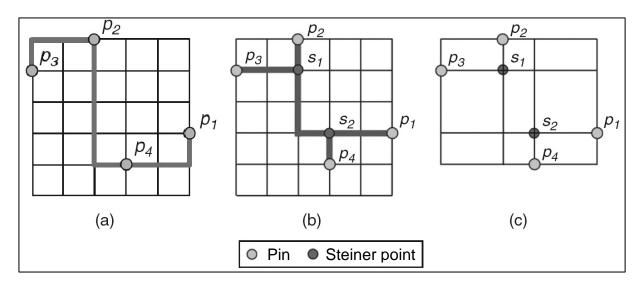

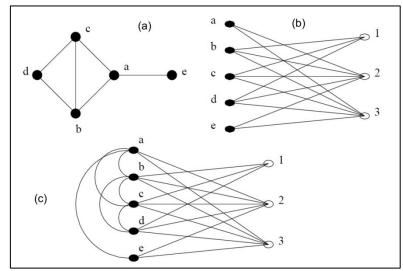

The second category of algorithms used in global routing refers to multi-pin nets. Within this scope, there are two main approaches to solving the problem. The first is to decompose the net into multiple two-pin nets and solve each one by default two-pin routing. The second is to solve the Steiner tree problem (SHERWANI, 1998).

The first approach can be solved by finding a Rectilinear Minimal Spanning Tree (RMST) from the net pins. A RMST is a tree that connects all vertices of a graph, having the lowest possible cost, which is given by the sum of edge costs. In this case, the vertices of the graph are the pins and the edges represent the possible connections of each pin with the others. Edge cost is the lowest possible connection cost. RMSTs can be found in polynomial time by the algorithms of Kruskal and Prim (CORMEN, 2002).

Solving the problem by this approach can provide suboptimal results. Figure 4a shows the net resulting from a four-pin MST. Note that the net does not have optimal WL, which is the case in Figure 4b. In this case, the router split the net into three two-pin nets, which were routed separately. Considering separately the resulting path of each pair of pins, it is clear that the WL is optimal. However, the total WL of the net is not optimal. In order to obtain the optimal result, it is necessary that the paths share some sections, but this cannot be foreseen since the problem was decomposed. Thus,

Figure 4– Illustration of a MRST (a), a RMST (b) and a Hannan grid (c), with a 4-pin net. Source: (CHEN, 2009).

it is necessary to have a global view of the problem, which is the case of the Steiner tree problem.

The second approach to routing a multi-pin net is to find the Minimal Rectilinear Steiner Tree (MRST) of the net. A MRST is an RMST with additional vertices called Steiner points. These points are strategically inserted into locations to force the net to reuse the same path sections to connect different pins. The problem in finding an MRST consists in determining the appropriate number of Steiner points and their locations to maximize this "path section sharing". These points form the Hanan grid (HANAN, 1966), which is obtained by projecting vertical and horizontal lines over each pin (Figure 4c). The vertices of this grid are the intersection points of these lines. The problem of finding an MRST is NP-Complete. Thus, heuristics were created to solve the problem quickly, with little WL loss, compared to the optimum result. The FLUTE algorithm (CHU, 2008) is a good example of the use of such heuristics, showing optimum results for nets of 9 pins or less. However, these methods do not take into account important routing factors such as obstacles, congested areas, and delay. There are several methods that consider the presence of obstacles (LIN; WU; LI; HUANG; 2007, 2007, 2008, 2010). Regarding congestion consideration, the FastRoute router (PAN; PAN; ZHANG; XU; 2006, 2007, 2008, 2009) is one of the main references. Another method of calculating an MRST is by using maze routing. The advantage of this approach is that it easily handles all the factors involved in routing, providing a solution with better quality, but with a runtime disadvantage. This approach is used by the AMAZE tool (HENTSCHKE; 2007, 2009).

The mentioned approaches are used to route single nets. For routing all nets in the chip, there are two main approaches: concurrent, using ILP, and a sequential, using a negotiated congestion technique. The concurrent one routes all nets simultaneously, and the sequential routes them one after another. The sequential methodology relies on ripup-and-reroute (RNR)<sup>1</sup> techniques. The RNR consists in ripping nets already routed so that new nets can be successfully routed. Considering that the ILP-based global routers present higher runtime, the sequential approach is preferred (KAHNG, 2011c). The sequential methodology using negotiated congestion technique keeps a cost history of the nets that passed between each gcell. When the capacity of an edge of the gcell graph is overflown, the cost of this edge is increased. Thus, congested

<sup>1</sup> RNR is sometimes called RRR, as in (KAHNG, 2011c)

regions present high penalty costs for the routing algorithms. This avoids the paths to pass through them, leaving the region to be used only by net nets that really need to do so (KAHNG, 2011d).

#### 2.3.2 Detailed Routing

In detailed routing, all wire routes are determined within the global routing guides, with some flexibility. Detailed routing also tries to optimize metrics as WL and via count, but the major part of these optimizations was already performed in global routing and are reflected in the global routing guides. There are many approaches to solve detailed routing. They are described in section 3.

Normally, the routing is restricted, with some flexibility, to a predefined routing grid. Each metal layer has a set of tracks in the preferred routing direction. There is also a routing approach that does not use any predefined grid, which is called gridless routing. Anyway, even in gridless routing, non-uniform grids may be created on-the-fly to run path searches.

The physical components involved in routing are pins, wires, vias and obstructions. The pins are interconnected by wires and vias. The wires have a default width, but some special nets may require a different width. Upper metal layers have thicker wires. The vias connect wires of adjacent layers. A via has a bottom and a top pad, as shown in Figure 5. Thus, a via is defined by three shapes: in the bottom, in the

Figure 5- Illustration of via shape configurations of a via library.

Figure 6- Picture of a standard cell in Cadence Innovus tool. Metal 1 is blue and metal 2 is red. The labeled polygons are the pins, and the other are the obstructions.

cut and in the top layer. Some vias present more than one cut shape. The vias that a detailed router can use are defined in a via library. Most of the pins are in the standard cells. These pins have more irregular shape and require much care when making contact with the wires, since it is easy to such connections cause DRVs, as will be discussed ahead. The other pins have a more regular shape, usually composed by just one rectangle, and are located in the chip boundaries (I/O pins) and in the macro cells. The obstructions are usually present in some standard cells and in the macro blocks. Figure 6 shows the pins and obstructions of a standard cell.

One of the biggest challenges of detailed routing, and possibly the biggest, is design rule handling. Dealing with all design rules during the construction of the routing solution is hard. Thus, this incentive the division of detailed routing in two parts. The first, called initial detailed routing, takes the major effort of the process. It finds all wire routes and handles the more feasible design rules. The last part, which is often referred as design rule cleanup tries to solve the remaining design rule violations (DRVs) and may perform some refinement on the solution. The problem is that it is not always possible to solve all DRVs in the cleanup step, and this has been constantly seen in the literature (AHRENS; GESTER; JIA; ZHANG, 2015, 2013, 2017, 2013). The more violations the initial phase leaves for the final one, the more likely is to be impossible (or unfeasible) to solve them all. Thus, the initial phase should handle DRVs as much as possible, while observing all metrics to be optimized. It is a challenging

Figure 7- Illustration of minimum edge rule.

implementation work, but it is possible, and the experiments in this work are evidence of this.

#### 2.3.2.1 Design Rules

This section presents some common design rules handled in detailed routing. Each layer, metal or cut, has a set of design rules. These rules can be grouped in two main categories: *shape rules* and *spacing rules*. Shape rules impose constraints in the shape of the objects. Spacing rules require the objects to obey a minimum distance from each other that may be influenced by many factors. There are also the *overlapping rules*, which impose restrictions on the overlapping between shapes, but they will not be treated here.

The *minimum area* is an example of a shape rule. It requires that any polygon in a metal layer meet a minimum area. The *minimum edge* rule is another example. In this case, two consecutive shape edges that do not meet a minimum length are forbidden. Figure 7 illustrates this rule. Also, any shape must respect a *minimum width*. The default wires of a metal layer have this width.

The *parallel runlength* is a spacing rule that requires that two metal shapes respect a minimum spacing from each other. The thicker the shapes, the higher is the spacing. The same way, the higher is the extent that both shapes run in parallel (i.e. the parallel runlength), the higher is the spacing. A spacing table defines these values. The rows and columns are the widths and parallel runlength ranges, and the table values are the required spacing. The minimum spacing value of the table is the default minimum spacing between any object. Usually, this spacing value plus the minimum width rule value, which is the default wire width, result in the *pitch* of the metal layer. The pitch is the distance between the grid points of the routing grid. Sometimes the

Figure 8- Illustration of the parallel runlength rule.

Figure 9- Illustration of the parallel runlength rule with a polygon with multiple rectangles.

pitch can be higher than this sum.

Figure 8 shows examples of the parallel runlength rule. "Width 1" and "Width 2" are widths of the width ranges 1 and 2 of the spacing table. The same way, the "Prl" represents the parallel runlength between both objects. Spacing[w][p] is the required spacing between two objects; w is the index of the width range that contains the greater width of the two objects and p is the index of the parallel runlength range that contains the parallel runlength of the two objects. The width of an object is the lesser side of the rectangle.

A metal object may be a polygon, defined by many rectangles. In this case, it may present parts that trigger different spacing values on the spacing table, due to their different widths. This is shown in Figure 9. The spacings shown are width-

Figure 10- Illustration of the cut spacing rule with adjacent via cuts constraint. The via cut 0 requires spacing of *adjSpacing* if there are 3 or more via cuts touching *cutWithin* radius.

Figure 11- Illustration of end-of-line rules. (a) is the simple case and (b) with parallel edge modifier.

dependent only, as the parallel runlength itself, between two objects, is ignored. An object passing by this polygon must be aware of all of its parts in order to avoid violations. The parallel runlength is measured in each part separately.

The *cut spacing* specifies the minimum spacing between two via cuts. This value is usually higher than the minimum wire spacing. The cut spacing rule may present some modifiers, like the *adjacent cuts*. A cut spacing with, say, 3 adjacent cuts means that this spacing is only applied when there is 3 via cuts in a given radius. Figure 10 illustrates the cut spacing rule with adjacent cuts constraint.

The end-of-line rule requires special spacing from a shape edge that has less than a determined size. Figure 11 shows examples of this rule. The red segment is the end-of-line edge. Any object in the red dashed rectangle causes a violation. The rule may present some modifiers, like the *parallel edges*. In Figure 11b, the parallel edges modifier is used, meaning that it is necessary to exist an object in any of the two blue rectangle areas in order to trigger the spacing requirement. If the modifier is set to *two edges*, then both blue rectangles must be intersected to trigger the spacing.

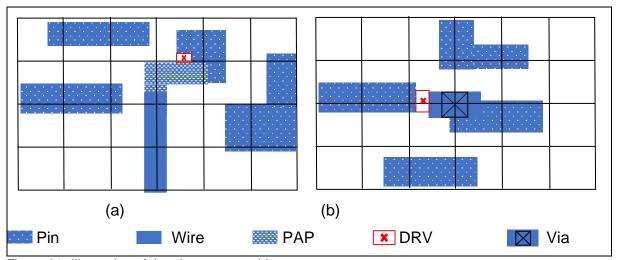

The pitch of the routing grid ensures that the wires of default width do not present violations with each other. Thus, the violation possibilities are in whatever objects with a width and/or with a spacing requirement greater than the minimum. These objects are pins, obstructions, non-default wires and vias. Thus, the major attention in avoiding DRVs is in the pin access and in the path search, since the paths need vias to connect the wires of different layers.

The ISPD18 benchmarks, adopted in the experiments of this work, use a simplified set of the mentioned design rules. The rules are: (1) minimum area; (2) cut spacing (no adjacent cuts); (3) end-of-line (no parallel edges); (4) parallel runlength, ignoring the parallel runlength itself, varying only the widths. Also, there are no non-default wires.

### 3 Detailed Routing Literature

This section presents a literature review of detailed routing. Section 3.1 presents detailed routing approaches and techniques. Considering that path search is a fundamental building block of detailed routing, and that part of the contributions of this work is related to path search, section 3.2 presents path search related algorithms. Pin access is also another important step of detailed routing, and since it is one of the main contributions of this work, section 3.3 presents pin access techniques.

### 3.1 Detailed Routing Approaches and Techniques

Detailed routing is a problem that can be solved in many ways. Over the history of routing in integrated circuits, many approaches and techniques were used. In the old days, when the number of layers available for routing was two or three, routing was solved using the channel routing approach. With the change of paradigm to the current one (over-the-cell routing), the resolution of the detailed routing problem is more flexible, presenting many different approaches.

The detailed routing methodologies may be grouped in some categories, according to the routing *order* of the nets, the use of a predefined *grid*, and the awareness of manufacturing peculiarities that improve *yield*.

Regarding the routing order, there are the sequential (also called net-by-net) and the concurrent approach. In the sequential one, the nets are routed one after another, such that previously routed nets form obstacle to the new ones. Nets that could not have a route found are rerouted in RNR (SHIN, 1987) step, as in global routing, in which nets are routed possibly ripping out other nets. The sequential routing tends to present a favorable runtime, but this can be compensated by the RNR step. The routing order of the nets has a high impact in the number open nets (i.e., nets that could not complete a connection). Thus, in order to properly work, this methodology relies on a good net ordering.

The concurrent approach routes all net pieces in some routing regions simultaneously. It is better at handling high congested areas, but it tends to present higher runtime than the sequential methodology. It is still possible to present open nets and rely on RNR, but much less than in the sequential approach. The concurrent routing is easier to parallelize than the sequential one.

Regarding the routing space modeling, most approaches use a predefined grid. This facilitates the implementation and tends to provide faster runtime than gridless

approaches. The main argument of gridless routing is that it naturally handles design rules better, mainly the less common ones.

Some routing approaches focus on optimizing good practices that may impact on the manufacturing yield. Examples are routers that try to use multi-cut vias and the ones that attend to the multiple patterning constraints (DING; YU; YUAN; GAO; MIRSAEEDI; MA; LIU, 2018, 2018, 2009, 2010, 2011, 2012, 2016).

## 3.1.1 Channel and Switchbox Routing

In the old routing paradigm, between each row of logic gates there was a space, called *channel*. The pins of the cells were located at the cell border adjacent to the channel. The connections between the cells were performed on the channels. Two metal layers were used, at first.

A channel is a rectangle with pins at two of its opposing borders. As the complexity of the circuits increased, not all connections could be performed on the same channel. The routing space was divided in rectangles, called *switchboxes*, with connections at the four borders. Figure 12 shows an example of a switchbox routed.

The first channel routing algorithm was the Left-Edge (HASHIMOTO, 1971). Later, (DEUTSCH, 1976) proposed the Dog-Leg algorithm, which was an improvement over Left-Edge. The switchbox routers (JOOBBANI; LUK; MAREK-SADOWSKA; HAMACHI, 1986, 1985, 1985, 1984) derive from the channel routers. The basic procedure of channel routing is the following. First, a horizontal constraint graph is built

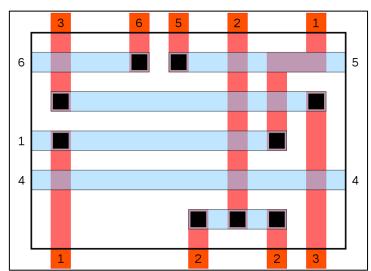

Figure 12 – Illustration of a switchbox routed. Blue and red represent the different metal layers, and the black squares are the vias. The terminals are labeled by numbers representing their respective net.

in order to detect the minimum number of routing tracks needed to make the routing feasible. Second, a vertical constraint graph is built, aiming to provide a topological order of pin connections to be routed. Finally, the connections are implemented following the vertical constraint graph topology and respecting the constraints of the horizontal constraint graph.

With the increase in circuit complexity, the routing channels had to become even larger in height, which would increase the circuit area. Thus, a third metal layer was introduced. In this layer, wires were allowed to be put over the cells. Several over-the-cell channel routers were proposed (CONG, Jason; HOLMES; CONG, J.; NATARAJAN; WU; 1990, 1991, 1990, 1992, 1992). However, this was not enough to handle the wire congestion that was constantly increasing. Thus, more metal layers were introduced, and the routing space assigned to the channels became pointless, causing the end of channel routing.

#### 3.1.2 Over-the-Cell Routing Using Gcells as Switchboxes

In the time of channel routing, global routing worked on irregularly partitioned regions, constituted of channels and switchboxes. With the change of paradigm, global routing partitioned the routing area regularly in gcells, as already shown in Figure 4. A path obtained in global routing is a sequence of gcells, called global routing guide, connecting all net pins. In detailed routing, the routing of a net is restricted to the region denoted by this set of gcells. Considering the sequential paradigm, in order to route a net, it is necessary to use a path search to connect all of its components (pins and wires). Since these components may be far away from each other, this may cause high runtime overheads in some path search algorithms. Thus, one detailed routing approach is to decompose these long connections into smaller connections, one for each gcell (IGUSA; PARNG, 1989, 1989). Each gcell, work as a switchbox, with pseudopins at its boundaries, as shown in Figure 13. Pseudopins are terminals that act like pins. This approach gave rise to the Cross-Point Assignment (CPA) problem (KAO; CHANG, 2001, 1995).

The CPA, also called Pseudopin Assignment, is an intermediate step between global and detailed routing, aiming to determine the positions of the pseudopins at the gcells boundaries. An advantage of this approach is that it allows a good level of parallelism, since it is possible to route each gcell separately. This methodology can

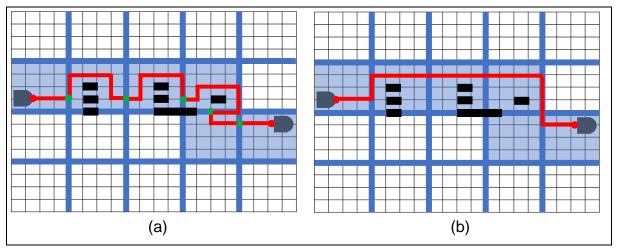

Figure 13- Illustration of routing each gcell as a switchbox and the problem involved in the crosspoint assignment. The gcell grid is denoted by the thick blue lines. The global routing guide is in translucid blue. A path (in red) connects two cells. The green points are the crosspoints (or pseudopins). In (a), it is possible to see the WL increase that may happen in this approach, due to the decomposition of the searches. In (b) it is shown the optimal solution.

be either sequential or concurrent. That is, it is possible to route all connections of all pseudopins of a gcell, each time one is processed (concurrent approach), or it is possible to consider one net at each time (sequential approach) and perform the connections of all gcells in the global routing guide. The mentioned parallelism is independent of the approach.

A disadvantage of this approach is that it provides bad results in terms of WL, as shown in Figure 13a. Since a connection is decomposed, the global view of the full connection is lost and thus, the optimal path cannot be guaranteed. This methodology became less popular with the emergence of more modern approaches (as in the next sections), which performed long connections more efficiently.

#### 3.1.3 Sequential Routing Using Path Search for Long Connections

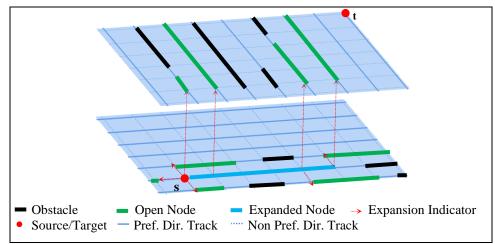

The justification of the path decomposition of the previously commented approach is that, the path search algorithms available in that time were not satisfactory to handle long connections. The maze search algorithms are known to present a high processing time, which is proportional to the available search space. The line probe algorithms are faster, but don't guarantee the optimal path and cannot handle variable grid point (and graph edge) costs. As will be shown in section 3.2.4, Hetzel's algorithm (HETZEL, 1998) uses line segments and is goal oriented, using A\* technique. In the current work, this kind of path search is called A\*-interval-based path search. With this algorithm, there is no reason to decompose the pin connections. Another possibility is to preprocess the global routing guide area to create an optimized graph for a Dijkstra-

based (CORMEN, 2001) path search algorithm, as in (CHEN, 2019a, 2019b). However, as the experiments in this work suggest (section 7), the time spent in constructing such graph does not compensate the runtime improvement of using an interval-based path search.

The sequential detailed routing methodology is the following. First, the nets are ordered in a priority queue. As mentioned earlier, a good net order is very important for a good routing. A good criterion for net ordering is related to the routing area of the global routing guides or the estimated WL of the net. Routing nets with less area (or WL) first theoretically tends to present good results, since a lower area net has less freedom to perform the connections. However, in practice, routing nets with more WL first may be better. Since the routing guides of all nets have the same width, the net length factor weights more than the routing area factor. Also, longer nets have most of their routes in higher metal layers, using lower layers only for pin access, while shorter nets tend to use more the lower layers. This makes longer nets present few blockages to shorter nets, if they are routed first, while routing first shorter nets presents more blockages to longer nets.

After the net ordering, the nets are sequentially routed. Since a net can have multiple pins, it is decomposed in two pin nets. This decomposition may be performed at the routing procedure begin, before net ordering, or after a net is selected for routing. Each two-pin net is restricted to a section of the global routing guides, which is called *tunnel* in this work. The two-pin net is routed and the resulting path is inserted into the routing space. Open nets are handled in the RNR step, as mentioned earlier. The path searches in RNR may rip other nets, and the process continues until all nets are routed or some other criterion, like a runtime limit, is met. In order to avoid RNR loops, the path search is penalized when routing through other wires. Another good practice is using a Negotiation-based technique (KAHNG, 2011d) in which the routing space stores a cost history of the wires that were already inserted on it. Thus, congested regions present higher penalty cost for the path search.

In the sequential approach, parallelization is less trivial than in the concurrent one, but it is still feasible. (CHEN, 2019a, 2019b) proposes to route, in parallel, batches of nets that do not present routing guide overlapping with each other. After a batch is routed, all found paths are inserted into the routing space, and the next batch is chosen, and so on.

Examples of sequential routers are (SHIN, 1987), (HETZEL, 1998), BonnRoute (GESTER; AHRENS, 2013, 2015), and (CHEN, 2019a, 2019b).

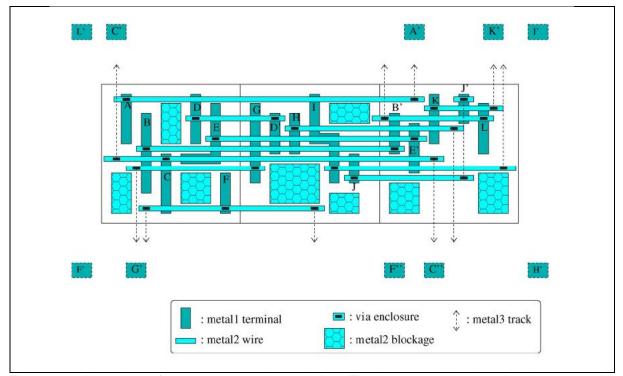

# 3.1.4 Track Assignment

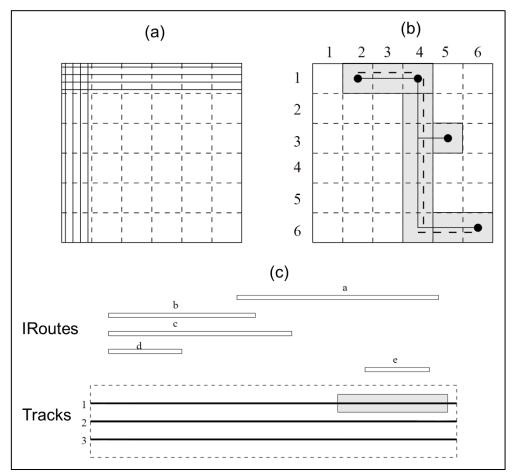

Track Assignment (TA) was proposed in (BATTERYWALA, 2002) as an intermediate step between global and detailed routing. It is closer to detailed routing than global routing, though. Consider Figure 14. Each row of gcells of a global routing guide is called *global segment*. An *iroute* (or *ir*) is a wire segment from detailed routing used to implement the global segment. A *panel* is the region denoted by an entire line or column of gcells of the global routing graph, following the preferred routing direction. The track assignment problem consists in assigning all *ir*'s of a panel to routing tracks without overlapping *ir*'s of different nets.

The first step of TA is to group all *ir*'s to their respective panels. Then, each panel is processed separately. This allows a good level of parallelization. For a given

Figure 14 – Illustration of the Track Assignment problem. (a) Vertical and horizontal panels in global routing grid. (b) The global routing guides of a net (in grey), its global segments (dashed lines), its iroutes (lines), and its pins (dots). (c) Track assignment example. The grey rectangle is an obstacle. Source: (BATTERYWALA, 2002).

Figure 15 – Illustration of the graphs used in the TA technique. (a) irou-te overlap graph. (b) bipartite assignment graph. (c) combined graph model.

panel, an iroute overlap graph is constructed (Figure 15a). Each vertex of this graph is an *ir* and the edges are their overlaps. Then, this graph is extended to a bipartite assignment graph (Figure 15b), where one set of vertices is composed by the *ir*'s and the other set contains the tracks. The edges connecting both sets represent the availability of assigning an *ir* to a track. The weight of these edges represents the cost of assigning the *ir* to the track. These costs are modeled by many factors, such as obstruction costs, long wire penalties in some cases, and anchor costs (wires and pins of the same net should be as close as possible).

Since the optimal track assignment solution is NP-Complete (BATTERYWALA, 2002), a heuristic is used to solve the problem. In an iterative procedure, the largest cliques<sup>1</sup> of the iroute overlap graph are selected, and their *ir*'s are assigned to different tracks, by modeling this task as a weighted bipartite matching problem and solving it using the shortest augmenting path algorithm of Jonker and Volgenant (1987). The combined graph (Figure 15c) is updated by removing the assigned *ir*'s and their edges linking to the tracks.

After the track assignment step, detailed routing is performed to connect the pieces of the nets. Since the longer connections were already performed by TA, the path search algorithm (even a maze search one) does not encounter great difficulties to find the routes.

In 2013, Zhang (2013) proposed a detailed router, called RegularRoute, based on TA. However, it does not use TA as an intermediate step between global and

-

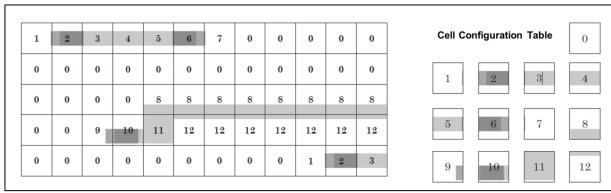

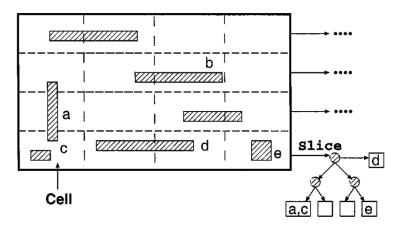

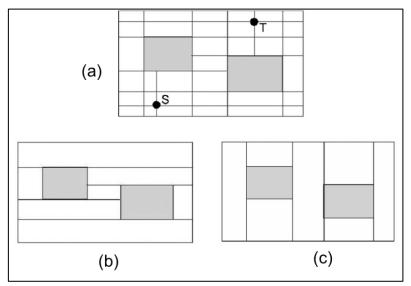

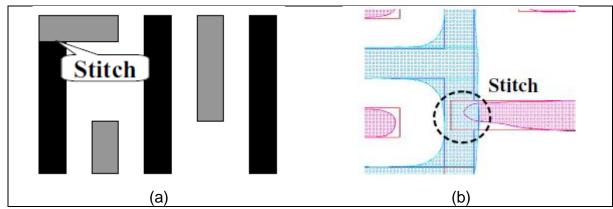

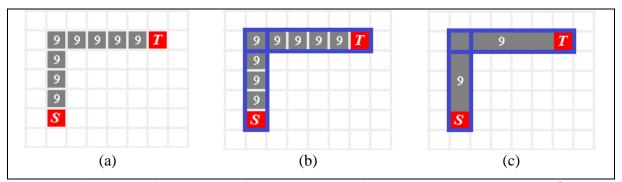

<sup>&</sup>lt;sup>1</sup> A clique is a set of vertices in an undirected graph such that any pair of vertices is connected by an edge.