# UNIVERSIDADE FEDERAL DE PELOTAS Centro de Desenvolvimento Tecnológico Programa de Pós-Graduação em Computação

Tese

# <u>FPGA-Enabled Heterogeneous System Simulation</u> for Early Design Space Exploration

**Carlos Michel Betemps**

#### **Carlos Michel Betemps**

# <u>FPGA-Enabled Heterogeneous System Simulation</u> for Early Design Space Exploration

Tese apresentada ao Programa de Pós-Graduação em Computação do Centro de Desenvolvimento Tecnológico da Universidade Federal de Pelotas, como requisito parcial à obtenção do título de Doutor em Ciência da Computação.

Advisor: Prof. Dr. Bruno Zatt

Coadvisores: Prof. Dr. Daniel Munari Vilchez Palomino

Prof. Dr. Marcelo Schiavon Porto

#### Universidade Federal de Pelotas / Sistema de Bibliotecas Catalogação na Publicação

#### B562f Betemps, Carlos Michel

FPGA-Enabled heterogeneous system simulation for early design space exploration / Carlos Michel Betemps; Bruno Zatt, orientador; Daniel Munari Vilchez Palomino, Marcelo Schiavon Porto, coorientadores. — Pelotas, 2021.

156 f.: il.

Tese (Doutorado) — Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, 2021.

1. Heterogeneous system simulator. 2. PGA simulation. 3. Early design space exploration. 4. Dynamic and partial reconfiguration. 5. Partially reconfigurable regions. I. Zatt, Bruno, orient. II. Palomino, Daniel Munari Vilchez, coorient. III. Porto, Marcelo Schiavon, coorient. IV. Título.

CDD: 005

#### **Carlos Michel Betemps**

# <u>FPGA-Enabled Heterogeneous System Simulation</u> for Early Design Space Exploration

Tese aprovada, como requisito parcial, para obtenção do grau de Doutor em Ciência da Computação, Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas.

**Data da Defesa:** 15 de março de 2021 (March 15, 2021)

#### **Banca Examinadora:**

Prof. Dr. Bruno Zatt (orientador)

Doutor em Microeletrônica pela Universidade Federal do Rio Grande do Sul.

Prof. Dr. Daniel Munari Vilchez Palomino (co-orientador)

Doutor em Computação pela Universidade Federal do Rio Grande do Sul.

Prof. Dr. Marcelo Schiavon Porto (co-orientador)

Doutor em Computação pela Universidade Federal do Rio Grande do Sul.

Prof. Dr. André Luís Del Mestre Martins

Doutor em Ciência da Computação pela Pontifícia Universidade Católica do Rio Grande do Sul.

Prof. Dr. Mateus Beck Rutzig

Doutor em Computação pela Universidade Federal do Rio Grande do Sul.

Prof<sup>a</sup>. Dr<sup>a</sup>. Lisane Brisolara de Brisolara

Doutora em Ciência da Computação pela Universidade Federal do Rio Grande do Sul.

Dedico este trabalho ...

... a minha família – Carla, Heitor, Davi e Miguel

– vocês representam a minha essência

... ao meu pai e irmãos – Carlinhos, Daniel e

Maurício – vocês são minha origem e referência

... a memória de minha mãe – Maria Irene – suas

lembranças e doces palavras ainda guiam meu ser

... a memória de meus avós e padrinhos

Domingos e Tereza e minha avó Nair

#### **AGRADECIMENTOS**

Primeiramente, agradeço ao Bruno Zatt pela troca de experiências e orientação durante este trabalho. Sua perspectiva e conhecimento da área foram essenciais para o desenvolvimento desta tese. Da mesma forma, agradeço ao Daniel Palomino e Marcelo Porto pela co-orientação e por trazerem suas diferentes visões para o contexto do trabalho.

Agradeço aos colegas Mateus Melo e Douglas Costa por compartilharem seus conhecimentos e dedicação em atividades relacionadas a este trabalho. Também agradeço aos demais colegas do PPGC, em especial ao Wagner Penny, Ruhan Conceição e Renato Souza pela acolhida e conversas no dia a dia do laboratório.

Gostaria de agradecer a todos os docentes do PPGC/UFPel, em especial aos professores Julio Mattos, Lisane Brisolara, Paulo Ferreira, Gerson Cavalheiro e Mauricio Pilla por compartilharem suas ideias e conhecimentos nas suas disciplinas do PPGC. Agradeço também a UFPel, instituição que me acolheu durante minha graduação e que também possibilitou o ingresso e formação nesta etapa de doutoramento em minha vida como docente universitário.

Agradeço aos colegas docentes do curso de Engenharia de Computação do Campus Bagé da UNIPAMPA pelo apoio na concretização do doutoramento. Em especial, agradeço a Universidade Federal do Pampa - UNIPAMPA pelo apoio institucional na formação de seus docentes.

Agradeço a todos que direta ou indiretamente me apoiaram para que fosse possível desenvolver este trabalho e todas suas atividades inerentes.

Por fim, como um ato de fé, agradeço a Deus pelas oportunidades de aprendizado que se apresentaram em minha vida e por todas as conquistas alcançadas.

. . .

Different eyes see different things Different hearts Beat on different strings

. . .

— GEDDY LEE (RUSH)

#### **ABSTRACT**

BETEMPS, Carlos Michel. <u>FPGA-Enabled Heterogeneous System Simulation</u> for Early Design Space Exploration. Advisor: Bruno Zatt. 2021. 156 f. Thesis (Doctorate in Computer Science) – Technology Development Center, Federal University of Pelotas, Pelotas, 2021.

Heterogeneous systems architectures usually include processing elements such as Central Processing Units and General Purpose Graphics Processing Units, frequently enabling optimization opportunities in terms of execution time, consumed energy, resource utilization, and throughput. In turn, the heterogeneity brings a series of new design challenges when compared to homogeneous systems. An even more challenging scenario appears when such heterogeneous systems feature hardware acceleration through dynamic and partial FPGA (Field Programmable Gate Array) reconfiguration. This work presents a Modeling and Simulation infrastructure for early Design Space Exploration (DSE) of heterogeneous systems by comprising a methodology to create high-level models of the system and a simulator complying with those models. A designer can partition an FPGA into Partially Reconfigurable Regions (PRRs) that can pass through a Dynamic and Partial Reconfiguration (DPR) during runtime. Considering those aspects, the modeling methodology contains the flow and automatic hardware generation to annotate our simulation models. FEHetSS is an FPGA-Enabled Heterogeneous System Simulator aiming to provide support for decision making in early design phases. We describe FEHetSS presenting its structure, models, and simulation flow. FEHetSS considers the tasks' latencies even those related to reconfiguration, also estimating the processing elements' power and resource utilization. Based on case studies, we demonstrate the methodology and FEHetSS's potentialities. First, we model heterogeneous systems and use FEHetSS as a tool to evaluate single-points in early DSE. Second, we conceive distinct hardware design (e.g., pipelining and parallelism) models for an application kernel and utilize FEHetSS as a tool to assist designers considering a holistic system perspective. Third, we restrict a couple of design spaces applying FEHetSS to perform exhaustive exploration. Last, we prepare a DSE environment integrating an optimization heuristic and FEHetSS, performing simulations based on exploration parameters. Case studies' results and analysis demonstrate the infrastructure features in the modeling and simulation of FPGA-enabled heterogeneous systems.

Keywords: Heterogeneous System Simulator. FPGA Simulation. Early Design Space Exploration. Dynamic and Partial Reconfiguration. Partially Reconfigurable Regions.

#### **RESUMO**

BETEMPS, Carlos Michel. Simulação de Sistemas Heterogêneos Habilitados para FPGA visando Exploração Precoce do Espaço de Projeto. Orientador: Bruno Zatt. 2021. 156 f. Tese (Doutorado em Ciência da Computação) — Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, Pelotas, 2021.

Arquiteturas de Sistemas Heterogêneos usualmente incluem CPUs e GPUs como elementos de processamento habilitando oportunidades de otimização no tempo de execução, energia consumida, utilização de recursos e desempenho. Em comparação ao projeto de sistemas homogêneos, novos desafios surgem com a heterogeneidade, sendo estes potencializados pela inclusão de aceleradores de hardware como FPGAs. Este trabalho apresenta uma infraestrutura de Modelagem e Simulação em alto nível para a Exploração Precoce do Espaço de Projeto de sistemas heterogêneos habilitados para incluir dispositivos FPGA. Tais dispositivos podem ser particionados em Regiões Parcialmente Reconfiguráveis (PRR) que, por sua vez, podem passar por Reconfiguração Dinâmica e Parcial (DPR). Considerando esses aspectos, a metodologia inclui o fluxo de modelagem e a geração automática de hardware necessários às anotações dos modelos de simulação. FEHetSS é um simulador de sistemas heterogêneos habilitado para FPGAs que fornece suporte à tomada de decisão em estágios iniciais de projeto, sendo este detalhado em relação a sua estrutura, modelos e fluxo de simulação. Nas simulações são consideradas as latências das tarefas de aplicação e aquelas referentes às reconfigurações, assim como o consumo energético e utilização de recursos do sistema. Estudos de caso demonstram as capacidades da infraestrutura. Primeiro, foram criados modelos de sistemas heterogêneos para simulação via FEHetSS atuando como uma ferramenta de avaliação na exploração precoce do espaço de projeto. Segundo, foram concebidos diferentes modelos de hardware para o kernel de uma aplicação exemplo, sendo estes submetidos ao FEHetSS para a avaliação do projeto em uma perspectiva holística do sistema. Terceiro, foram definidos parâmetros de busca restringindo o espaço de projeto para exploração exaustiva com FEHetSS. Por último, FEHetSS foi integrado em um ambiente gerenciado por heurística de otimização visando a exploração baseada em parâmetros do espaço de projeto. Os resultados e respectivas análises demonstraram as potencialidades da infraestrutura na modelagem e simulação de sistemas heterogêneos habilitados para FPGAs dinamicamente reconfiguráveis e particionados em PRRs.

Palavras-chave: Simulador de Sistemas Heterogêneos. Simulação FPGA. Antecipada Exploração do Espaço de Projeto. Reconfiguração Dinâmica e Parcial. Regiões Parcialmente Reconfiguráveis.

### **LIST OF FIGURES**

| 1 2 | Thesis Contributions Context                                                                                                                                                                | 23<br>26 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 3   | Embedded Systems Design                                                                                                                                                                     | 28       |

| 4   | Pareto Front and Domination relation considering the objective functions f1 and f2, excerpted from (PIMENTEL, 2017).                                                                        | 30       |

| 5   | Y-Chart Approach (based on GRIES (2004))                                                                                                                                                    | 31       |

| 6   | Abstractions Levels of Simulation considering the Computation (a) – of the Processing Components – and the Communication (b) between the System Components (adapted from PIMENTEL (2017)) . | 36       |

| 7   | OpenCL Platform Model (extracted from KAELI et al. (2015))                                                                                                                                  | 38       |

| 8   | FPGA Architecture – Layers (extracted from VIPIN; FAHMY (2018)).                                                                                                                            | 39       |

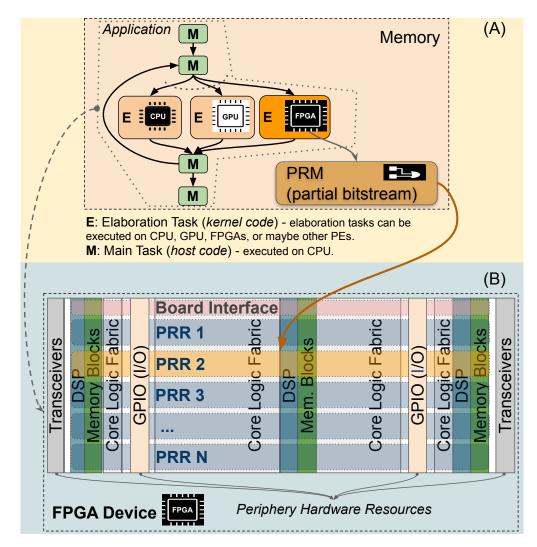

| 9   | PRRs, PRMs, board interface, and periphery HW. (A) Application                                                                                                                              |          |

|     | model and partial bitstream. (B) FPGA device model                                                                                                                                          | 40       |

| 10  | Overview of the CLASSY Tool (AN; GAMATIÉ; RUTTEN, 2015)                                                                                                                                     | 45       |

| 11  | Multilayer Approach using the AADL Extension (BLOUIN et al., 2011)                                                                                                                          | 46       |

| 12  | SAVE Framework: (A) Application Task Graphs. (B) Simulator Struc-                                                                                                                           |          |

| 10  | ture in SystemC/TLM (MIELE et al., 2015)                                                                                                                                                    | 48       |

| 13  | The Proposed Method for GA-based DSE Using Parallel DEVS Formalism to Evaluate the Condidate Solutions (NOCLIFIED et al., 2016)                                                             | 49       |

| 14  | malism to Evaluate the Candidate Solutions (NOGUEIRA et al., 2016)<br>The COMPLEX Reference Framework (GRÜTTNER et al., 2013)                                                               | 50       |

| 15  | FoRTReSS Overview (DUHEM et al., 2015)                                                                                                                                                      | 51       |

| 16  | rSesame Model for a Generic Reconfigurable Architecture (SIGDEL                                                                                                                             | <b>.</b> |

|     | et al., 2009b)                                                                                                                                                                              | 52       |

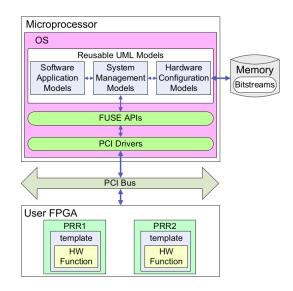

| 17  | UCoP UML-based HW/SW Co-design Platform (HUANG; HSIUNG;                                                                                                                                     |          |

|     | SHEN, 2010)                                                                                                                                                                                 | 53       |

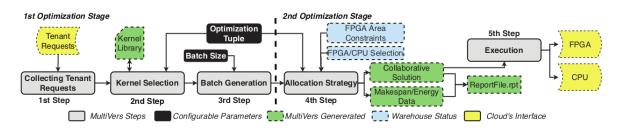

| 18  | MultiVers Framework Overview (LIGNATI et al., 2021)                                                                                                                                         | 53       |

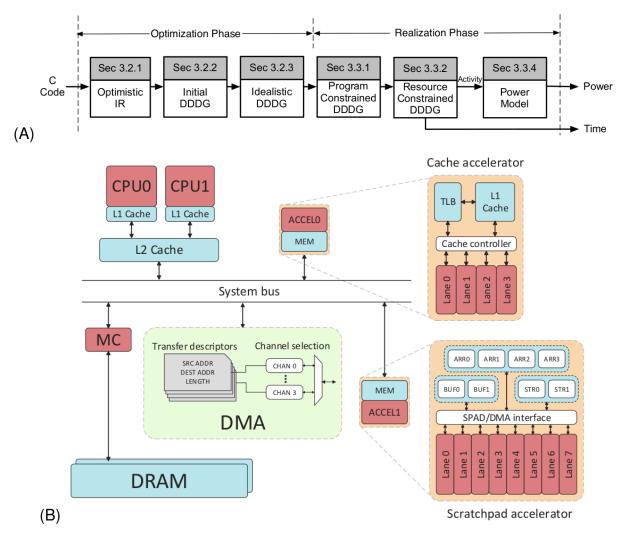

| 19  | (A) The Aladdin Framework Overview (SHAO et al., 2014). (B) A                                                                                                                               |          |

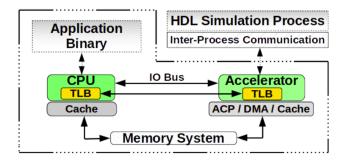

| 00  | SoC Architecture Sample in gem5-Aladdin (SHAO et al., 2016)                                                                                                                                 | 54       |

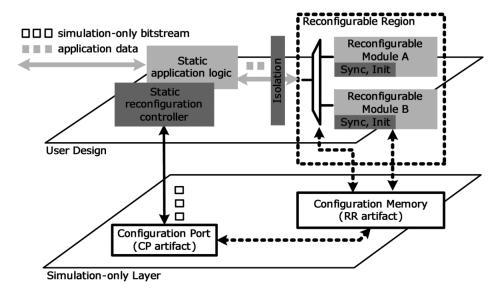

| 20  | ReSim Simulation Artifacts – Simulation-only Bitstream and Simulation-only Layer (GONG; DIESSEL, 2014)                                                                                      | 55       |

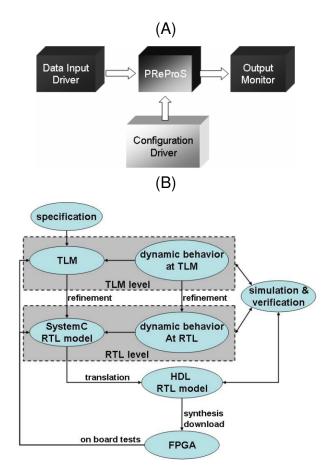

| 21  | (A) PRePros Overview (BRITO et al., 2007a) and (B) Adapted Sys-                                                                                                                             |          |

|     | temC Design Flow (BRITO et al., 2007b)                                                                                                                                                      | 56       |

| 22  | PAAS Architecture (LIANG et al., 2017)                                                                                                                                                      | 57       |

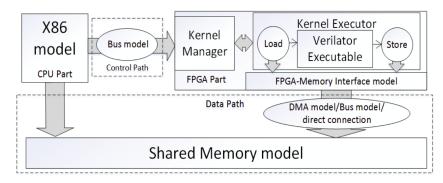

| 23  | HeteroSim Simulator Architecture (FENG et al., 2017)                                                                                                                                        | 57       |

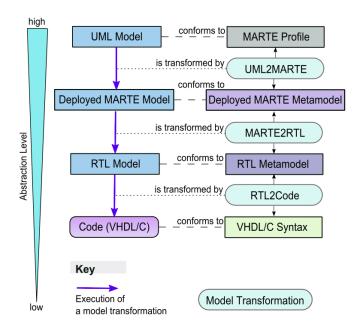

| 24  | The Model Transformation Chain in Gaspard2 (QUADRI et al., 2010)                                                                                                                            | 58       |

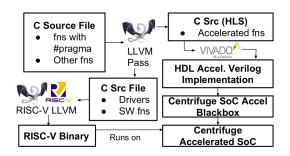

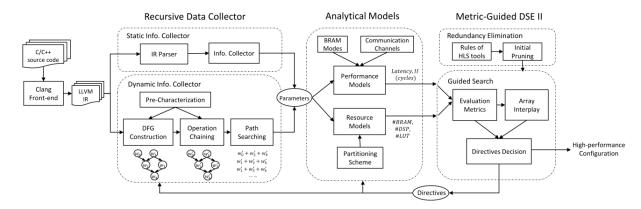

| 25  | Centrifuge HLS Flow and Tools (HUANG et al., 2019)                                                                                                                                          | 59       |

| 26                               | COMBA Framework (ZHAO et al., 2020)                                                                                                                                                                               | 60                         |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|

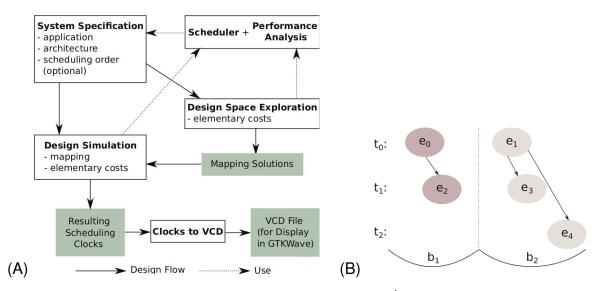

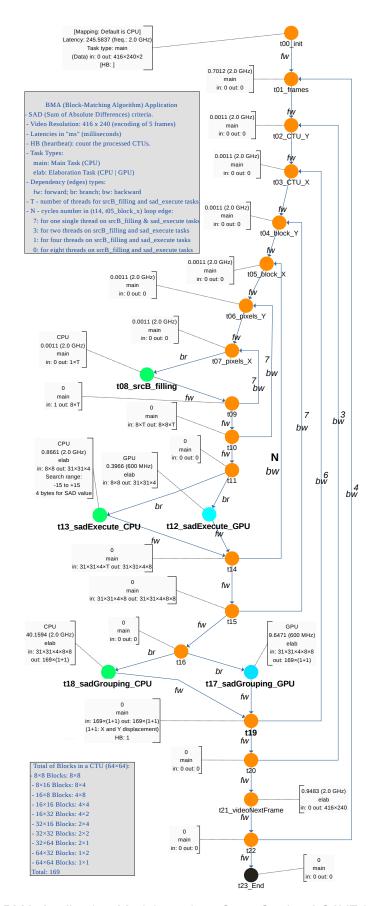

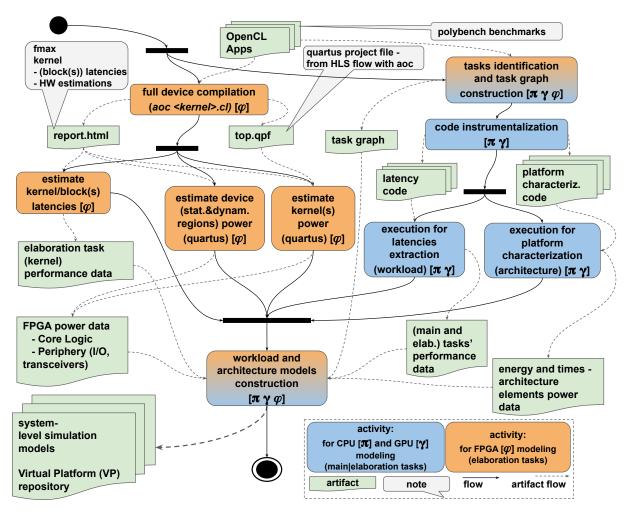

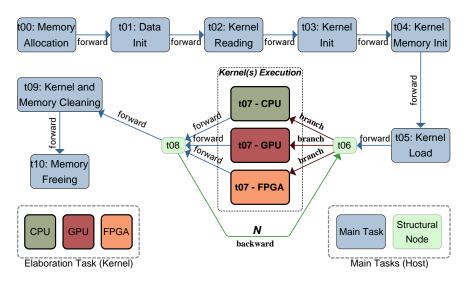

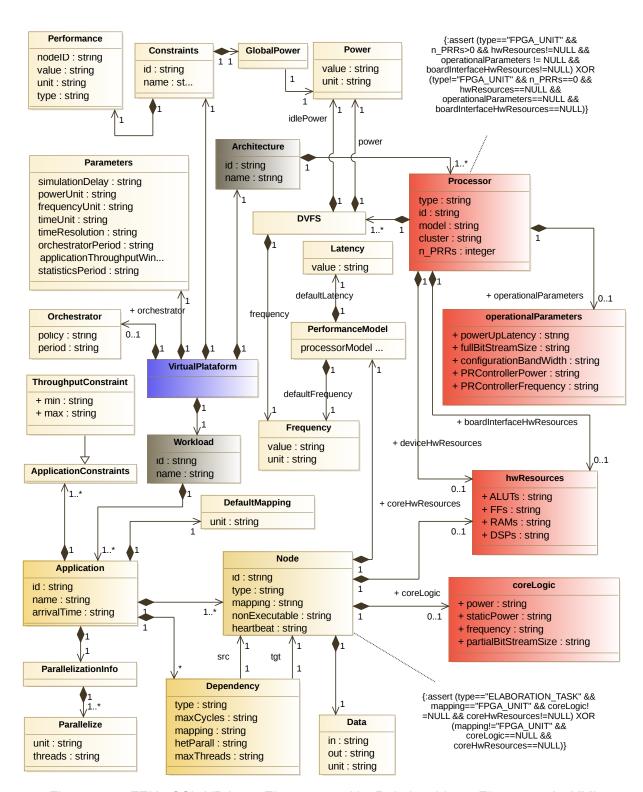

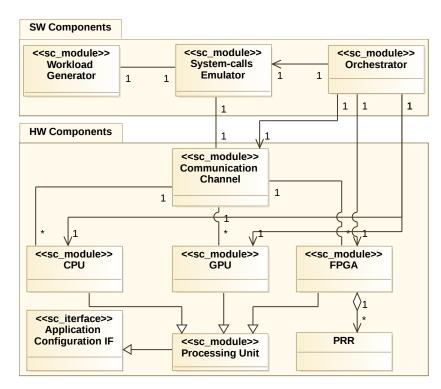

| 27<br>28<br>29<br>30<br>31<br>32 | Conceptual Elements and Main Contributions of the Thesis FEHetSS Framework's Flow                                                                                                                                 | 68<br>69<br>71<br>76<br>77 |

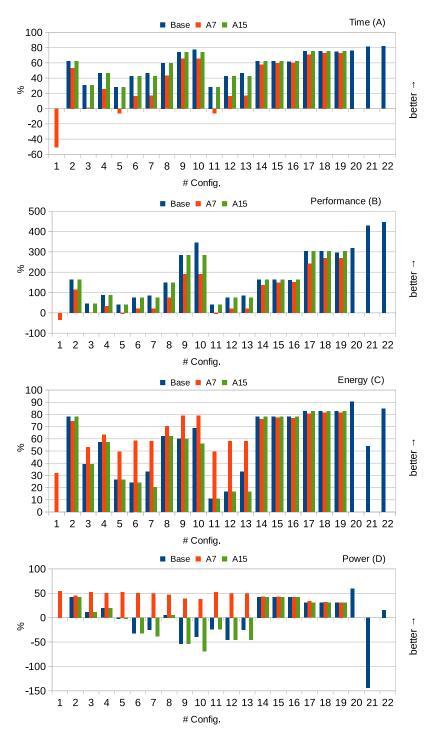

| 33                               | Percentage gains for time (A), performance (B), energy (C), and power (D) for each configuration in the three resource policies (Base, A7, and A15) with #1 in the Base policy as baseline (BETEMPS et al., 2018) | 80                         |

| 34<br>35                         | Methodology for VP Modeling                                                                                                                                                                                       | 82                         |

| 36                               | as Processing Elements                                                                                                                                                                                            | 86<br>87                   |

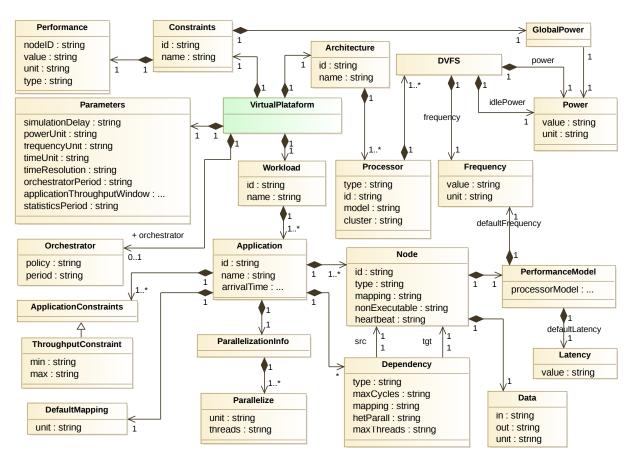

| 37<br>38                         | FEHetSS's VP Input Elements and its Relationships – Elements of a XML File describing a VP (Architecture and Workload) Main Components of FEHetSS System-level Simulator                                          | 89<br>90                   |

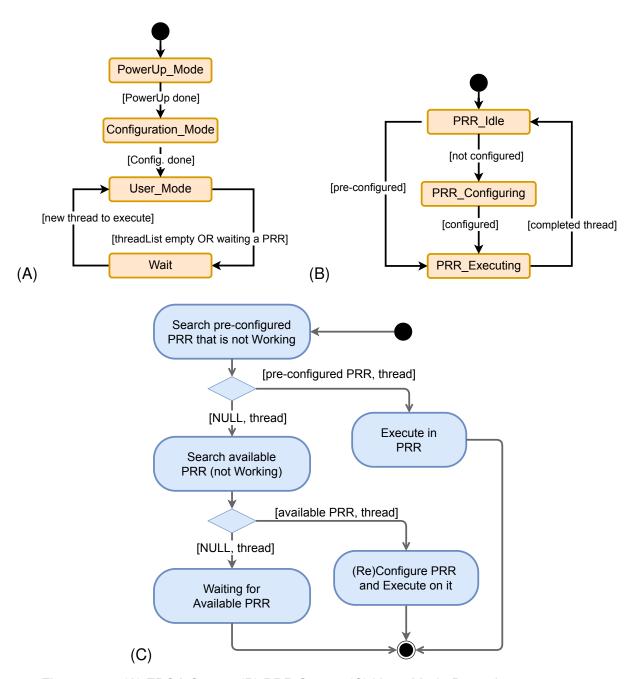

| 39                               | (A) FPGA States. (B) PRR States. (C) User_Mode Procedure                                                                                                                                                          | 91                         |

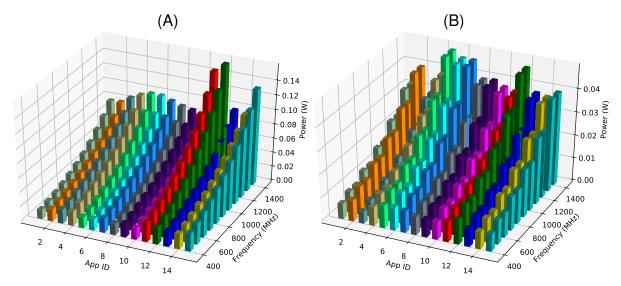

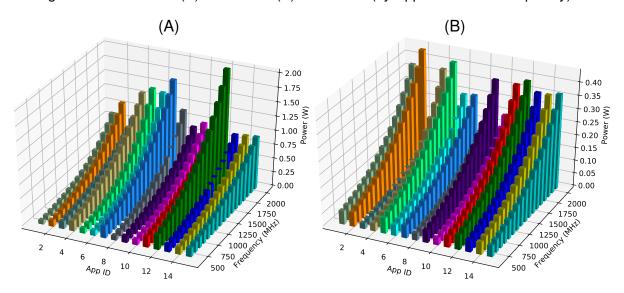

| 40<br>41                         | A7 Core: (A) Power and (B) Idle Power (by Application and Frequency) A15 Core: (A) Power and (B) Idle Power (by Application and Fre-                                                                              | . 97                       |

| 42                               | quency)                                                                                                                                                                                                           | 97<br>98                   |

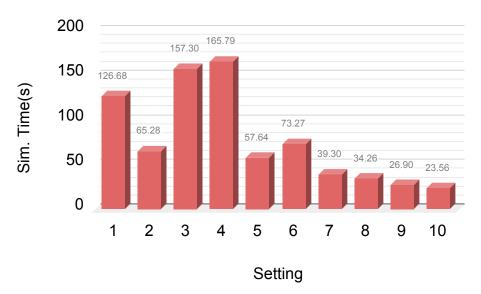

| 43                               | Energy vs Time vs Utilization of Case Study #1 - DSE Settings (1-10 of Tab. 12)                                                                                                                                   | 101                        |

| 44                               | Power Consumption (A and B) and HW Utilization (C and D) along time of each PE for settings 09 and 10, respectively (top to bottom).                                                                              | 103                        |

| 45                               | Power Consumption of Setting 09 detailing the Reconfiguration Points (top) of each PRR of the Arria10GX Device and the Appli-                                                                                     | 100                        |

| 46<br>47                         | cations Completions (bottom)                                                                                                                                                                                      | 104<br>105                 |

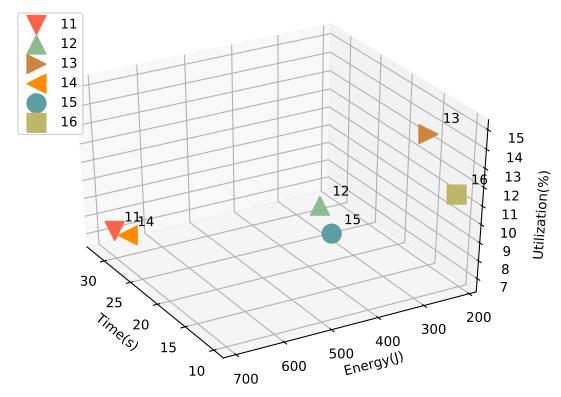

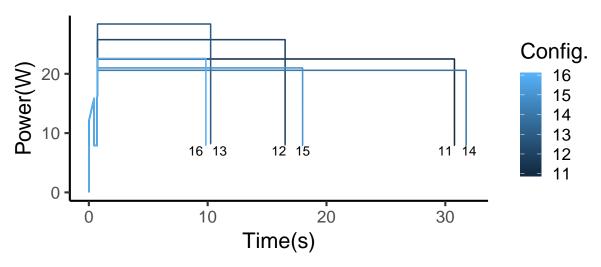

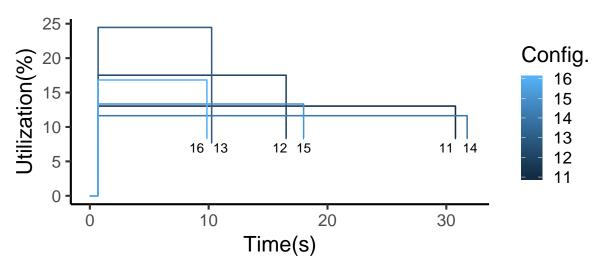

| 48                               | Tab. 13)                                                                                                                                                                                                          | 106<br>107                 |

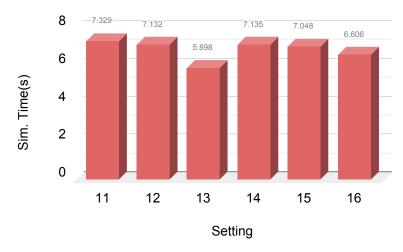

| 49<br>50                         | FPGA HW Utilization along Time (settings 11 to 16) Simulation Times for Settings 11 to 16                                                                                                                         | 107<br>108                 |

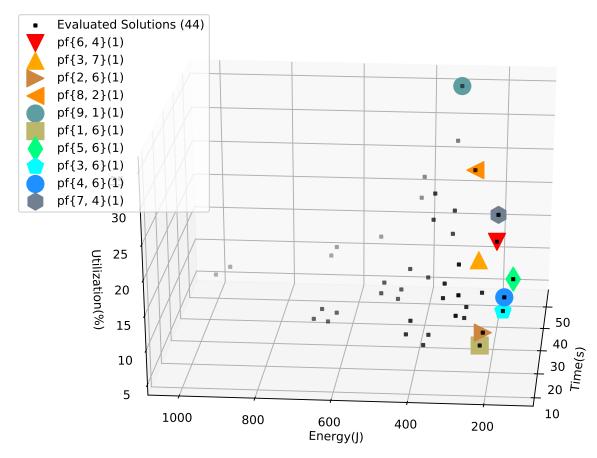

| 51                               | Exhaustive Search Regarding the Specific Device (D) and the HW Task Implementation (I) for Application 2MM (3) [ pf{D, I} – pf: Pareto Front ]                                                                    | 109                        |

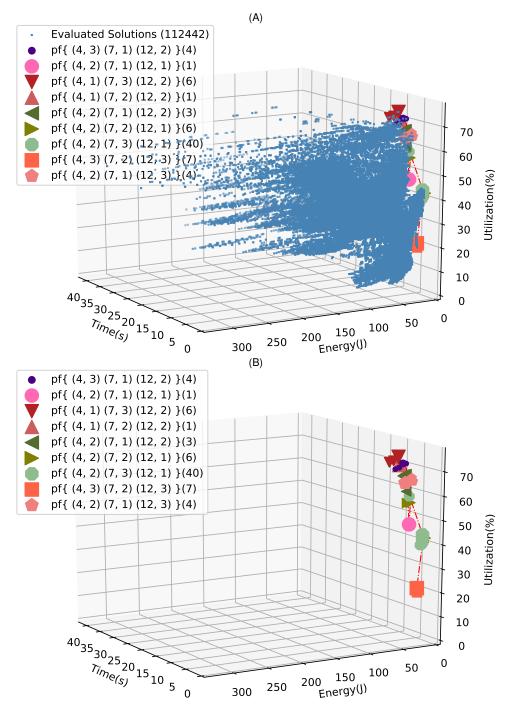

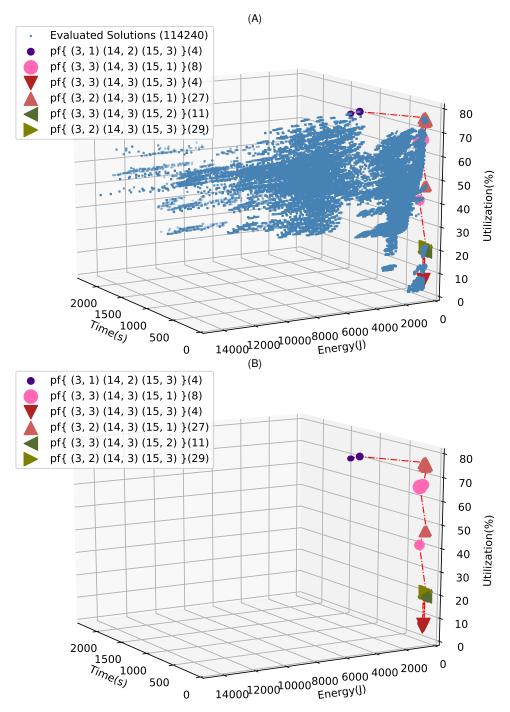

| 52                               | Case Study #3: (A) Exhaustive Search for Appl. 4, 7, and 12. (B) Only its Pareto Front (PF). {(Appl. ID, Map. PE),}(# Solutions). PE - 1: CPU; 2: GPU; 3: FPGA                                                    | 114                        |

| 53                               | Case Study #3: (A) Exhaustive Search for Appl. 3, 14, and 15. (B) Only its Pareto Front (PF). {(Appl. ID, Map. PE),}(# Solutions). PE - 1: CPU; 2: GPU; 3: FPGA.                                                  | 115                        |

|                                  |                                                                                                                                                                                                                   |                            |

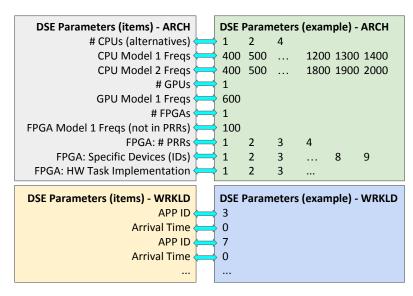

| 54 | Parameters for DSE Configuration                                                                                                                                                                                                                                                                                                                                                                           | 121        |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

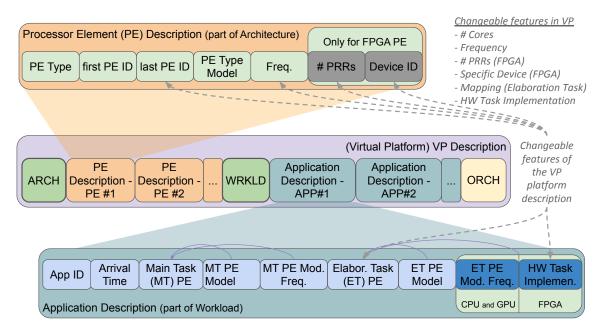

| 55 | Virtual Platform (VP) Description                                                                                                                                                                                                                                                                                                                                                                          | 122        |

| 56 | Architecture Description Details                                                                                                                                                                                                                                                                                                                                                                           | 123        |

| 57 | Workload Description Details                                                                                                                                                                                                                                                                                                                                                                               | 124        |

| 58 | Hypervolume Indicator in a Two-Objective Space (extracted from (FONSECA; PAQUETE; LOPEZ-IBANEZ, 2006))                                                                                                                                                                                                                                                                                                     | 124        |

| 59 | Representation of a Nadir Point in a Two-Objective Space (based on (WANG; HE; YAO, 2017))                                                                                                                                                                                                                                                                                                                  | 126        |

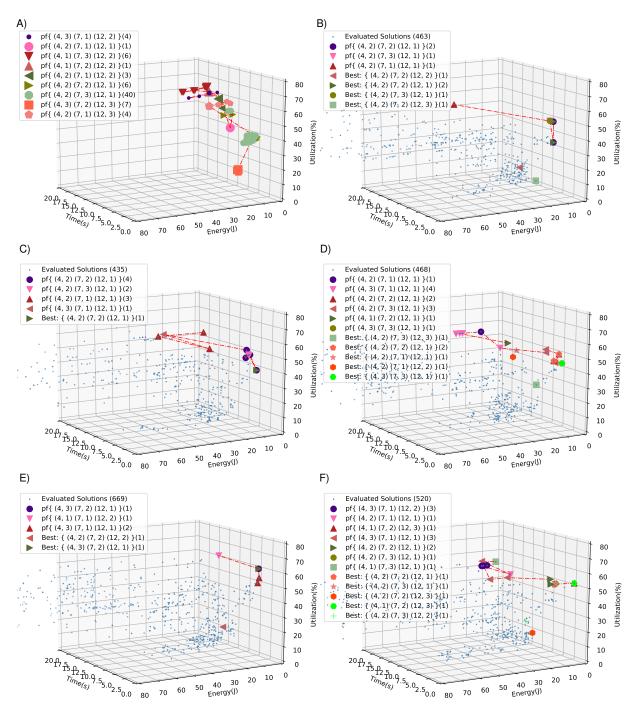

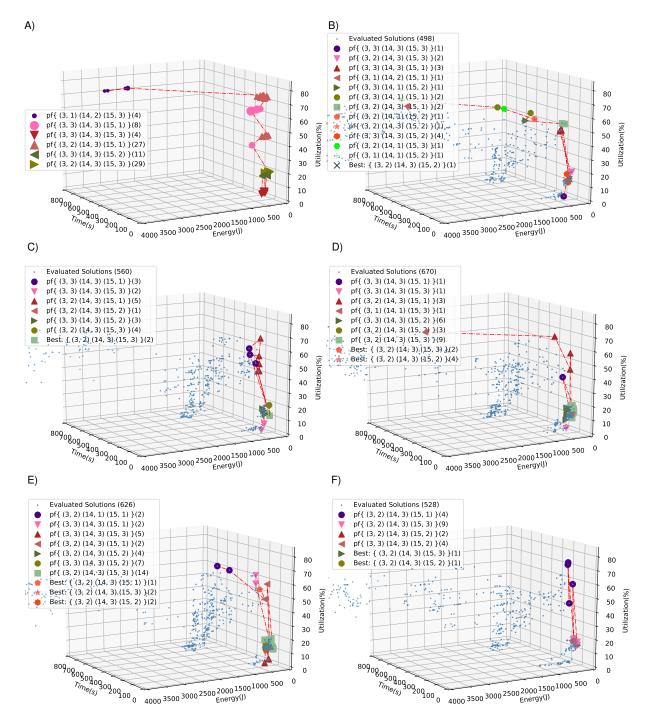

| 60 | (A) Pareto Front from Exhaustive Search and (B-F) DSE Runs 14, 12, 1, 27, and 24 ( $\approx$ the 10th, 25th, 50th, 75th and 95th percentiles of the HR values regarding the DSE PF Approximations, respectively) considering the Applications 4, 7, and 12                                                                                                                                                 | 127        |

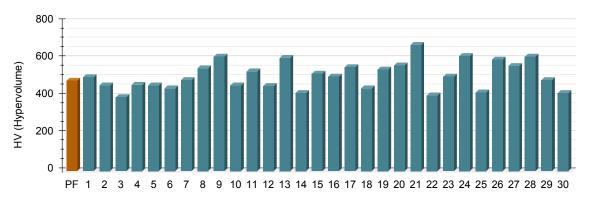

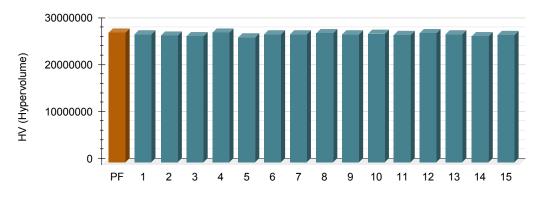

| 61 | Bar Plot of the HV (Hypervolume) Indicator for the Exhaustive Search PF and the DSE Runs #1 to #30 (Applications 4, 7, and 12)                                                                                                                                                                                                                                                                             | 128        |

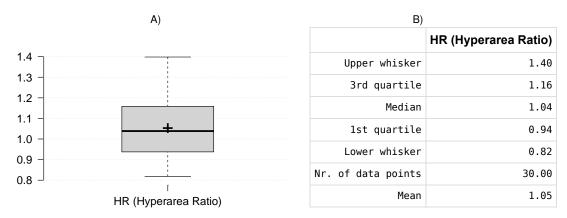

| 62 | (A) Boxplot of the HR (Hyperarea Ratio) Indicator of the DSE Runs #1 to #30 and using the Case Study #3, Scenario 1 PF as the known Design Space PF. (B) Boxplot Statistics (Applications 4, 7, and 12).                                                                                                                                                                                                   | 128        |

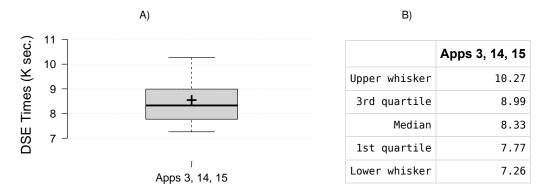

| 63 | (A) Box Plot of the Simulation Times of Case Study #4 Scenario 1 (Applications 4, 7, and 12). (B) Box Plot Statistics                                                                                                                                                                                                                                                                                      | 129        |

| 64 | (A) Exhaustive Search and (B-F) DSE Runs 14, 15, 13, 7, and 12 ( $\approx$ the 14th, 28th, 50th, 72th, and 92th percentiles of the HR values regarding the DSE PF Approximations, respectively) for Applications                                                                                                                                                                                           | 4.0.0      |

| 65 | 3, 14, and 15                                                                                                                                                                                                                                                                                                                                                                                              | 130<br>131 |

| 66 | (A) Boxplot of the HR (Hyperarea Ratio) Indicator of the DSE Runs #1 to #15 and using the Case Study #3, Scenario 2 PF as the known Design Space PF. (B) Box plot Statistics (Applications 3, 14, and 15)                                                                                                                                                                                                  | 131        |

| 67 | (A) Box Plot of the Simulation Times of Case Study #4 Scenario 1 (Applications 3, 14, and 15). (B) Box Plot Statistics                                                                                                                                                                                                                                                                                     | 132        |

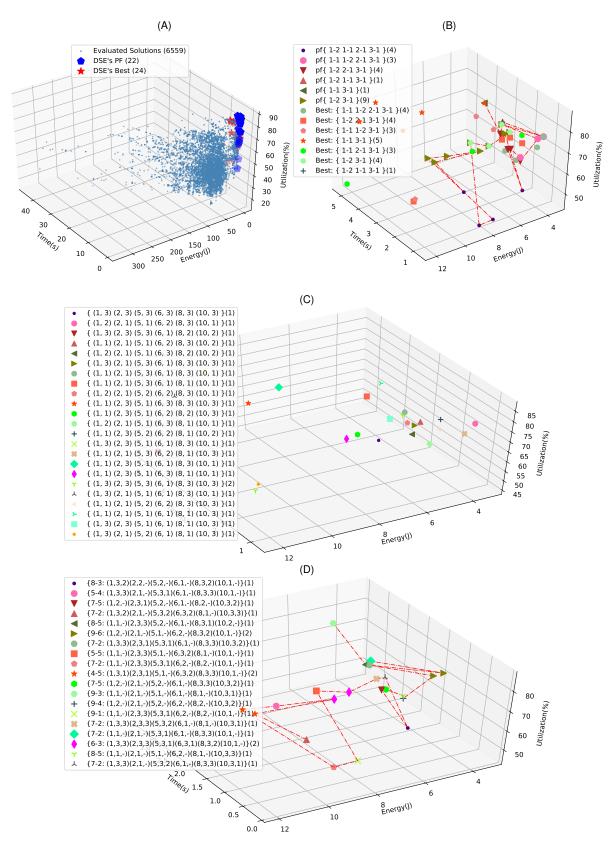

| 68 | DSE for Applications 1, 2, 5, 6, 8, and 10: (A) All Evaluated Solutions Highlighting the PF and DSE's "Best" Solutions. (B) Architecture Elements of PF and DSE's "Best" Solutions. (C) "Best" Solutions Detaching the Applications Mappings. (D) PF Solutions Indicating the Specific FPGA Device and Number of PRRs, followed by the Appl. ID (Tab. 5, its Kernel Mapping (1: CPU, 2: GPU, and 3: FPGA), |            |

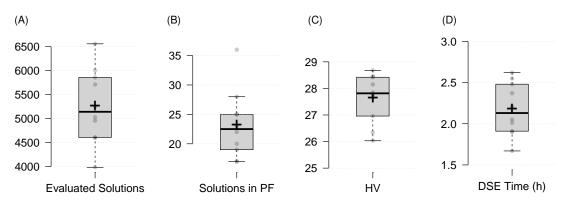

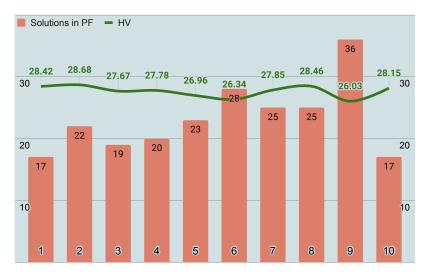

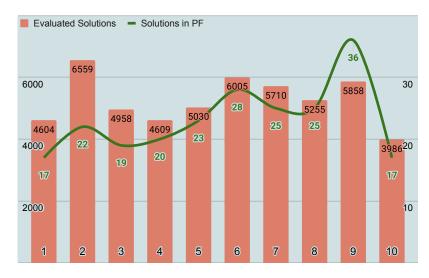

| 69 | and the used HW Task Implementation for FPGA (Tab. 7) Box Plots for (A) Evaluated Solutions, (B) Solutions in PF, (C) HV                                                                                                                                                                                                                                                                                   | 133        |

| 70 | Indicator, and (D) DSE Time for Case Study #4, Scenario 3                                                                                                                                                                                                                                                                                                                                                  | 134        |

| 70 | No Relation Between the PF's Size and the HV Indicator (Case Study #4, Scenario 3)                                                                                                                                                                                                                                                                                                                         | 134        |

| 71 | No Relation Between the Sets Cardinalities of Evaluated Solutions and Solutions in PF (Case Study #4, Scenario 3)                                                                                                                                                                                                                                                                                          | 135        |

|    |                                                                                                                                                                                                                                                                                                                                                                                                            |            |

### **LIST OF TABLES**

| 1<br>2      | Comparative Evaluation between the Related Works                                                                              | 61       |

|-------------|-------------------------------------------------------------------------------------------------------------------------------|----------|

| _           | DPR, and PRR Features                                                                                                         | 63       |

| 3           | SAVE-htlp Experiment Configurations                                                                                           | 79       |

| 4<br>5<br>6 | Summary of Case Studies #1 and #2                                                                                             | 95<br>95 |

| 7           | stream                                                                                                                        | 96       |

| 7<br>8      | HW Tasks' Implementations of the Workload's Applications HW Tasks' Latencies, Powers, and Partial Bitstreams - Original Codes | 98<br>99 |

| 9           | HW Tasks' Latencies, Powers, and Partial Bitstreams - Two Loop                                                                | 00       |

|             | Unrolling                                                                                                                     | 99       |

| 10          | HW Tasks' Latencies, Powers, and Partial Bitstreams - Two Compute Units                                                       | 100      |

| 11          | HW Tasks' Latencies, Powers, and Partial Bitstreams for Application                                                           | 100      |

|             | 2MM (3) with FPGA Optimizations                                                                                               | 100      |

| 12          | Architecture Scenarios for Case Study #1 (settings 1-10))                                                                     | 101      |

| 13          | Architecture Scenarios for Case Study #2 (settings 11-16)                                                                     | 105      |

| 14          | Summary of Case Studies #3 and #4                                                                                             | 112      |

| 15          | Architecture Types Description and Its Processing Elements                                                                    | 118      |

| 16          | DSE Parameters for Experimentation Scenario 3                                                                                 |          |

| 17          | Characterization of DSE Runs of Case Study #4, Scenario 3                                                                     | 132      |

| 18          | Briefing of the Case Studies' Questions                                                                                       | 137      |

#### LIST OF ABBREVIATIONS AND ACRONYMS

ALUT Adaptive Look-Up Tables

aoc Altera Offline Compiler

ASIC Application Specific Integrated Circuits

BIHW Board Interface Hardware

CPU Central Processing Unit

DPC Dynamic Power for the Core

DPPH Dynamic Power for the Periphery Hardware

DPR Dynamic and Partial Reconfiguration

DSE Design Space Exploration

DSP Digital Signal Processor

ES Embedded Systems

FEHetSS FPGA-Enabled Heterogeneous System Simulator

FPGA Field Programmable Gate Array

GPGPU General Purpose Graphics Processing Unit

GPU Graphics Processing Unit

HW Hardware

HTLP Heterogeneous Task-Level Parallelism

I/O Input/Output

LLVM Low-Level Virtual Machine

LUT Look-Up Tables

MPSoC Multiprocessor System-on-Chip

OS Operating System

OpenCL Open Computing Language

PF Pareto Front

PE Processing Element

PR Partial Reconfiguration

PRM Partially Reconfigurable Module

PRR Partially Reconfigurable Region

RTL Register-transfer Level

SA Simulated Annealing

SIS System-level Simulation

SoC System-on-Chip

SPD Standby Power for the Device

SPPH Standby Power for the Periphery Hardware

SW Software

TLM Transaction-Level Modeling

TLP Task-Level Parallelism

VirtualHWAccel Virtual Hardware Accelerator

VP Virtual Platform

XML eXtensible Markup Language

### **CONTENTS**

| 1.1<br>1.1.1<br>1.1.2<br>1.2<br>1.3 | Thesis' Research Challenges  Motivational Scenario Research Challenges  Work's Main Contributions  Work's Methodology Overview Thesis Structure                                                                                                                         | 18<br>21<br>22<br>22<br>22<br>24<br>26                         |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|

| <b>2.1 2.2</b> 2.2.1                | ACKGROUND TOPICS  Embedded Systems and its Design  Design Space Exploration  A DSE Heuristic: Simulated Annealing  System-level Simulation  OpenCL  FPGA Devices as Hardware Accelerators  Chapter Summary                                                              | 27<br>27<br>29<br>32<br>34<br>36<br>38<br>41                   |

| 3.1.1<br>3.1.2                      | Related Works High-Level Simulation 3.1.1.1 Works with Power Model 3.1.1.2 Works with No Power Model Low-Level Simulation 3.1.2.1 Works with Power Model 3.1.2.2 Works with No Power Model A "Bird's Eye" View of the Related Works Research Challenges Chapter Summary | 42<br>42<br>42<br>42<br>43<br>51<br>51<br>52<br>60<br>63<br>65 |

| 4.1                                 | PGA-ENABLED HETEROGENEOUS SYSTEM MODELING AND SIMU- ATION                                                                                                                                                                                                               | 67<br>70<br>74<br>75<br>81<br>82<br>83                         |

|                                     |                                                                                                                                                                                                                                                                         | 50                                                             |

| 4.3.2               | Workload Modeling                                                                                                                                                     | 85<br>86 |

|---------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 4.4                 | FEHetSS – FPGA-Enabled Heterogeneous System Simulator                                                                                                                 | 88       |

| 4.4.1               | FPGA Processing Element Simulation Flow                                                                                                                               | 90       |

| 4.5                 | Chapter Summary                                                                                                                                                       | 92       |

|                     | ASSESSING FEHETSS AS A SOLUTION EVALUATOR DURING DSE AND                                                                                                              |          |

|                     | W DESIGN ACTIVITIES                                                                                                                                                   | 94       |

| <b>5.1</b><br>5.1.1 | Case Studies Goals and Preparation                                                                                                                                    | 94<br>94 |

| 5.1.1               | · ·                                                                                                                                                                   | 94<br>95 |

| 5.1.2<br><b>5.2</b> | <del>_</del>                                                                                                                                                          | 98       |

| 5.2.1               |                                                                                                                                                                       | 101      |

| 5.3                 | Case Study #2 – Evaluating HW Design Alternatives                                                                                                                     | 105      |

| 5.3.1               |                                                                                                                                                                       | 106      |

| 5.4                 | Chapter Summary                                                                                                                                                       | 109      |

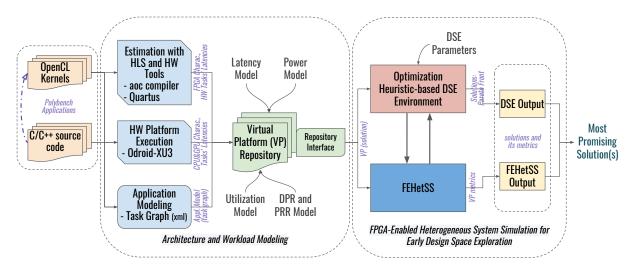

| 6 E                 | EVALUATING FEHETSS IN A HEURISTIC-BASED DSE ENVIRONMENT .                                                                                                             | 111      |

| 6.1                 | Goals for Case Studies #3 and #4                                                                                                                                      | 111      |

| 6.2                 | Case Study #3 – Using FEHetSS in Exhaustive Search                                                                                                                    | 111      |

| 6.2.1               |                                                                                                                                                                       |          |

| 6.3                 | Case Study #4 - Evaluating FEHetSS in an Heuristic-based DSE                                                                                                          |          |

| 6.3.1               | <b>5</b>                                                                                                                                                              |          |

| 6.3.2               | I I                                                                                                                                                                   | 121      |

| 6.3.3               | ,                                                                                                                                                                     |          |

| 6.4                 | Chapter Summary                                                                                                                                                       | 135      |

| 7 <i>A</i><br>7.1   | ASSESSING THE RESEARCH CHALLENGES Evaluating Challenge 01: How to enable early-DSE on heterogeneous systems that include reconfigurable hardware acceleration through | 136      |

|                     | FPGAs?                                                                                                                                                                | 136      |

| 7.2                 | Evaluating Challenge 02: How to assess (at early stages) different architectural FPGA implementations for a specific application kernel,                              |          |

|                     | as an HW task, within a heterogeneous system?                                                                                                                         | 138      |

| 7.3                 | Evaluating Challenge 03: How to model FPGA units at a high level,                                                                                                     |          |

|                     | supporting PRR and DPR, focusing on high-level system simulation?                                                                                                     | 138      |

| 7.4                 | Chapter's Considerations                                                                                                                                              | 139      |

| 8 0                 | CONCLUSIONS                                                                                                                                                           | 141      |

| 8.1                 | Answering the Research Challenges: Thesis' Contributions                                                                                                              | 143      |

| 8.2                 | Future Perspectives for the Thesis                                                                                                                                    | 145      |

| DEE                 | EDENICES                                                                                                                                                              | 1/19     |

#### 1 INTRODUCTION

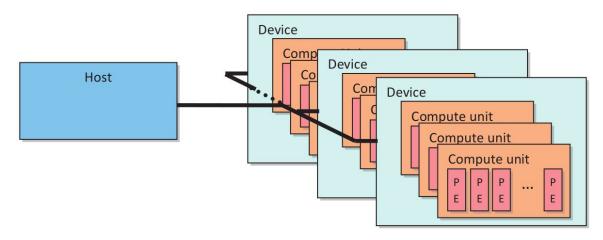

Today's computing environments explore the capabilities of a wide range of processors – such as CPUs (Central Processing Units), DSPs (Digital Signal Processors), media processors, vector processors, reconfigurable hardware (such as FPGAs - Field Programmable Gate Arrays), and General Purpose Graphics Processing Units (GPGPUs, or just GPUs) (KAELI et al., 2015; WAIDYASOORIYA; HARIYAMA; UCHIYAMA, 2018). These systems integrate a relevant number of independent and heterogeneous processing resources within the same environment (MIELE et al., 2015).

The workloads submitted to the systems usually present a series of different behaviors. It comprises applications with a mix of computational demands such as control-intensive (e.g., searching, sorting, and parsing), data-intensive (e.g., image processing, simulation and modeling, and data mining), and compute-intensive tasks (e.g., iterative methods, numerical methods, and financial modeling) (KAELI et al., 2015). Thus, different workloads characterize the computing scenarios – consisting of a range of applications with distinct performance requirements and varying amounts of data to process (BOLCHINI et al., 2015), demanding diverse processing capabilities. In these scenarios, the overall throughput is subject to the hardware (HW) devices' computational efficiency. Moreover, there is no single architecture suitable for all types of applications (KAELI et al., 2015).

Some applications, especially those that contain substantial fractions of sequential code, run faster on the CPU. Others have extensive use of data parallelism finishing their tasks earlier by running on Graphical Processing Units (GPUs) (SINGH et al., 2017). Besides, several parts (excerpts) of the applications can be executed in parallel – the so-called *kernels* of the applications. It allows the exploitation of task-level parallelism (TLP) (SCARPAZZA et al., 2006). The multi-processed systems, including those with a series of heterogeneous processing elements (PEs), exploit TLP.

Typically, heterogeneous systems better meet the workload's demands. Computing with heterogeneous resources such as FPGAs and GPUs can improve system performance and energy efficiency (DURELLI et al., 2014; WAIDYASOORIYA; HARIYAMA; UCHIYAMA, 2018). Providing a high computing capacity and energy efficiency, usually

enabled by abundant parallelism of data (ROGERS, 2013), processing elements (PEs) such as GPUs and FPGAs arise in the heterogeneous context with a very motivational perspective. Thus, a promising approach to deal with current computing scenarios is to exploit specialized computing resources integrated into heterogeneous system architectures, such as asymmetric multi-core CPUs, specialized graphics coprocessors, GPUs, and reconfigurable hardware like FPGAs (BOLCHINI et al., 2015). Multiprocessor System-on-Chip (MPSoC) is an instance of heterogeneous systems providing large amounts of computing capability (hsafoundation, 2020). These systems commonly contain CPUs (Central Processing Units) cores of different characteristics, GPGPUs (General Purpose Graphics Processing Units) or GPUs (Graphics Processing Units) processors, and perhaps other PEs – e.g., FPGAs (Field Programmable Gate Arrays) devices, ASIC (Application Specific Integrated Circuit) HW accelerators, and DSPs – Digital Signal Processors.

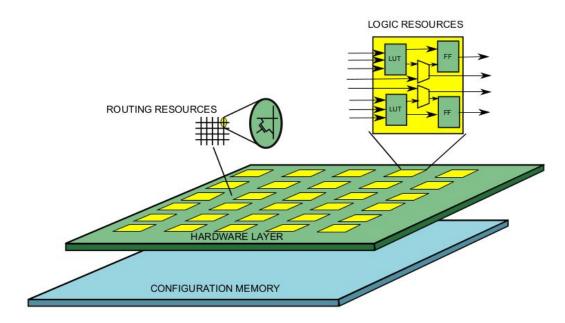

FPGA devices can provide enhanced performance combined with superior power efficiency (MUSLIM et al., 2017), whereas keeping flexibility (not possible to ASIC accelerators). These aspects plausibly have led to the deployment of FPGAs in cloud computing architectures like F1 Instances of Amazon (AWS) (AMAZON, 2020), and Project Catapult of Microsoft Research (MICROSOFT, 2020). Nonetheless, programming FPGAs usually requires a low-level HW description language (e.g., Verilog or VHDL) (SHATA; ELTEIR; EL-ZOGHABI, 2019). The design initiatives using this abstraction level demands longer development time. However, current High-level Synthesis (HLS) tools have enabled the programming of these devices. It allows the use of a high-level abstraction language in FPGA development. Indeed, FPGA vendors currently release mature environments (INTEL, 2020a) (XILINX, 2020) that allow HW description and synthesis in higher-level languages, such as OpenCL, C, and C++.

The design of a new HW/SW (hardware/software) system, such as an embedded system, is a complex initiative. The exploring of alternative solutions to such systems frequently occurs at a system-level abstraction (GRIES, 2004). System-level Simulation (SIS) uses coarser models for architecture and applications (GRIES, 2004), allowing reduced time of simulation and possibly a broader evaluation of the design alternatives. The referred models require non-functional requirements that may include latency, power estimates, HW area, and possibly others. Also, it depends on the system workload and the target platform. We can obtain estimations data using platform execution, cycle-accurate simulation, tool estimation, or even extracting from component datasheets and academic works. Moreover, the employed modeling paradigm must include a framework containing concepts and respective representations, providing the fundamental elements to describe the platform in its parts, such as architecture and workload.

Design Space Exploration (DSE) is the process of finding a set of optimal (or near-

optimal) configurations (the *Pareto* front) regarding some evaluation metrics and following design restrictions (SINAEI; FATEMI, 2018). DSE must evaluate the solutions based on multiple optimization objectives – such as execution time, energy consumption, utilization, cost, and others. Frequently, the objectives conflict and there is no single solution that optimizes all (PIMENTEL, 2017). Resuming, we can state that the DSE goal is to find the *Pareto* front (or the most proximal settings) of the design space (PIMENTEL, 2017). Several works use heuristics to accelerate the DSE process such as Simulate Annealing (SA) (SINAEI; FATEMI, 2018), Genetic Algorithms (GA) (JIANG; ELES; PENG, 2016), and Ant Colony Optimization (ACO) (WANG et al., 2007). These heuristics provide a search mechanism that systematically traverses the design space aiming to find quality solutions.

Cycle and instruction accurate simulators frequently cannot deal with the demand under DSE, given its long simulation time, architecture details (e.g., aspects of memory, cache configurations, communication channels, etc.), low-level programming/parameterization, and so on. Initial design phases do not allow the time to define all these system details. Many works present simulators and frameworks aiming at the evaluation of architecture settings.

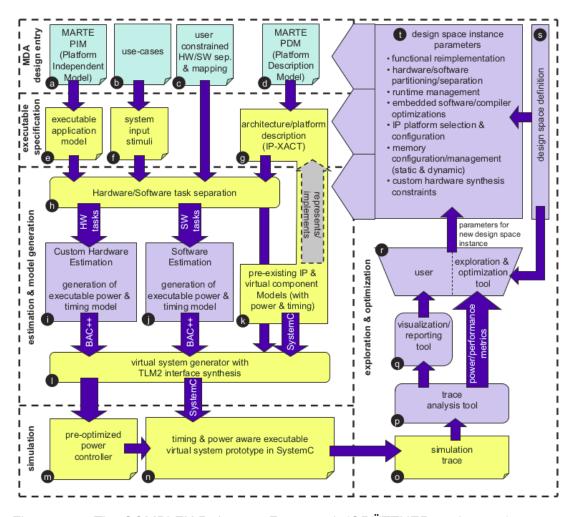

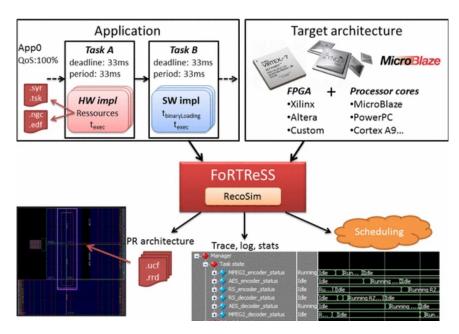

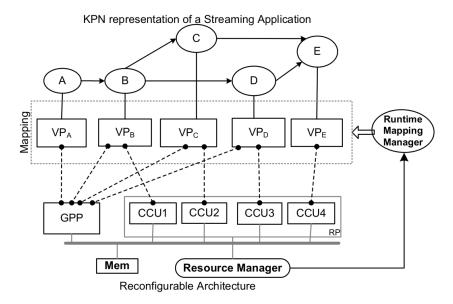

Some works employ low-level simulation, usually at register-transfer level (RTL), to evaluate the architecture settings – such as FENG et al. (2017), LIANG et al. (2017), SHAO et al. (2016), MAKNI et al. (2018), ZHONG et al. (2016), ZHAO et al. (2020), HUANG et al. (2019), LIGNATI et al. (2021), QUADRI et al. (2010), GONG; DIES-SEL (2014), and BRITO et al. (2007a,b)). Therefore, they likely demand long simulation times and more detailed system models/artifacts, caused by the simulated details. In contrast, works like MIELE et al. (2015), SIGDEL et al. (2009a,b), DUHEM et al. (2015), NOGUEIRA et al. (2016), AN; GAMATIÉ; RUTTEN (2015), and BLOUIN et al. (2011) employ high-level simulation also using models of high-abstraction level. Such approaches usually require less efforts in the models' description and the simulation itself. Others works utilize standard languages as UML (Unified Modeling Language) (HUANG; HSIUNG; SHEN, 2010) and their extension UML/MARTE (Modeling and Analysis of Real-Time and Embedded systems) (GRÜTTNER et al., 2013; HER-RERA et al., 2014) (QUADRI et al., 2010) to model the platform using a series of model transformations to generate simulation models, but most employing low-level abstractions.

Several works do not account for the system power/energy. But, those works that do it usually employ some kind of component characterization (MIELE et al., 2015; SHAO et al., 2016; NOGUEIRA et al., 2016; AN; GAMATIÉ; RUTTEN, 2015; GRÜTTNER et al., 2013; MAKNI et al., 2018; LIGNATI et al., 2021) or even direct interaction with HW (HUANG; HSIUNG; SHEN, 2010) to generate power/energy-related metrics.

FPGAs are configurable components. It can provide higher flexibility degree when

Dynamic and Partial Reconfiguration (DPR) and Partially Reconfigurable Regions (PRRs) are in use. DPR allows the configuration of a device's portion while still operating in other regions. PRRs are portions of the device that can pass by a DPR. Although the previous works deal with FPGA fabric, DPR and PRR features are not always present. SIGDEL et al. (2009a) and DUHEM et al. (2015) deal with both features but lack in power estimation. AN; GAMATIÉ; RUTTEN (2015), BLOUIN et al. (2011), LIANG et al. (2017), FENG et al. (2017), and QUADRI et al. (2010) consider DPR feature, but with gaps in the use of PRRs or even the accounting of reconfiguration time/energy. GONG; DIESSEL (2014) and BRITO et al. (2007a,b) only focus on DPR issues, not providing a wide system-level view. The goal in works like MAKNI et al. (2018), ZHONG et al. (2016), and (ZHAO et al., 2020) is the FPGA's Performance, Power, and Area estimations, while in LIGNATI et al. (2021) the focus is on resource provisioning in CPU-FPGA-based Cloud Systems.

Thus, these works lack some essential aspects during the evaluation of Heterogeneous System Architectures (HSA) in early design phases, as follows: the necessity of low-level designing (e.g., to describe a task using HDL – hardware description languages, or describing floorplanning aspects), time-consuming evaluation due to detailed simulations, absence of power modeling, the impossibility of deal with multiple Partially Reconfigurable Regions (PRRs) or to model Dynamic and Partial Reconfiguration (DPR), and even the non-compliance with HW (e.g., FPGA) accelerated systems.

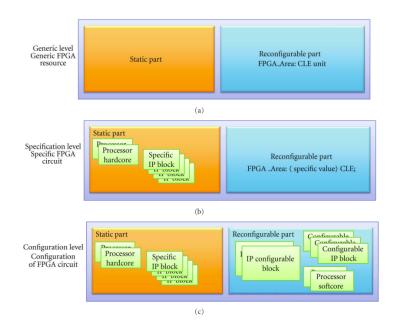

FPGA-enabled system simulation appears to be a promising feature due to the possibility of using Dynamic and Partial Reconfiguration (DPR), or even the ability to define one or more Partially Reconfigurable Regions (PRRs). Thus, a flow and a simulator proficient in modeling an FPGA-capable system using a high abstraction level and simulating its behavior in terms of latency, power consumption, and HW utilization are of paramount importance. Regarding the embedded systems domain, the employment of large FPGA devices is usually not an option, hence, hampering the acceleration of whole applications. Thus, wondering about a modeling methodology, the OpenCL (KHRONOS, 2020) models and concepts appear to be suitable in this context where a designer shall models an FPGA unit accelerating (only) the application's kernels as HW tasks, maintaining the remaining running in a general-purpose processor.

#### 1.1 Thesis' Research Challenges

We present the Research Challenges of the Thesis in this section, passing before by a Motivational Scenario that contextualizes the work.

#### 1.1.1 Motivational Scenario

Consider a design initiative for a new embedded system. It must deal with a specific workload and considers metrics such as execution time, power/energy consumption, and processing elements/HW area utilization. Since probably no physical architecture is available, early design evaluations must happen using high-level models. Thus, System-Level Simulation is a way to assess the design points employing Virtual Platforms (VP) modeling the system architecture, the workload, and their mappings. With notions such as host/device processors and application kernels, OpenCL concepts serve as a basis for modeling the system architecture&workload. Also, considering High-Level Synthesis tools, it outcomes appropriate artifacts that enable modeling the application's kernel(s) running in FPGA units. FPGAs are customizable devices usually providing performance and power efficiency. Besides, it offers features like Partially Reconfigurable Regions (PRRs) and Dynamic and Partial Reconfiguration (DPR). Each PRR can potentially act as an independent HW accelerator. DPR enables dynamically change the PRR's configuration. Moreover, the custom capability of FPGA devices allows experimenting with diverse HW task implementations aiming to obtain a good trade-off between execution time, energy consumption, and resource utilization. Given this scenario, how could a designer conduct early design space exploration (early-DSE) activities in a feasible time considering high-abstraction descriptions of the system and its applications, producing valuable design artifacts for initial decisions making? All of this, before passing to more detailed and low-level HW/SW development.

#### 1.1.2 Research Challenges

We define the Thesis Research Challenges through the following items:

- Challenge 01 (C01): How to enable early-DSE on heterogeneous systems that include reconfigurable hardware acceleration through FPGAs?

- Challenge 02 (C02): How to assess (at early stages) different architectural FPGA implementations for a specific application kernel, as an HW task, within a heterogeneous system?

- Challenge 03 (C03): How to model FPGA units at a high level, supporting PRRs and DPR, focusing on high-level system simulation?

#### 1.2 Work's Main Contributions

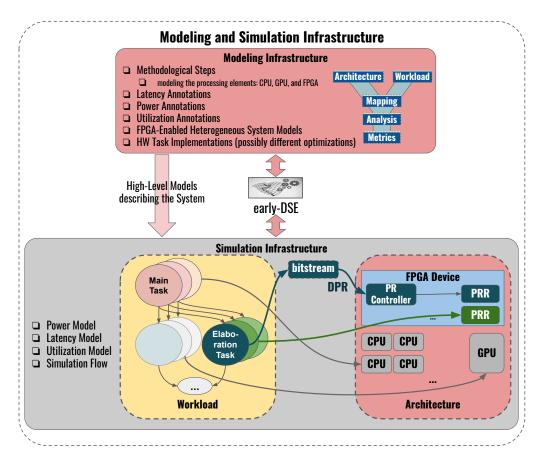

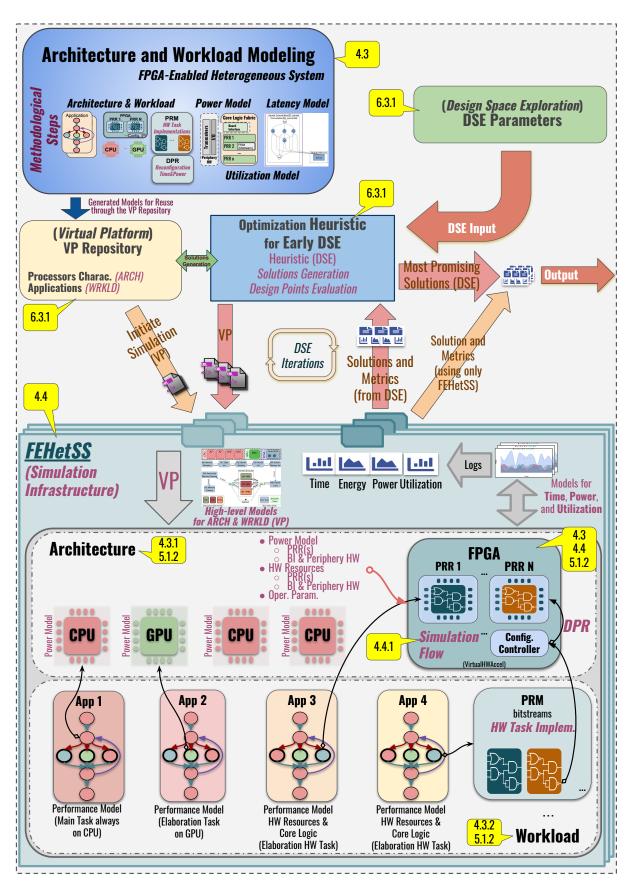

In this work, we describe a methodology to construct models for *Architecture* and *Workload* that can be employed in System-Level Simulation through FEHetSS (FPGA-Enabled Heterogeneous System Simulator) simulator. In its simulations, FEHetSS

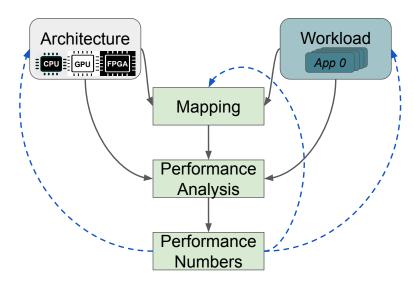

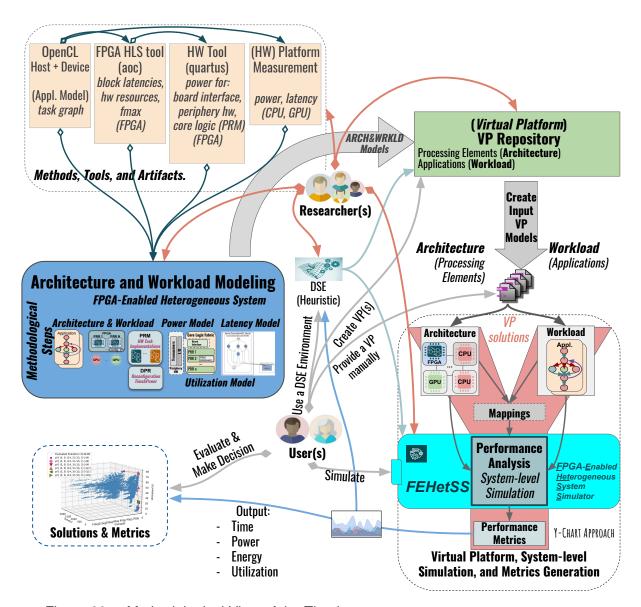

Figure 1 - Thesis Contributions Context

may include, beyond CPUs and GPUs, virtual hardware accelerators (*VirtualHWAccels*) modeled as FPGA devices. Our methodology includes the high-level modeling of FPGA units featuring PRRs and DPR, also supported by FEHetSS. As part of case studies, we describe the main capabilities of FEHetSS. Towards this end, our work makes some contributions which are illustrated in Fig. 1, as a context diagram, and listed in the following items:

- A Modeling and Simulation Infrastructure to support early-DSE of FPGA-capable Heterogeneous Systems;

- A set of methodological steps aiming the high-level modeling of the system Architecture and the Workload applications;

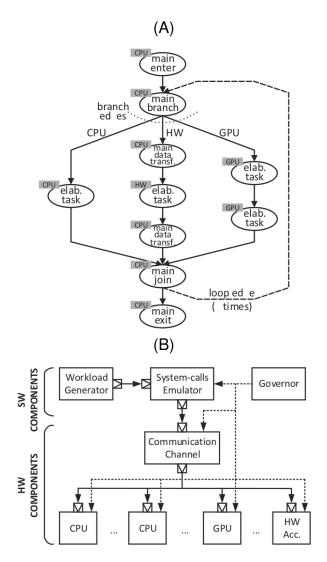

- The task-level modeling of an application considering sequential management tasks (called main tasks) and heterogeneously accelerated potentially paralleled tasks (named elaboration tasks);

- The high-level modeling of FPGA units supporting Dynamic and Partial Reconfiguration (DPR) and the device partition in Partially Reconfigurable Regions (PRRs);

- The FEHetSS simulator and its simulation model for FPGA-Enabled Systems, considering aspects such as latency, power, and resource utilization;

- A set of Case Studies demonstrating the modeling and simulation capabilities of the proposed infrastructure (FEHetSS and models' creation methodology), as follows:

- (i) DSE of heterogeneous settings using FEHetSS as a single design point assessing tool;

- (ii) Evaluation of HW Design Implementations of an application's kernel, supported by the modeling steps and our simulator;

- (iii) Exhaustive Search of solutions in a customized design space employing the rapid simulations of FEHetSS;

- (iv) Embedding of FEHetSS in a Heuristic-based DSE Environment performing explorations in a parametrized design space.

In summary, the main goal of this work is to provide a modeling and simulation infrastructure to perform early Design Space Exploration (DSE) for heterogeneous systems featuring FPGA fabric for reconfigurable hardware acceleration. Moreover, the framework also enables the design's implementation assessment by considering the hardware/software interface in a heterogeneous architecture.

#### 1.3 Work's Methodology Overview

For the development of the Thesis, we employ a set of tools, processes, and artifacts aiming to attend the presented Research Challenges. Since our main goal is to explore design spaces of FPGA-enabled heterogeneous systems by simulation in the early phases of development, we base our modeling steps on concepts that are commonly employed in programming languages like OpenCL (KHRONOS, 2020) - e.g., applications with portions of *host code* to manage and prepare the execution of the *kernel code* which is possibly *accelerated* in *devices* like CPU, GPU, or FPGAs. To make it possible to annotate our models, especially those related to FPGA devices, we employ High-Level Synthesis (HLS) (INTEL, 2020a) tools to make estimations for the models, providing details such as latency, power, and HW utilization. Besides, regarding CPU and GPU architectural elements, we use a real platform (HARDKERNEL, 2020) to extract measurements for the characterization of the processors' power and the applications' tasks latencies.

We employ the Y-Chart approach (GRIES, 2004) to model our platforms, using models to separately describe the architectural elements – such as the Processing Elements (PEs) – and the workload – a set of applications. Our modeling elements

include the characterization of CPU, GPU, and FPGA, describing them through power models containing the operation power, idle power, and frequency. For the description of FPGA devices in the models, extra annotations depict aspects such as: (i) the necessary HW resources to implement a custom processor within the device, (ii) the annotations to describe the employment of Dynamic and Partial Reconfiguration (DPR), (iii) the device partition in Partially Reconfigurable Regions (PRR), (iv) the size of the called bitstream files used to (re)configure the whole device or its PRRs, and others.

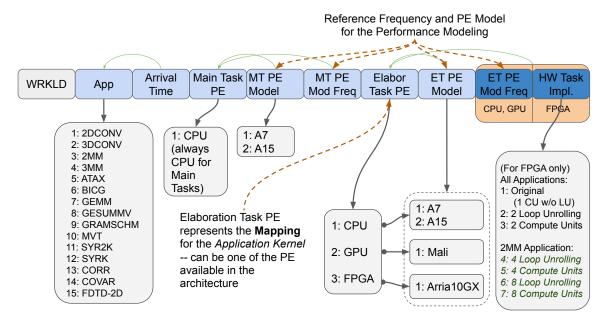

To model the applications, we employ task graphs where each task represents an application's portion at a coarse-grained level – e.g., a whole procedure. A performance model describes each task pointing out a PE type and model, as well as the operating frequency and respective latency. Specialized tasks, called elaboration tasks, model the application kernels allowing the mapping on distinct PEs (e.g., CPU, GPU, and FPGA).

On top of our previously developed SAVE-htlp (BETEMPS et al., 2018) framework, we develop the FEHetSS simulator using SystemC at Transaction Level Modeling (TLM) abstraction level. Aiming to promote an agile utilization of FEHetSS, we prepare a repository containing Architecture and Workload model portions capable to be reused in the generation of different solutions to be simulated with FEHetSS. A set of automation scrips accompany our model repository allowing us to automate the interaction with FEHetSS.

As a proof of concept regarding the modeling methodology and aiming to experiment simulations with FEHetSS, we prepare a set of Case Studies with FEHetSS also employing the generation of solutions from our model repository. Using the GQM (Goal-Question-Metric) approach (BASILI; CALDIERA; ROMBACH, 1994), we define the Goal(s) of each Case Study by setting up Question(s) to be answered and the Metric(s) to be extracted during the case studies. The answers to the Case Studies Questions give us support for the fulfillment assessment of the Thesis Research Challenges.

The repository automation facilitates the performing of the Case Studies, especially in the handle of a design space exhaustive traversing using FEHetSS, as well as an integration of FEHetSS in a heuristic-based DSE environment. We employ Simulated Annealing (SA) (FRANZIN; STÜTZLE, 2019) as the DSE environment's heuristic. SA is a simple to formulate, robust, and compact strategy for single or multiple objective optimization problems. It is a widely used heuristic commonly providing good solutions even for mixed problems of discrete and continuous spaces (SUMAN; KUMAR, 2006; FRANZIN; STÜTZLE, 2019).

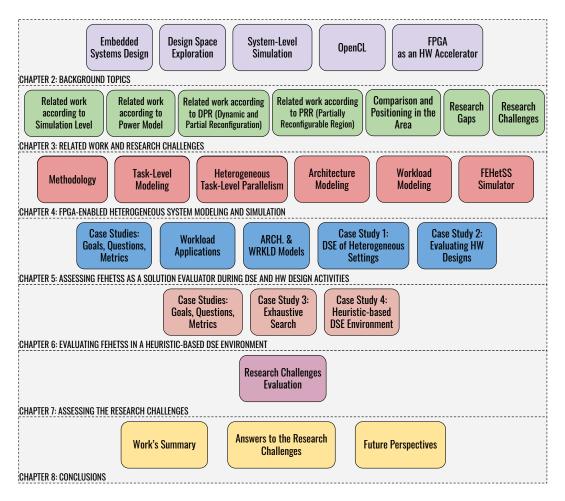

Figure 2 - Thesis' Structure and Chapters' Main Topics

#### 1.4 Thesis Structure

The Thesis is structured as follows. Chapter 2 presents background topics of the work. Next, in Chapter 3, we describe the related works and present the Thesis' Research Challenges. Chapter 4 presents the work's main contributions passing by sections approaching the Thesis' methodological view, the modeling of heterogeneous task-level parallelism, the methodology to model Virtual Platforms, and the FEHetSS simulator. Chapter 5 describes the experimentation of FEHetSS by manual DSE in Case Studies #1 and #2, also presenting its results. After, Chapter 6 presents the Case Studies #3 and #4 that automatically employ FEHetSS through an exhaustive search and within a heuristic-based DSE environment, respectively. In Chapter 7, we present an assessment of the Thesis' Research Challenges based on the Case Studies results and respective answered questions. Chapter 8 concludes the work by presenting answers for the Research Challenges, also indicating some future perspectives for the Thesis. Fig. 2 highlights the main topics approached in each chapter.

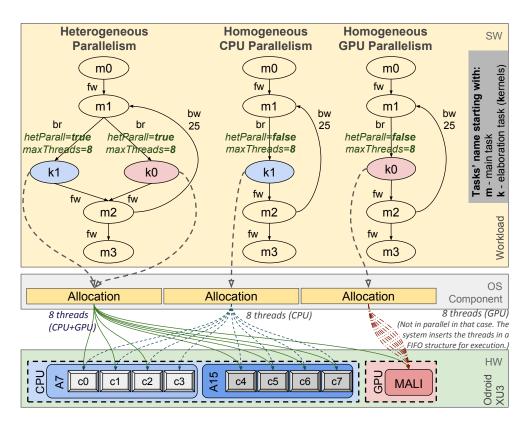

#### 2 BACKGROUND TOPICS

This chapter presents some background aspects related to the thesis. Embedded Systems (ES) are composed of SW and HW components, possibly including heterogeneous Processing Elements (PEs). The design of this type of system (Sec. 2.1) involves the analysis of the feasible design points (solutions). Usually, the design space of these systems is vast, with multiple objective functions to optimize. The Design Space Exploration (DSE) (Sec. 2.2) is the process of evaluating the design points and defining which one is the best trade-off. During the DSE, heuristics (Sec. 2.2.1) can prune the design space and still provide quality solutions. Besides, System-level Simulation (Sec. 2.3) can rapidly assess the design points based on high-level models describing Virtual Platforms (VPs) that include models for the architecture, the workload, and the mappings between both. The OpenCL standard (Sec. 2.4) provides a programming model suitable to employ in the modeling of workload's applications - describing tasks that manage the execution (main tasks) and the ones that represent the application's kernel (elaboration tasks). Elaboration tasks can run in different PEs, allowing exploring the system's heterogeneity. Besides, modern OpenCL programming environments allow employing application kernels as HW tasks using the FPGA devices flexibility (Sec. 2.5), making it act like an HW Accelerator. Also, Dynamic and Partial Reconfiguration (DPR) enhances such flexibility even more. DPR allows configuring multiple regions (called Partially Reconfigurable Regions - PRRs) separately and dynamically. Indeed, each PRR can implement an HW task separately, making a single FPGA device acting as several HW accelerators.

### 2.1 Embedded Systems and its Design

Embedded Systems (ES) provide specific and dedicated functions inside a host (CAMPOSANO; WILBERG, 1996), being a component of a greater system controlling and monitoring it (GUESSI et al., 2012). ES are information processing systems enclosed in a larger product, usually not visible to its users (MARWEDEL, 2006).

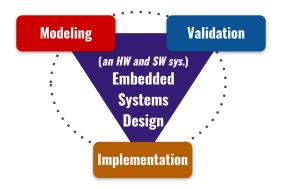

ES are highly diverse, varying from little systems – such as refrigerator controllers,

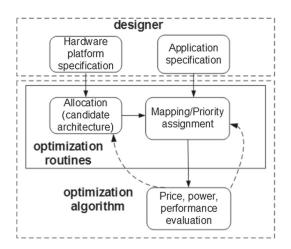

Figure 3 – Embedded Systems Design.

ATMs, or intelligent sensors in construction automation – to complex and distributed systems – e.g. automotive control and aerospace systems (VOELTER et al., 2013). Embedded software is constantly growing in terms of functionality, size, and complexity (HENDRIKS et al., 2016). Thus, ES design is in a competitive context that rapidly evolves as new technologies are introduced (BERTELS, 2012). The transformation of a design initiative in a successful product depends on the time-to-market as new functionalities are proportioned obeying performance restrictions and accessible prices (HERRERA et al., 2014; MISCHKALLA; HE; MUELLER, 2010).

According to Fig. 3, as systems containing HW and SW components, the design of Embedded Systems involves modeling, validation, and implementation (DE MICHELI; GUPTA, 1997). **Modeling** deals with the conceptualization and refinement of the specification, producing models of HW and SW. **Validation** aims to reach a reasonable level of reliability that the system will run as designed. **Implementation** is the system's physical realization in terms of hardware and software. This thesis involves aspects of modeling and validation regarding ES development.

Due to the complexity of the design of new products, the competitiveness in the ES market, and the gap in the joint design of hardware and software, more and more tasks of exploring solutions are carried out at the system level (GRIES, 2004; GAJSKI et al., 2009; SINAEI; FATEMI, 2018), to enable decision making in the early stages of development. In this context, models with a high level of abstraction are used to describe the different architecture configurations and workloads to be submitted to the system. As evaluations need to occur in the early stages of development, when usually there is no availability of architecture and applications that can be executed, the use of system-level simulation appears as an alternative for evaluating solutions during Design Space Exploration (DSE).

#### 2.2 Design Space Exploration

Design Space Exploration (DSE) is the process to find a set of optimal (or near-optimal) configurations (the *Pareto* front) regarding some evaluation metrics and following design restrictions (SINAEI; FATEMI, 2018)(PANERATI; SCIUTO; BELTRAME, 2017). It is the process of analyzing the set of possible solutions and defining which one will be selected (MARWEDEL, 2006). The solutions in the *Pareto* front are the optimal points that are not dominated by any other in the design space (PANERATI; SCIUTO; BELTRAME, 2017). A set of metrics (or objective functions) express the quality of a solution. Thus, DSE evaluates the solutions based on multiple optimization objectives – such as execution time, energy consumption, utilization, cost, and others. It characterizes an optimization problem (PALERMO; SILVANO; ZACCARIA, 2009) whose aim is maximization or minimization. Frequently the objectives conflict, and there is no single solution that optimizes all (PIMENTEL, 2017) – potentially exist several optimal solutions.

In a Multiobjective Optimization Problem (MOP), there is a solution space X in which solutions have m decision variables (or independent variables). Moreover, the DSE searches for a solution or solutions that minimizes (or maximizes) the n objective values (or dependent variables), in the objective space Y, by evaluating objective functions  $f_i$  with  $1 \le i \le n$ . Thus, during a DSE we search for MOP solutions characterized by (PIMENTEL, 2017):

Minimize

$$y = f(x) = (f_1(x), f_2(x), ..., f_n(x))$$

where  $x = (x_1, x_2, ..., x_m) \in X$

$y = (y_1, y_2, ..., y_n) \in Y$

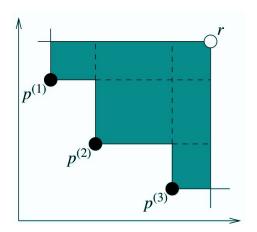

Aiming to evaluate the solutions during the DSE, the Pareto dominance relation is usually used. A solution  $x_1 \in X$  is said to dominate solution  $x_2 \in X$  if and only if  $x_1 < x_2$  (PIMENTEL, 2017).

$$x_1 < x_2 \Leftrightarrow \forall i \in \{1, 2, \dots, n\} : f_i(x_1) \le f_i(x_2) \land \exists i \in \{1, 2, \dots, n\} : f_i(x_1) < f_i(x_2)$$

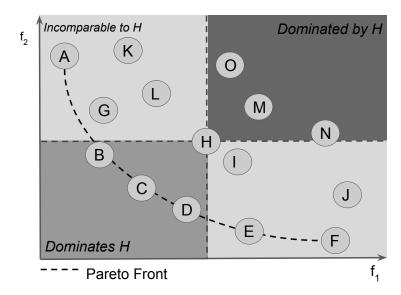

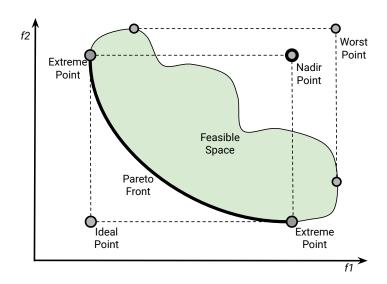

Figure 4 illustrates the Pareto front and dominance relation concepts regarding a two objective ( $f_1$  and  $f_2$ ) problem. Solutions A to F are in the Pareto front, being not comparable with each other. These solutions cannot be ordered since each one is better than the others in at least one objective function but worst in the other one(s). Solutions B to D dominates H, which dominates solutions M to O. Solutions in the light

Figure 4 – Pareto Front and Domination relation considering the objective functions f1 and f2, excerpted from (PIMENTEL, 2017).

grey areas are incomparable to H.

The performance of a system is dependent on a diverse set of factors, such as the application architecture, platform HW architecture, which processing elements (e.g. CPU, GPU, FPGA, ASIC, and DSP) are employed for each application task, beyond parameters such as caches and memory sizes. Thus, DSE is a key activity to evaluate the system under development since early design phases (HERRERA et al., 2014; SINAEI; FATEMI, 2018). The DSE adjusts the system parameters aiming at the optimal setting. In a general way, a DSE approach consists of four components (ASCIA et al., 2011): *i*) an entry point represented by the initial configurations, (*ii*) an evaluation model for the settings, (*iii*) an exploration strategy aiming to visit the design space via transformation in the configurations, and (*iv*) a stopping criterion.

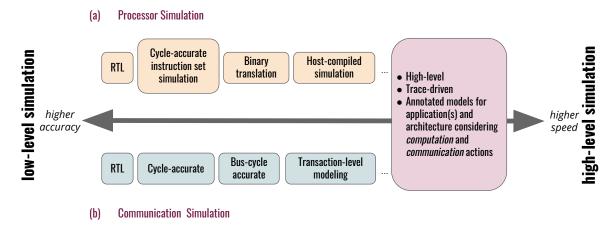

According to Fig. 5, DSE usually follows the Y-chart approach (GRIES, 2004). Y-chart separates the architecture and workload specifications, considers the mapping between both, and succeeds in a performance analysis generating performance numbers that can guide changes in the specifications or the mappings. An application model(s) represents the system *workload* – derived from the target application(s) – describing the functional behaviour independently from the architecture. Also, an *architecture* model defines the system resources in the architecture (the processing elements – PEs) and captures its performance constraints (JIA et al., 2013). The *mapping* model links the previous ones allocating tasks in the architecture PEs (GRIES, 2004) for execution (e.g. through simulation). The execution generates metrics for quantitative assessment (JIA et al., 2013). Based on execution metrics, e.g., performance, power, energy, and utilization – obtained by real hardware execution, simulation, or estimates – an analysis is performed allowing to tuning the models for the architecture,

Figure 5 - Y-Chart Approach (based on GRIES (2004))

workload, or mapping.

Obtaining the optimal *Pareto curve* requires the exhaustive search of it within the design space (PIMENTEL, 2017) of a given system. However, the vast size of the design space is a problem in most embedded system designs, and it can become even more severe according to the non-functional design requirements (restrictions) (GLAß et al., 2017; SINAEI; FATEMI, 2018). Thus, the main objective of the DSE can be relaxed in the sense of seeking to minimize the exploration time while guaranteeing good quality solutions (ASCIA et al., 2011) (not necessarily optimal). In general, DSE approaches use strategies to prune the design space and minimize the number of configurations to evaluate (ASCIA et al., 2011; SINAEI; FATEMI, 2018). In this context, we can apply Heuristics (and Meta-Heuristics). Meta-heuristics are general, higher-level methodologies that can guide strategies in the development of heuristics to solve specific optimization problems (TALBI, 2009).

Therefore, the DSE process consists of two interdependent components that need to be accelerated or improved, aiming to deal with the vast design space and to find optimal (or close to it) solutions (GRIES, 2004; SINAEI; FATEMI, 2018):

- (*i*) the evaluation of each design point (configuration) of the solution space using, for example, analytical models or simulation; and

- (ii) the search engine that systematically traverses the design space to find quality solutions.

Considering the component (i), the use of system-level simulation has interesting characteristics concerning aspects such as simulation time and the use of high-level abstraction models (made with less effort in the early stages of development). As for the component (ii), the use of heuristics for selecting and directing searches for

candidate solutions can prune the design space (usually vast in the case of ES) to be visited (examined).

#### 2.2.1 A DSE Heuristic: Simulated Annealing

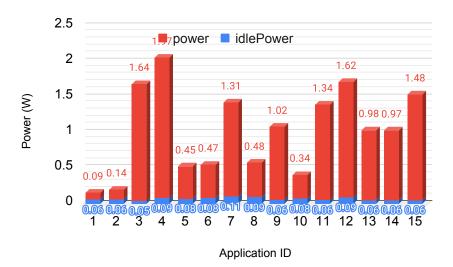

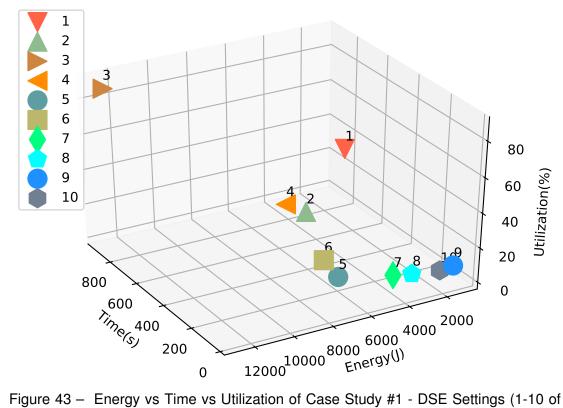

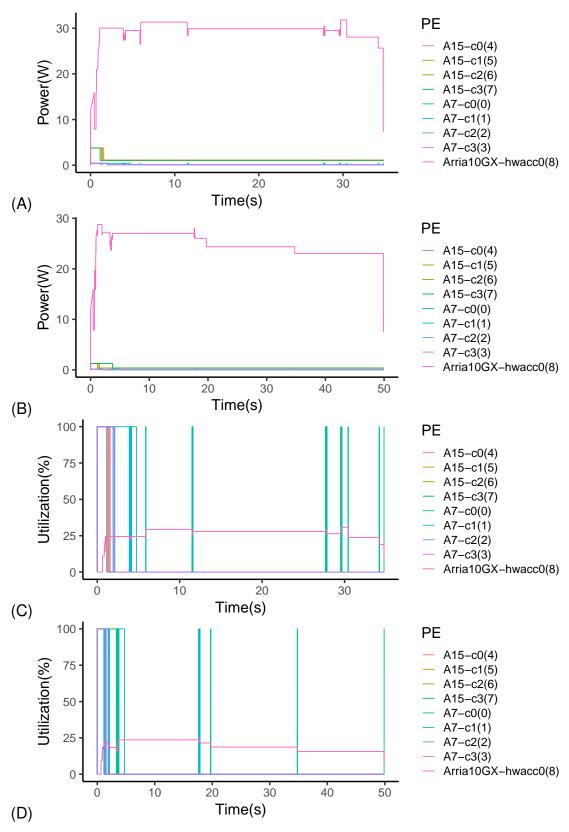

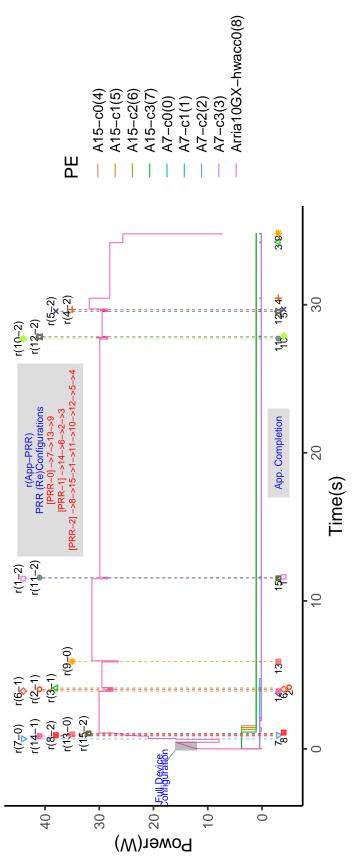

Meta-heuristics are solution methods that control the interaction between local improvement procedures and high-level strategies to create processes capable of escaping from local optimal and that perform a robust search for a solution space (GEN-DREAU; POTVIN, 2010, p. vii). On the other hand, TALBI (2009) defines meta-heuristics as general high-level methodologies (templates) used as guiding strategies in the development of related heuristics to solve specific optimization problems.