# UNIVERSIDADE FEDERAL DE PELOTAS Centro de Desenvolvimento Tecnológico Programa de Pós-Graduação em Computação

**Thesis**

**Sharing-Aware Thread Mapping in Software Transactional Memory**

**Douglas Pereira Pasqualin**

# **Douglas Pereira Pasqualin**

**Sharing-Aware Thread Mapping in Software Transactional Memory**

Thesis presented to the Graduate Program in Computing at the Technology Development Center of the Federal University of Pelotas, in partial fulfillment of the requirements for the degree of Doctor of Computer Science.

Advisor: Dr. André Rauber Du Bois

Coadvisores: Dr. Matthias Diener

Dr. Maurício Lima Pilla

# Universidade Federal de Pelotas / Sistema de Bibliotecas Catalogação na Publicação

# P284s Pasqualin, Douglas Pereira

Sharing-aware thread mapping in software transactional memory / Douglas Pereira Pasqualin ; André Rauber Du Bois, orientador ; Matthias Diener, Maurício Lima Pilla, coorientadores. — Pelotas, 2021.

114 f.: il.

Tese (Doutorado) — Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, 2021.

1. Software transactional memory. 2. Sharing-aware. 3. Thread mapping. 4. Communication. I. Bois, André Rauber Du, orient. II. Diener, Matthias, coorient. III. Pilla, Maurício Lima, coorient. IV. Título.

CDD: 005

#### **Douglas Pereira Pasqualin**

### **Sharing-Aware Thread Mapping in Software Transactional Memory**

Thesis approved in partial fulfillment of the requirements for the degree of Doctor of Computer Science, Graduate Program in Computing, Technology Development Center, Federal University of Pelotas.

Defense Date: 28 April 2021

#### **Examination Board:**

Dr. André Rauber Du Bois (advisor)

PhD in Computer Science from the Heriot-Watt University, Scotland.

Dr. Laércio Lima Pilla

PhD in Computer Science from the Federal University of Rio Grande do Sul (UFRGS), Brazil and Université Grenoble Alpes, France.

Dr. Alexandro José Baldassin

PhD in Computer Science from the State University of Campinas (UNICAMP), Brazil

Dr. Gerson Geraldo Homrich Cavalheiro

PhD in Informatique Systèmes et Communications from the Institut National Polytechnique de Grenoble, France.

| This is dedicated to my wife Daiane and my son     |

|----------------------------------------------------|

| Nicolas, for their endless love and encouragement. |

|                                                    |

#### **ACKNOWLEDGMENTS**

Finally, it is time to write this hard part of the thesis. The acknowledgments! Although it is an optional element of the document, I think that it should be mandatory. It is nearly impossible to imagine developing a PhD thesis alone. Many people work together and backstage, but all are fundamental to reach the final objective. Now it is time to thank them all.

Firstly, I would like to thank my advisor team. Indeed, I do not have just an advisor and a co-advisor, but a team of three advisors. Each one started in a distinct phase of this thesis. So, I thank you, Prof. Dr. André Du Bois, for accepting me as a PhD student. Also, for your support and confidence in me. Prof. Dr. Maurício Pilla, for sharing profound knowledge and guidance during my initial studies on the thesis subject. Finally, Dr. Matthias Diener, I have no words to thank you for all your support. Our contact started with a simple question about your work on Facebook and finished with you being officially my co-advisor. My sincerely *Herzlichen Dank*.

I also would like to thank another team that was always working backstage: my family! Especially my wife Daiane, my son Nicolas and my mom Maria. Thank you for the support and encouragement during these four long years, including giving me the strengths to continue when sometimes I thought that I would not be able to make it! But I did it! This achievement is also yours.

Lastly, I would like to thank my employer (CPD and UFSM) to grant me the privilege of getting a license of my professional activities. Hence, it was possible to dedicate my full time to my PhD studies.

"Accessing memory is more like mailing a letter than making a phone call"

(THE ART OF MULTIPROCESSOR PROGRAMMING, PAGE 471)

# **ABSTRACT**

PASQUALIN, Douglas Pereira. **Sharing-Aware Thread Mapping in Software Transactional Memory**. Advisor: André Rauber Du Bois. 2021. 114 f. Thesis (Doctorate in Computer Science) – Technology Development Center, Federal University of Pelotas, Pelotas, 2021.

Software Transactional Memory (STM) is an alternative abstraction for thread synchronization in parallel programming. One advantage is simplicity since it is possible to replace the use of explicit locks with atomic blocks, while the STM runtime is responsible to ensure a consistent execution, for instance, without deadlocks and race conditions. Regarding STM performance, many studies already have been made focusing on reducing the number of transactional aborts and conflicts. However, in current multicore architectures with complex memory hierarchies, it is also important to consider where the memory of a program is allocated and how it is accessed. This thesis proposes the use of a technique called sharing-aware mapping, which maps threads to cores and memory pages to NUMA nodes based on their memory access behavior to achieve better performance in STM systems. The first major contribution of this thesis is a mechanism to detect sharing behavior directly inside the STM library by tracking and analyzing how threads perform STM operations. The collected information can be used to perform an optimized mapping of the application's threads to cores in order to improve the efficiency of STM operations. The second contribution of this thesis is the characterization of the sharing behavior of STM applications by using information extracted from the STM runtime, providing information to guide thread mapping based on their sharing behavior. The third contribution is a mechanism to perform sharing-aware thread mapping in STM applications. We first introduce Static-SharingAware (SSA), which map threads to cores based on a previous analysis of the sharing behavior of STM applications. Next, we introduce STMap, an online, low overhead mechanism to detect the sharing behavior and perform the mapping directly inside the STM library, by tracking and analyzing how threads perform STM operations during the execution. In experiments with the STAMP benchmark suite and synthetic benchmarks, both mechanisms showed performance gains when compared to the default Linux scheduler.

Keywords: Software Transactional Memory. Sharing-aware. Thread Mapping. Communication.

#### **RESUMO**

PASQUALIN, Douglas Pereira. **Mapeamento de** *Threads* **Baseado em Comparti-Ihamento em Memórias Transacionais em Software**. Orientador: André Rauber Du Bois. 2021. 114 f. Tese (Doutorado em Ciência da Computação) — Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, Pelotas, 2021.

Memória Transacional em Software (MTS) é uma abstração para a sincronização de threads na programação paralela. Uma de suas vantagens é a simplicidade, pois é possível substituir o uso de bloqueios por blocos atômicos. Além disso, a implementação de MTS é responsável por garantir uma execução consistente, por exemplo, sem deadlocks ou condições de corrida. Com relação ao desempenho de MTS, existem muitos estudos focados na redução do número de cancelamentos. Contudo, nas atuais arquiteturas *multicore*, com complexas hierarquias de memória, é também importante considerar onde a memória do programa está alocada e como ela é acessada. Esta tese propõe o uso de uma técnica chamada mapeamento baseado em compartilhamento a qual consiste em mapear threads para núcleos de processamento e páginas de memória para nós NUMA com base no seu padrão de acesso à memória para melhorar o desempenho de aplicações que utilizam MTS. A primeira contribuição desta tese é um mecanismo para detectar o padrão de acesso à memória em bibliotecas de MTS. Ele consiste em rastrear e analisar como threads executam operações de MTS. As informações coletadas podem ser utilizadas para criar um mapeamento otimizado de threads para núcleos de processamento, com o objetivo de melhorar a eficiência das operações de MTS. A segunda contribuição é a caracterização do padrão de acesso à memória de aplicações que utilizam MTS, fornecendo informações para guiar um mapeamento de threads com base no padrão de compartilhamento da aplicação. A terceira contribuição é um mecanismo para efetuar um mapeamento de threads baseado em compartilhamento para aplicações que utilizam MTS. Primeiramente é apresentado Static-SharingAware (SSA), que baseado em uma análise prévia do padrão de compartilhamento da aplicação, mapeia threads para núcleos de processamento de forma estática. Após, é apresentado STMap, um mecanismo que opera dinamicamente e com baixa sobrecarga, com o objetivo de detectar o padrão de acesso à memoria e efetuar o mapeamento de threads durante a execução do programa. Em experimentos com o benchmark STAMP e outras aplicações sintéticas, ambos mecanismos apresentaram ganhos de desempenho quando comparados com o escalonador padrão do Linux.

Palavras-chave: Memória Transacional em Software. Sensibilidade ao compartilhamento. Mapeamento de thread. Comunicação.

# **LIST OF FIGURES**

| Figure 1 Data structures utilized internally by the STM library TinyST Source: (FELBER et al., 2010). R/W sets stands for read and wrisets. A snapshot corresponds to a range of valid linearization point LB and UB stand for lower and upper bounds, i.e, the validity range of the snapshot.  Figure 2 Examples of communication matrices |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 26<br>30<br>31<br>32                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------|

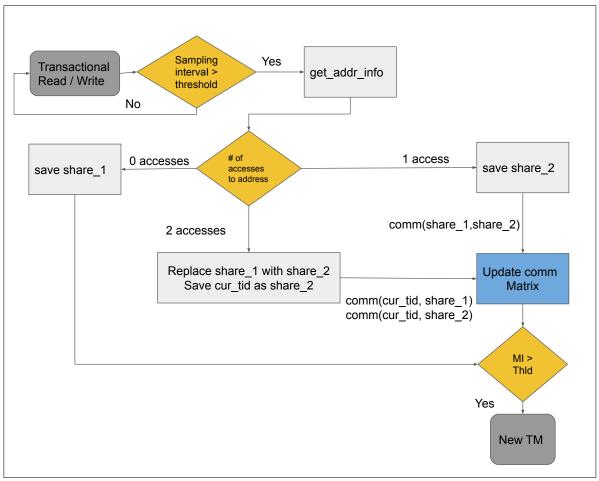

| Figure 5 Figure 6 Figure 7 Figure 8 Figure 9 Figure 10 Figure 11                                                                                                                                                                                                                                                                             | Mechanism for detecting communication patterns. Data structures are shown for an application consisting of 4 threads (0-3.) Flowchart of the proposed mechanism                                                                                                                                                                                                                                                                                                                                                          | 51<br>52<br>55<br>56<br>56<br>57       |

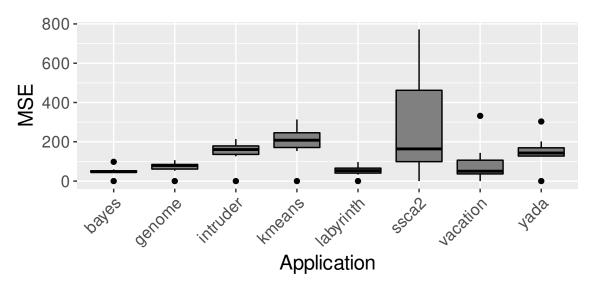

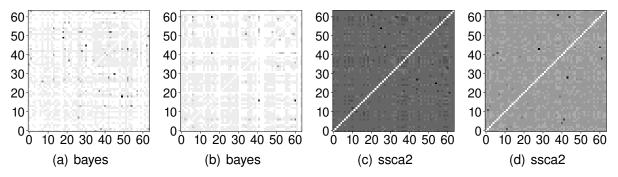

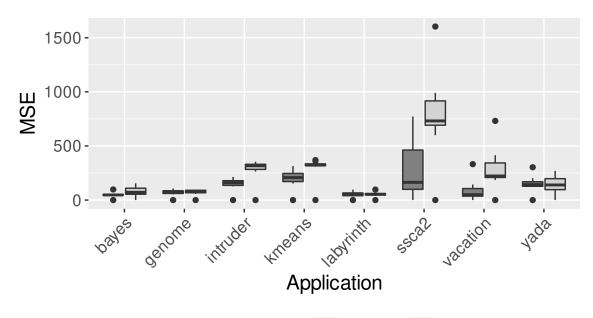

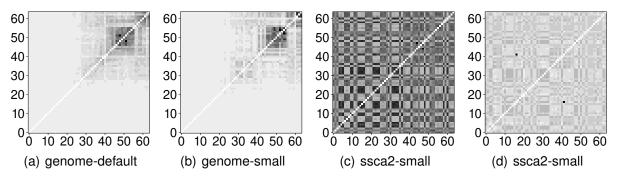

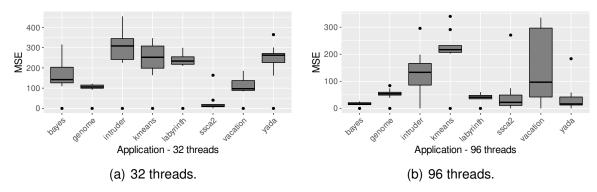

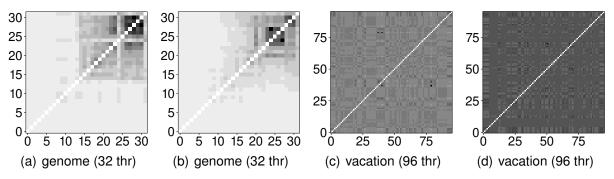

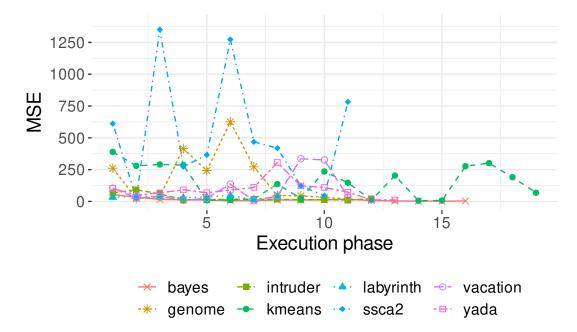

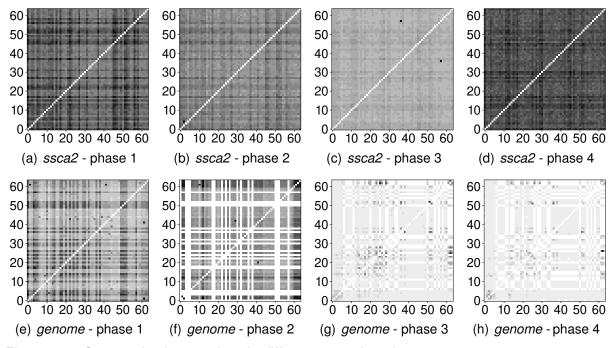

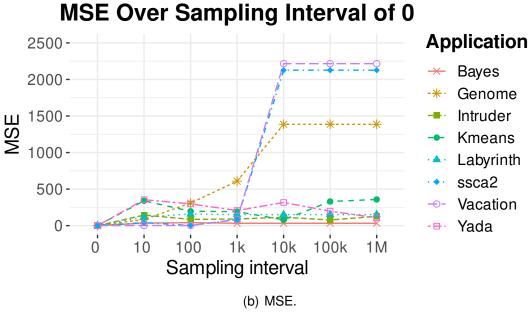

| Figure 12 Figure 13 Figure 14 Figure 15 Figure 16 Figure 17 Figure 18 Figure 19 Figure 20                                                                                                                                                                                                                                                    | Stability of the sharing behavior across different executions.  Matrices with highest and lowest MSEs between different executions.  Stability of the sharing behavior when changing input parameters.  Matrices with highest and lowest MSEs.  Stability of the sharing behavior when changing the number of threads.  Matrices with the lowest and highest MSEs.  Comparing the MSE on different execution phases.  Communication matrices in different execution phases.  Original source code of kmeans application. | 61<br>62<br>63<br>64<br>64<br>65<br>65 |

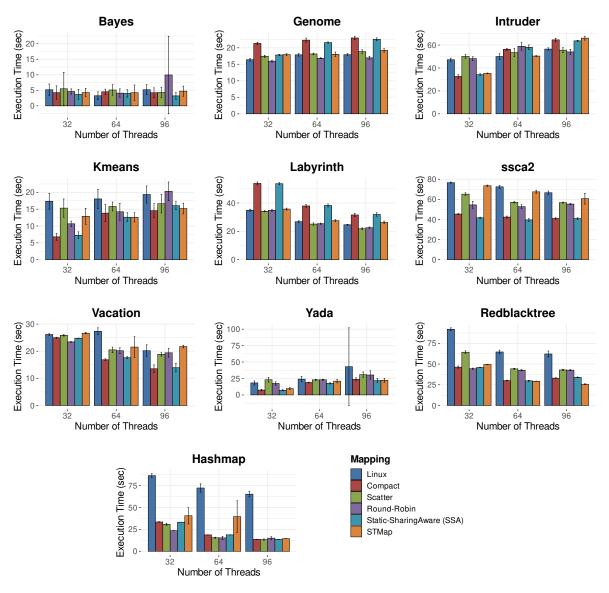

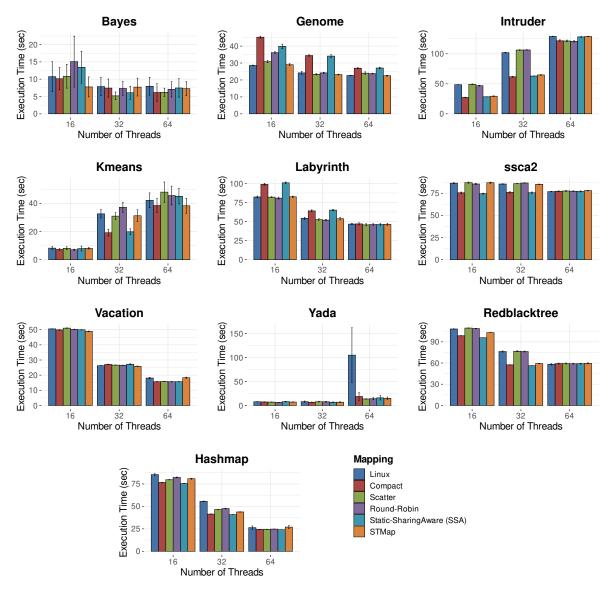

| Figure 21<br>Figure 22<br>Figure 23<br>Figure 24<br>Figure 25                                                                                                                                                                                                                                                                                | Thread mapping strategies                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 69<br>71<br>72<br>75                   |

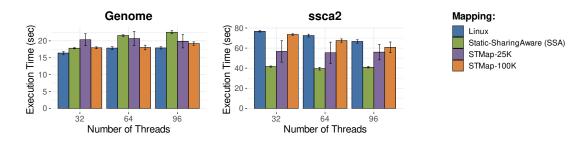

| Figure 26<br>Figure 27<br>Figure 28                                                                                                                                                                                                                                                                                                          | Execution time results on the Xeon machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 81<br>83<br>85                         |

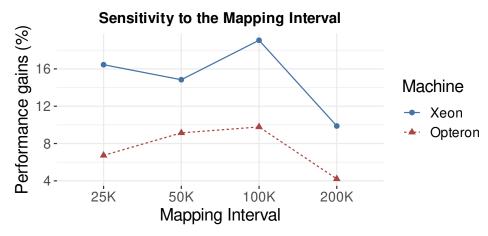

| Figure 29 | Comparing STMap using different mapping intervals on the Xeon machine                                  | 85  |

|-----------|--------------------------------------------------------------------------------------------------------|-----|

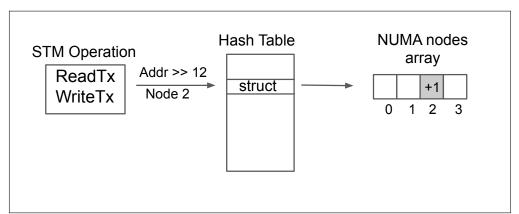

| Figure 30 | Mechanism for detecting page accesses. Data structures are shown for a NUMA machine with 4 nodes (0-3) | 108 |

| •         | Execution time of the Array Sum application                                                            | 111 |

| Figure 32 | Average speedup of the mappings when compared to Linux-NOff                                            | 113 |

# **LIST OF TABLES**

| Table 1                       | Applications from STAMP benchmark. Source: (MINH et al., 2008).                                                                                                                                            | 28             |

|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| Table 2                       | Comparison of related work on thread and data mapping for STM applications                                                                                                                                 | 48             |

| Table 3                       | Default arguments for the programs used in the experiments                                                                                                                                                 | 54             |

| Table 4<br>Table 5<br>Table 6 | Analysis of accessed STM memory addresses in STAMP applications. Small input parameters used in the experiments in Section 5.2.3 Kmeans performance gains with source code changes to reduce false sharing | 60<br>62<br>66 |

| Table 7<br>Table 8<br>Table 9 | Average performance gains of each mechanism over Linux Characteristics used to define the heuristic and the mapping interval. Average performance gains of each mechanism over Linux                       | 74<br>77<br>84 |

| Table 10                      | NUMA factor of the machines used in the experiments                                                                                                                                                        | 112            |

# LIST OF ABBREVIATIONS AND ACRONYMS

ACC Adaptive Concurrency Control

ATS Adaptive Transaction Scheduling

AR Abort Ratio

BAT Best Alternative Transaction

CAR Collision Avoidance and Resolution

CB Contention Bit

CDSM Communication Detection in Shared Memory

CFS Completely Fair Scheduler

CI Contention Intensity

CL Concurrency Level

CM Contention Manager

CMP Chip Multiprocessor

CP Contention Predictor

CPU Central Processing Unit

CR Commit Ratio

DA Distinct Addresses

DoT Dominant Thread

DS Dynamic Serializer

DVFS Dynamic Voltage and Frequency Scaling

F2C2 Flux-based Feedback-driven Concurrency Control

GC Garbage Collector

GPU Graphics Processing Unit

HPC High Performance Computing

HTM Hardware Transactional Memory

IBS Instruction-Based Sampling

kMAF kernel Memory Affinity Framework

LLC Last-Level Cache

LO-SER Low-Overhead Serializing Algorithm

LSA Lazy Snapshot Algorithm

LUTS Light-Weight User-Level Transaction Scheduler

MAi Memory Affinity Interface

MI Mapping Interval

ML Machine Learning

MPI Message Passing Interface

MSE Mean squared error

NPB NAS Parallel Benchmark

NUMA Non-Uniform Memory Access

PEW Percentage of the Effective Work

PoCC P-only Concurrency Controller

ProPS Progressively Pessimistic Scheduling

SC Saturating Counter

SCA Speculative Contention Avoidance

SI Sample Interval

SRP Success-Reward Policy

SSER+ Stricter Serializability

RS Read-set

TBB Threading Building Blocks

TCR Transaction Commit Ratio

TCP Transmission Control Protocol

TLB Translation Lookaside Buffer

TM Transactional Memory

SOA Steal-on-Abort

SSA Static-SharingAware

STAMP Stanford Transactional Applications for Multi-Processing

STM Software Transactional Memory

UMA Uniform Memory Access

VIT Very Important Transaction

WACC Weighted Adaptive Concurrency Control

WS Write-set

# **CONTENTS**

| 1 IN<br>1.1<br>1.2<br>1.3<br>1.4                                                                      | NTRODUCTION                                                                                                                                                                                                                                                    | 17<br>18<br>19<br>20<br>21                                           |

|-------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| <ul><li>2 B</li><li>2.1</li><li>2.1.1</li></ul>                                                       | ACKGROUND                                                                                                                                                                                                                                                      | 22<br>22<br>22                                                       |

| 2.1.2<br>2.1.3                                                                                        | Design Choices                                                                                                                                                                                                                                                 | 23                                                                   |

| 2.2<br>2.3                                                                                            | Benchmarks for STM                                                                                                                                                                                                                                             | 28<br>29                                                             |

| 2.3.1<br><b>2.4</b><br><b>2.5</b>                                                                     | Communication/sharing matrix                                                                                                                                                                                                                                   | 30<br>30<br>33                                                       |

|                                                                                                       | ELATED WORK                                                                                                                                                                                                                                                    | 34                                                                   |

| 3.1<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5<br>3.2<br>3.3<br>3.3.1<br>3.3.2<br>3.4<br>3.5<br>3.6 | Transactional schedulers Feedback-driven Reactive Prediction-driven Mixed Heuristics Others  Thread and data mapping in STM  Thread and data mapping in general applications Offline Techniques Online Techniques Workload characterization Discussion Summary | 34<br>35<br>37<br>38<br>39<br>40<br>41<br>42<br>43<br>45<br>47<br>48 |

| 4 D<br>4.1<br>4.2<br>4.3<br>4.4                                                                       | CETECTING MEMORY ACCESS BEHAVIOR IN STM APPLICATIONS  Overview                                                                                                                                                                                                 | 50<br>50<br>51<br>53<br>54                                           |

| • | 4.4.2<br>4.4.3<br><b>4.5</b>                                                                  | Communication matrices                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                            |

|---|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|

|   | <b>5.1</b> 5.1.1 5.1.2 5.1.3 <b>5.2</b> 5.2.1 5.2.2 5.2.3 5.2.4 5.2.5 <b>5.3</b>              | HARACTERIZATION OF SHARING-BEHAVIOR OF STM APPLICATIONS  Methodology of the Characterization  Detecting sharing in STM applications  Mean squared error (MSE)  Experiments  Characterization of sharing behavior  STM memory access information  Stability of sharing behavior across different executions  Stability of sharing behavior when changing input parameters  Stability of sharing behavior with different numbers of threads  Dynamic behavior during execution  False sharing in kmeans  Summary | 58<br>58<br>58<br>59<br>60<br>61<br>62<br>63<br>64<br>66<br>67             |

|   | <b>6.1</b> 6.1.1 6.1.2 6.1.3 6.1.4 <b>6.2</b> 6.2.1 6.2.2 6.2.3 6.2.4 6.2.5 6.2.6 6.2.7 6.2.8 | HARING-AWARE THREAD MAPPING IN STM Static thread mapping  Methodology Results on the Xeon Machine Results on the Opteron Machine Discussion  Online thread mapping Reducing the overhead of online detection Calculating the mapping Final algorithm Implementation Results on the Xeon Machine Results on the Opteron Machine Discussion Mechanism sensitivity  Summary                                                                                                                                       | 68<br>68<br>70<br>72<br>73<br>74<br>76<br>80<br>80<br>82<br>84<br>85<br>86 |

|   | 7 C(<br>7.1                                                                                   | ONCLUSION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 87<br>88                                                                   |

|   | REFE                                                                                          | RENCES                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 90                                                                         |

|   | A.1<br>A.2<br>A.3<br>A.4<br>A.5                                                               | Algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 108<br>108<br>110<br>112<br>112<br>113                                     |

# 1 INTRODUCTION

At the beginning of the year 2000, multicore processors started to be produced. This decision was taken due to the microarchitectural limitations and, higher power consumption and heat dissipation involved on improving the performance of a single CPU (TRONO, 2015). Since then, the number of cores in a single chip is growing every year. Today, desktops and even cellphone processors are multicore. Besides, servers normally have many processors and each one is multicore.

The simplest architecture for multiprocessors systems are based on a single bus, i.e., one or more processors and memory modules use the same bus for communication. In this architecture, every memory word can be read with the same latency. Hence, they are named UMA (Uniform Memory Access). However, these architectures have a scalability problem as the number of CPUs grow, as all communication needs to pass by the single bus.

One alternative is to replace the single bus with multiple nodes, where each node is a multiprocessor connected directly to a local memory module (GAUD et al., 2015). These architectures are called NUMA (Non-Uniform Memory Access) and are becoming dominant in servers (CALCIU et al., 2017). In NUMA machines, programs have access to the entire memory. In a transparent way, data can be stored in the local node or in a node that belongs to other processor (remote node). Interconnect links between nodes are asymmetric and have different bandwidths (LEPERS; QUÉMA; FEDOROVA, 2015). Hence, the location of the data plays an important role in the performance.

Accessing a remote node implies higher latency, making the access time non-uniform, i.e., depends on the location of the data.

In order to better exploit the parallelism available in these modern architectures, software must be parallel and scalable (GRAHN, 2010). An important issue that arises in parallel programming is thread synchronization, and it is the major cause that prevents the scalability of applications (DAVID; GUERRAOUI; TRIGONAKIS, 2013). Synchronization is necessary when multiple concurrent threads need to access at the same time a shared variable and, at least one thread needs to write to this shared variable. If there is no synchronization, a race condition can happen (NETZER; MILLER, 1992), possibly

leading to non-deterministic results (TRONO, 2015). The block of code that needs to be protected in order to not be accessed at the same time by different processes is called *critical section* (RAYNAL, 2013).

Mutual-exclusion locks are one of the most used abstractions to protect critical sections (FRASER; HARRIS, 2007). However, the semantics of locks is not intuitive. Programmers need to explicitly acquire and release locks, making the source code hard to read and debug (ANTHES, 2014). Besides, if more than one lock was acquired in a critical section, they need to be released in the same order, to avoid *deadlocks* (HERLIHY; SHAVIT, 2008). The performance of locks depends on the size of the critical section that it protects. Coarse-grained locks are easy to program but the parallelism is limited (DICE; SHALEV; SHAVIT, 2006). On the other hand, fine-grained locks provide good performance but they are hard to use (DICE; SHAVIT, 2007).

An alternative abstraction to replace mutual-exclusion locks in parallel programming is the *Transactional Memory* (TM) (HARRIS; LARUS; RAJWAR, 2010; GRAHN, 2010), in which critical-sections are accessed using transactions similar to the ones available in databases. With TM, instead of explicitly acquiring and releasing locks, the programmer only needs to delimit the block of code that he wants to be executed atomically as a transaction. The TM runtime is responsible to ensure a consistent execution, e.g., without deadlocks and race conditions. A transaction that has executed without conflicts can commit, i.e., update the memory with the new values. If a conflict was detected an abort is executed and a transaction is reinitialized until a commit is possible. Thus, an impression of atomicity is given to the programmer. Although there are TMs implemented in hardware (HTM) and in software (STM), this thesis focuses on the study of STM, where transaction consistency is guaranteed by a software library. An advantage of an implementation in software is that it is more flexible and not dependent on hardware. Also, it does not have the same resource limitations as in hardware (GRAHN, 2010).

#### 1.1 Motivation

There are many compilers and programming languages that already support transactional memory constructs, such as C++ (since the standard C++11¹), Haskell, Scala and .NET Framework (GRAMOLI; GUERRAOUI, 2017). Besides, some researches already showed that STM can outperform locks in some scenarios (DICE; SHAVIT, 2007; DRAGOJEVIĆ et al., 2011). Unfortunately, there are scenarios where the overhead added by the management of internal metadata of the STM or a high number of aborts, limits good performance (GRAMOLI; GUERRAOUI, 2014). Due to these limitations, improving performance of STM is an active research area. There are several proposals

<sup>1&</sup>lt;https://gcc.gnu.org/wiki/TransactionalMemory>

for increasing the performance of STM systems. However, the majority of them focus on reducing the number of conflicts (transactional aborts). One technique is the use of a transactional scheduler, acting proactively, using heuristics to prevent conflicts and to decide *when* and *where* a transaction should be executed (DI SANZO, 2017).

Current multicore architectures have complex memory hierarchies and different latencies for memory accesses. Hence, a thread placement that improves the use of memory controllers and data locality is important to achieve good performance. A technique called *sharing-aware mapping*<sup>2</sup> (CRUZ; DIENER; NAVAUX, 2018) aims to map threads to cores and memory pages to NUMA nodes considering their memory access behavior. Since STM is used to synchronize data accessed by multiple threads, an efficient mapping will help to make better usage of caches and memory controllers, hence improving the overall performance. Besides, STM provides interesting mapping opportunities since the STM runtime has precise information about memory areas that are shared between threads, their respective memory addresses, and the intensity with which they are accessed by each thread. Hence, contrary to prior works on sharing-aware thread mapping, it is not necessary to keep track of all memory access of the applications, only the STM accesses. Therefore, the proposed mechanism will have a low overhead and can perform sharing-aware thread mapping accurately for STM applications.

#### 1.2 Contributions

The main objective of this thesis is to investigate the use of sharing-aware mapping in the context of STM. Contrary to previous sharing-aware mapping proposals that rely on memory traces of the entire application, our proposal has lower overhead and better accuracy because only memory accesses that are in fact shared between threads are traced. Beyond that, this sharing-aware mapping will improve the overall performance of STM applications by improving the cache usage and interconnection traffic. More specifically, this thesis makes the following contributions:

- We developed a low overhead mechanism to **detect the sharing behavior of STM applications**, by tracking and analyzing how threads perform STM operations (Chapter 4).

- We made an in-depth characterization of STM applications, regarding memory access behavior, using the proposed mechanism. This characterization is used to define the suitability for a thread mapping based on communication behavior and defining which type of mapping policy is more appropriate (static or dynamic) (Chapter 5).

<sup>&</sup>lt;sup>2</sup>This research field is also known as topology-aware mapping (JEANNOT et al., 2013; UNAT et al., 2017).

- We show how a **static thread mapping** (where threads are mapped to cores at the beginning of execution, and never migrated) is sufficient to improve the overall performance of the majority of STM applications (Chapter 6, Section 6.1).

- We extend the proposed mechanism to perform online detecting sharing behavior and mapping. We developed a heuristic to disable the mechanism if it determines that the application will not benefit from a new thread mapping (Chapter 6, Section 6.2).

#### 1.3 Publications

The following papers were published during the PhD program and contain material that is relevant to this thesis:

- Douglas P. Pasqualin, Matthias Diener, André R. Du Bois, Maurício L. Pilla. "Thread Affinity in Software Transactional Memory." 19th International Symposium on Parallel and Distributed Computing (ISPDC), July 2020 (PASQUALIN et al., 2020b).

- Douglas P. Pasqualin, Matthias Diener, André R. Du Bois, Maurício L. Pilla. "Online Sharing-Aware Thread Mapping in Software Transactional Memory."

32nd International Symposium on Computer Architecture and High Performance Computing (SBAC-PAD), September 2020 (PASQUALIN et al., 2020a).

- 3. <u>Douglas P. Pasqualin</u>, Matthias Diener, André R. Du Bois, Maurício L. Pilla. "Characterizing the Sharing Behavior of Applications using Software Transactional Memory." Benchmarking, Measuring, and Optimizing (Bench'20). November 2020. (Best Paper Award and Award for Excellence for Reproducible Research) (PASQUALIN et al., 2021).

The following papers were also submitted for publication and are currently under peer-review:

- 1. <u>Douglas P. Pasqualin</u>, Matthias Diener, André R. Du Bois, Maurício L. Pilla. "STMap: Sharing-Aware Thread Mapping in Software Transactional Memory." Journal of Parallel and Distributed Computing (JPDC).

- Douglas P. Pasqualin, Matthias Diener, André R. Du Bois, Maurício L. Pilla. "Sharing-Aware Data Mapping in Software Transactional Memory." SAMOS XXI - International Conference on Embedded Computer Systems: Architectures, Modeling and Simulation.

# 1.4 Document organization

The remainder of this thesis is organized as follows. Chapter 2 presents the background of different topics used in this thesis, such as TM and sharing-aware mapping. Chapter 3 presents the works related to the thesis subject. Also, we discuss the differences between our contributions with related work. Chapter 4 presents the first contribution of this thesis, i.e, a mechanism to detected the sharing behavior of STM applications, by tracking and analyzing how threads perform STM operations. Chapter 5 uses the proposed mechanism of Chapter 4 to perform an in-depth characterization of STAMP, a frequently used TM benchmark suite, regarding memory access behavior. It includes information about the suitability for thread mapping of each STAMP application, its communication pattern, and its dynamic behavior, among others. Chapter 6 shows how to use the proposed mechanism to perform static and online thread mapping based on the memory access behavior of STM operations. Finally, Chapter 7 presents the conclusion and future work. We also included Appendix A which shows how to extend the online sharing-aware thread mapping mechanism to include data mapping.

# 2 BACKGROUND

This chapter covers the background on the range of different topics which are important to this thesis. It starts by explaining transactional memory (Section 2.1) and sharing-aware mapping (Section 2.3). Benchmarks for STM are briefly described in Section 2.2. We also include a small experiment to show the benefits of sharing-aware thread mapping for STM applications (Section 2.4).

# 2.1 Transactional Memory

Transactional memory (TM) is an abstraction to synchronize accesses to shared variables. Instead of using locks, the programmer only needs to enclose the critical section in an atomic block, which will be executed as a transaction. The concept of transactions was borrowed from Databases. In fact, the first idea to use Database transactions in programming languages was described by Lomet (1977). Sixteen years later, Herlihy and Moss (1993) proposed hardware support for TM. The first implementation purely on software (STM) was proposed by Shavit and Touitou (1995) as a flexible alternative not dependent on hardware. There are also hybrid approaches (DAMRON et al., 2006) that combine implementation both on hardware and software.

#### 2.1.1 General Concepts

The execution of a transaction needs to be *atomic*. Atomicity requires that a transaction is executed as a whole or it needs to appear as it was never executed (HARRIS; LARUS; RAJWAR, 2010; GRAHN, 2010). This property is also known as "all-or-nothing" (ÖZSU; VALDURIEZ, 1996). A transaction *commits* if executed without conflicts, hence all operations and results are made visible to the rest of the system (GRAHN, 2010). If conflicts are detected, a transaction *aborts*, i.e., all operations are discarded, and the transaction needs to restart until a commit is possible. This idea is associated with another important property called *isolation*: all memory updates of a running transaction can not be visible to other transactions before a commit.

The sequence of operations performed by all transactions in a given execution is

called *history* (GUERRAOUI; KAPALKA, 2008). If one transaction executes only after the end of the other they are serial, otherwise *concurrent* (HARRIS; LARUS; RAJWAR, 2010). If they are concurrent, conflicts could occur between them. A conflict occurs when two transactions perform operations in the same memory location, and at least one of these operations is a write.

As transactions can execute concurrently, correctness criteria were proposed to ensure that the TM system produces correct results. One of the most used criteria is Opacity (GUERRAOUI; KAPALKA, 2008), that is an extension of the classical database criteria Strict Serializability (PAPADIMITRIOU, 1979). Serializability says that the result of executing concurrent transactions in a given history must be equal to a serial execution. Strict Serializability says that real-time order must be respected. If  $T_1$  finishes before  $T_2$  starts, then  $T_1$  must occur before  $T_2$  in the equivalent serial execution (HARRIS; LARUS; RAJWAR, 2010). Opacity extends these concepts to aborted transactions, i.e., all transactions in a given history, including aborted, must appear to be executed in a serial order.

#### 2.1.2 Design Choices

Although the main purpose of TM is to provide a simple interface to manage accesses to shared resources, its implementation is not trivial. Many different design options are available such as transaction granularity, version management, conflict detection and resolution. The next subsections describe these design options.

#### 2.1.2.1 Version Management

TMs use version management of memory locations to manage the writes of concurrent transactions. Two approaches are used (HARRIS; LARUS; RAJWAR, 2010; FELBER et al., 2010):

- Eager, direct update or write-through: data is modified directly in memory. Older values are stored in an *undo-log*. In case of an abort the log is used to restore the old values.

- Lazy, deferred update or write-back: instead of updating data directly in memory, new values are stored in an *redo-log*. During a commit, the log is used to set new values to memory. In case of an abort, the log is discarded.

Eager versioning makes committing faster, whereas lazy versioning makes aborting faster (GRAHN, 2010).

#### 2.1.2.2 Transaction Granularity

The granularity is the dimension used for conflict detection, i.e., the level used for keeping track of memory locations. One option is to use memory **word** granularity. The

main advantage is that no false conflicts happen. However it adds a high overhead in terms of time and space to keep the metadata (GRAHN, 2010). **Object** granularity is most used in object-based languages (CASTRO, 2012). However it can lead to false conflicts, i.e., transactions accessing the same object but different fields (LARUS; KOZYRAKIS, 2008). For HTM, **cache line** granularity is the most suitable (GRAHN, 2010).

#### 2.1.2.3 Conflict Detection

Similar to version management, there are two approaches to deal with conflict detection between concurrent transactions (GRAHN, 2010):

- Eager, early, pessimistic or encounter-time: conflicts are verified on each memory location read or written exactly when it occurs. In STM this could be done using locks or version number on memory locations. Thus, to access a value, a transaction needs to acquire its ownership, preventing others from accessing it (BANDEIRA et al., 2015).

- Lazy, late, optimistic or commit-time: conflicts are verified only at commit time. It allows multiple transactions to access shared data and continue executing even if they conflict, as the TM system will detect and resolve them on commit time (HARRIS; LARUS; RAJWAR, 2010, p. 20).

These options could be combined, for instance, lazy conflict detection for reads and eager for writes (BANDEIRA et al., 2015).

#### 2.1.2.4 Conflict Resolution

All operations executed by a transaction that aborts could be seen as a wasted work (SPEAR et al., 2009; ANSARI et al., 2009; ZHOU et al., 2016). Thus, the total aborts in an execution have a strong relationship with the final performance. In case of conflicts, choosing which transaction needs to be aborted is a responsibility of the *Contention Manager* (CM) (YOO; LEE, 2008). When two transactions  $T_A$  and  $T_B$  conflict, the transaction that has detected the conflict, suppose  $T_A$ , asks the CM what to do. The actions could be, for instance, abort immediately or wait a determined time, allowing  $T_B$  to finish, or force and abort of  $T_B$  (GUERRAOUI; HERLIHY; POCHON, 2006). There are many CMs proposed in the literature with different purposes. A few examples of them are (SCHERER III; SCOTT, 2005; SPEAR et al., 2009; HARRIS; LARUS; RAJWAR, 2010; GRAHN, 2010):

- Passive: the transaction that detected the conflict aborts and restart its execution.

- **Polite**: the transaction that detected the conflict could abort the conflicting one. However, aborting is delayed for a period of time, waiting the conflicting transaction

to end accessing values. The transaction can also wait for a fixed number of exponentially growing intervals before aborting the enemy.

- **Karma**: use priorities to define which transaction must abort. The priority is defined by the total of memory locations that a transaction has accessed. The total is cumulative, i.e., taking in consideration all aborts and re-executions.

- **Timestamp**: aborts the transaction that started earlier.

- Polka: a hybrid between Polite and Karma.

# 2.1.3 STM Implementation

The first STM implementations were non-blocking (SHAVIT; TOUITOU, 1997), more specifically obstruction-free (HERLIHY et al., 2003). However, according to Ennals (2006), obstruction-free is essential in distributed systems but not appropriate for non-distributed STM. In the same publication, Ennals shows that lock-based STM are simpler to implement and faster. As a consequence many state-of-art STM implementations, for instance, TL2 (DICE; SHALEV; SHAVIT, 2006), TinySTM (FELBER et al., 2010) and SwissSTM (DRAGOJEVIĆ; GUERRAOUI; KAPALKA, 2009) are lock-based.

Other characteristic used in the first implementations was visible reads, i.e., all transactions knew who read a specific memory location. To implement this approach it is necessary a list to store all transactions who read a specific memory location. Thus, when a transaction writes new values in memory, it is possible to notify the readers that there is a conflict. The disadvantage of this approach arises when many distinct threads read the same memory location (FELBER et al., 2010). As most workloads are read-intensive, this approach limits the performance (SUTRA et al., 2018). The opposite solution is to use invisible reads, where other threads do not know who read a specific memory location. However, using this approach, a thread could be in an inconsistent state (due to a conflict) and does not know yet. Letting this transaction continue execution could bring an unwanted result, not guaranteeing Opacity or other consistency. Thus, a solution to using invisible reads is to periodically validate the read set, verifying if the memory locations read are still consistent. On the other hand, this solution is expensive, mainly if a transaction has read many memory locations. This cost keeps growing as the transaction keeps reading different memory locations. This problem is known as incremental validation (HARRIS; LARUS; RAJWAR, 2010).

To use invisible reads without the problem of incremental validation the concept of *global clock* was introduced in an independent way in the algorithms  ${\tt TL2}$  (DICE; SHALEV; SHAVIT, 2006) and  ${\tt LSA}$  (Lazy Snapshot Algorithm) (RIEGEL; FELBER; FETZER, 2006). The global clock is a counter utilized for versioning memory locations. When a transaction writes new values to memory, the global clock is incremented and

the new clock value is used as a version number for modified memory locations. In STM implementations that use a global clock, transactions still need to validate their read set, but in general, this is necessary only for write transactions during the commit phase. Read only transactions can commit without validation, because memory location were validated when read.

#### 2.1.3.1 Using a global clock

This section presents an overview of how an STM implementation that uses a global clock for versioning memory locations works. The operations described are based on algorithms TL2 (DICE; SHALEV; SHAVIT, 2006) and TinySTM (FELBER et al., 2010). However, minor details could be different depending on the STM implementation.

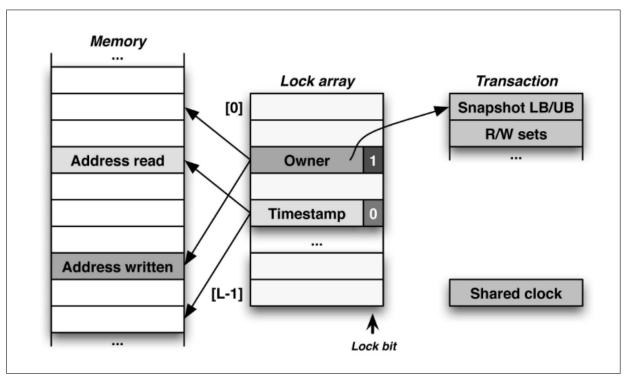

Figure 1 – Data structures utilized internally by the STM library <code>TinySTM</code>. Source: (FELBER et al., 2010). R/W sets stands for read and write sets. A snapshot corresponds to a range of valid linearization points. LB and UB stand for lower and upper bounds, i.e, the validity range of the snapshot.

Figure 1, represents the internal organization of TinySTM. Each transaction has two internal linked lists, called read-set (RS) and write-set (WS). These lists are utilized to keep track of memory locations read and written by transactions. Another important data structure for STMs, is the lock array, implemented using a hash table. This table is utilized to map memory locations to their related versioned locks. When a versioned lock is locked, its last bit is set to one and the remaining bits contain the owner of the memory location. If the lock is free, it contains the current version of the memory location, also called timestamp (Figure 1). Some authors call the lock array as *owner*-

*ship records* (orecs), because it associates memory locations with their current owners (DALESSANDRO; SPEAR; SCOTT, 2010).

To summarize, a transaction performs the follow operations. To make it simpler, we do not intent to cover all possible algorithm cases. The main idea is to show the basics of how an STM algorithm works.

- **Begin Transaction**: The current global clock value is copied to a local variable of the transaction. Normally, the variable name is rv which stands for **read version**. This value will be utilized to validate reads on memory locations.

- Read or Load: With eager version management (Section 2.1.2.1), the transaction verifies if it owns the lock of the memory location that is being read. If true, it returns directly the value stored in memory. If the lock of the memory location belongs to another transaction, an abort is necessary. Using lazy version management, the transaction first verifies if the memory location that it wants to read is in their WS. In that case, the transaction has already written to this location and the value in the WS must be returned. Otherwise, it is verified if the memory location is locked by another transaction. If true, an abort is necessary. Otherwise, the version associated with the memory location is compared with rv. If the version of the memory locations is greater than rv, an abort is necessary, as the memory location was updated after the transaction that is accessing it started. In case of abort, independently of the version management, the CM (Section 2.1.2.4) is triggered. STM implementations, such as TinySTM, try to do additional processing before aborting a transaction, for instance, the use of timestamp extension technique (RIEGEL; FELBER; FETZER, 2006). Finally, the address read is added to the RS and the content of the memory location is returned.

- Write or Store: First, it is necessary to verify if the memory location is locked. If true an abort is necessary. The next step, in case of **eager** conflict detection (Section 2.1.2.3) is to lock the memory location. If **eager** version management (Section 2.1.2.1) is utilized, the new value is updated directly on memory and the old one is stored in an undo-log. If the version management is **lazy**, the new value is stored in the WS to be updated at commit time.

- Commit: Read-only transactions can commit directly, as the memory locations were validated on the Read step. For write transactions, the first step is to validate the RS, verifying each address, if it is locked by other transaction and if the rv is still valid. If the implementation uses lazy version management (Section 2.1.2.1), all address in the WS should be locked. If it fails, the transaction aborts. In case of eager version management, addresses have already been locked in the Write step. Then, the global clock is advanced by 1 and the result is used as

| Application | Domain                        | Description                            |

|-------------|-------------------------------|----------------------------------------|

| bayes       | machine learning              | Learns structure of a Bayesian network |

| genome      | bioinformatics                | Performs gene sequencing               |

| intruder    | security                      | Detects network intrusions             |

| kmeans      | data mining                   | Implements K-means clustering          |

| labyrinth   | engineering                   | Routes paths in a maze                 |

| ssca2       | scientific                    | Creates efficient graph representation |

| vacation    | online transaction processing | Emulates travel reservation system     |

| yada        | scientific                    | Refines a Delaunay mesh                |

Table 1 – Applications from STAMP benchmark. Source: (MINH et al., 2008).

the new version for the values being updated. If **lazy** version management is used, the new values are updated in the memory. In the case of **eager** version management, the new values were updated in the **Write** step. A final step, for both version managements, is to release the locks and set the new version value of the memory location.

Abort: If the implementation uses eager version management, all values from the undo-log must be restored. Otherwise, the redo-log is discarded. A final step is to release all locks, if acquired.

#### 2.2 Benchmarks for STM

Together with the first STM proposals, researches also developed benchmarks for testing. In most of the cases, these benchmarks were simple, based on sets, lists and maps (HERLIHY et al., 2003; HARRIS; FRASER, 2003; SCHERER III; SCOTT, 2005; RIEGEL; FELBER; FETZER, 2006; DICE; SHAVIT, 2007). Hence, it was necessary to develop specific TM benchmarks to evaluate TM systems. More specifically, benchmarks with realistic characteristics. One of the first benchmarks proposed for evaluating STM systems were STMBench7 (GUERRAOUI; KAPALKA; VITEK, 2007) and Lee-TM (ANSARI et al., 2008c). After that, other suites and standalone benchmarks applications were proposed to evaluate TM systems, for instance, Eigenbench (HONG et al., 2010), RMS-TM (KESTOR et al., 2011) and, Memcached (RUAN et al., 2014).

Despite the effort on STM benchmarks proposal, the most used for evaluating TM implementations is the STAMP (*Stanford Transactional Applications for Multi-Processing*) (MINH et al., 2008). This suite is composed of 8 applications with realistic characteristics and that represent several application domains. Table 1 shows the domain and a short description of each application from STAMP benchmark.

STAMP still is the most used STM benchmark suite, as can be seen in recent researches (CHEN; GIBBONS; MOWRY, 2020; CARVALHO et al., 2020; DI SANZO et al., 2020; YU; ZUO; ZHAO, 2019; POUDEL; SHARMA, 2019; MURURU; GAVRILOVSKA;

# 2.3 Sharing-Aware Mapping

Data locality is an important factor in modern multicore and NUMA systems. One way to better explore locality is to map threads and data according to their *memory access behavior* (DIENER et al., 2016a). Hence, two types of mappings are possible (CRUZ; DIENER; NAVAUX, 2018):

- 1. **Thread mapping**: threads are associated to cores, improving the cache usage and interconnections, i.e., threads are mapped to cores that are close to each other in the underlying architecture.

- 2. **Data mapping**: memory pages are associated with NUMA nodes, optimizing the usage of memory controllers, i.e., memory pages are mapped to the same NUMA node where the core that is accessing them belongs.

Thread and data mapping based on the memory access behavior of applications is called **sharing-aware mapping** (CRUZ; DIENER; NAVAUX, 2018). Although the Linux kernel handles thread and data mapping, for thread mapping it does not take memory access patterns into consideration. For instance, the *Completely Fair Scheduler* (CFS) (WONG et al., 2008) used by default in the Linux kernel (DIENER et al., 2016a) mainly focuses on load balancing. For data mapping, the default policy is called *first-touch* (GAUD et al., 2015) where the memory is allocated in the NUMA node where the first access to the memory page is performed. Another data mapping policy available is *interleave*, that focuses on balance, allocating pages in a round-robin way on the NUMA nodes (LAMETER, 2013).

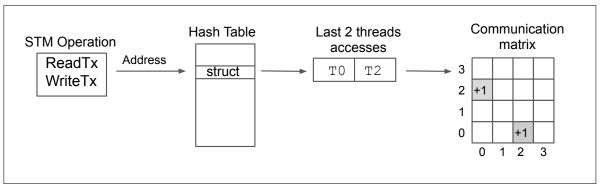

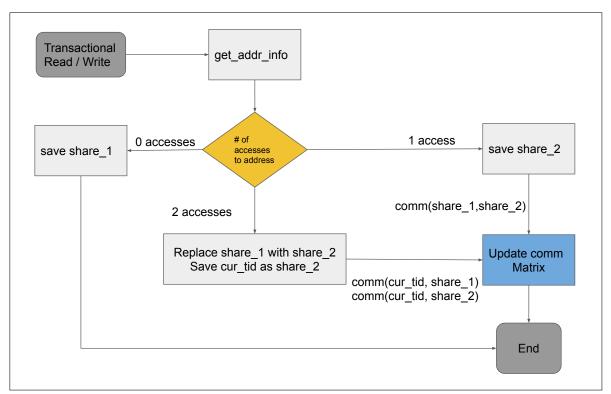

To perform a thread mapping, it is necessary to know how threads share data (DIENER et al., 2016a). This information is usually represented as a *communication matrix* (BORDAGE; JEANNOT, 2018). Also required is information about the hardware hierarchy, which can be discovered using tools such as hwloc (BROQUEDIS et al., 2010a). A mapping algorithm uses the communication matrix and hardware hierarchy to choose an improved mapping of threads to cores.

For data mapping based on memory access, the accesses of each NUMA node to pages must be known (CRUZ; DIENER; NAVAUX, 2018). Current systems have millions or even billions of memory pages. For this reason, only a small group of pages must be considered for the mapping decision, avoiding a high overhead (DIENER et al., 2016a).

As mentioned in Section 1.1, STM provides interesting mapping opportunities since the STM runtime has precise information about memory areas that are shared between threads. The main idea of this thesis is to use information about transactional shared variables inside STM runtime to perform an efficient mapping. Hence, this thesis will focus on sharing-aware **thread mapping**. For efficient data mapping is necessary to have a global vision of the memory pages of an application, not only the ones accessed by the STM runtime. Nevertheless, in Appendix A we made some experiments with sharing-aware data mapping in STM to confirm this hypothesis.

#### 2.3.1 Communication/sharing matrix

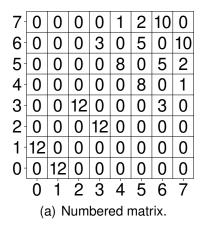

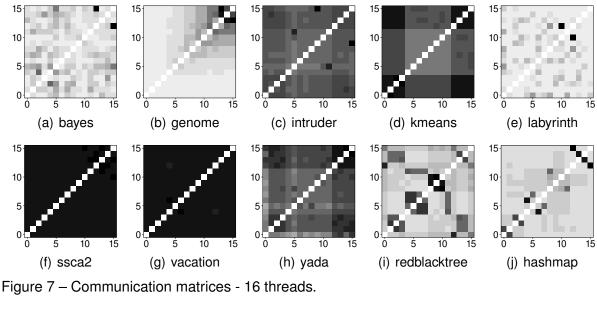

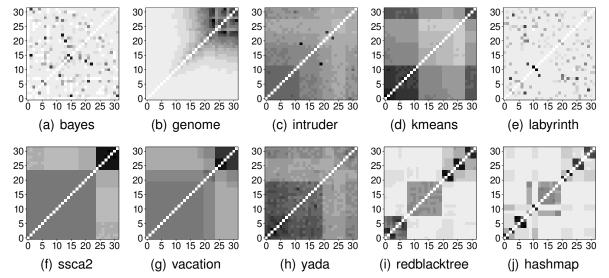

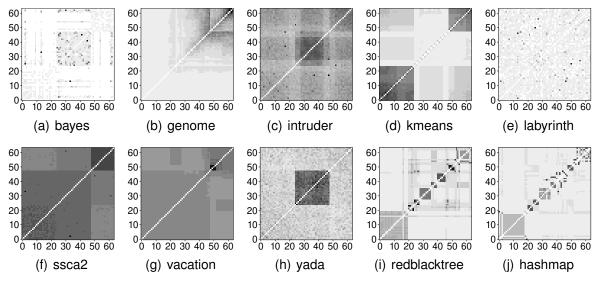

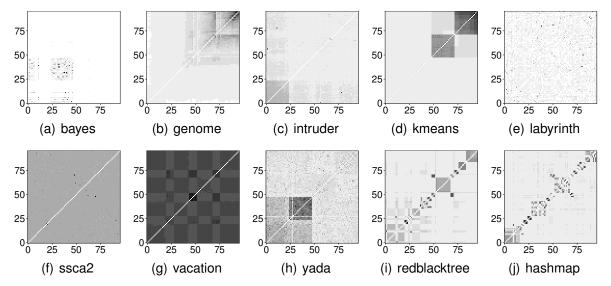

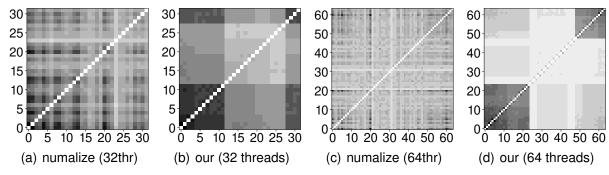

To determine a better placement of threads and data, an affinity measure is required. For thread mapping, a common measure is a communication or sharing matrix (BOR-DAGE; JEANNOT, 2018; MAZAHERI; WOLF; JANNESARI, 2018), in which each cell represents the amount of communication between pairs of threads (SASONGKO et al., 2019). Since the amount of communication between thread i and j is the same between j and i, the communication matrix is symmetric and diagonals are zero (MAZAHERI; WOLF; JANNESARI, 2018). Figure 2 shown examples of communication matrices, where axes show thread IDs. In Figure 2(b), the matrix is represented graphically,

Figure 2 – Examples of communication matrices

where darker cells indicate more communication between pairs of threads (DIENER et al., 2016b).

# 2.4 Improving STM applications with Thread Mapping

To show how sharing-aware thread mapping can improve the performance of an STM application, we designed an experiment that illustrates sharing-aware mapping of an STM application that calculates the sum of 16 million array elements. In the application, each group of 2 threads computes the sum of their respective array part in a shared sum variable. For example, with 8 threads, there are 4 shared variables for computing the sum. The memory access behavior is known in advance: threads 0 and 1 access a shared variable, threads 2 and 3 another shared variable, and so on. Algorithm 1 shows how the sum function works. Lines 5-12 verify the number of

#### Algorithm 1 Function executed by each thread on the array sum application

#### 1: function SUM

#### Require:

tid: thread ID that is accessing this function

```

2:

bind thread to core according to the strategy

pinThreadToCore(tid, coreId)

3:

for all value in array do

4:

stm_start_transaction()

▶ begin transaction

5:

if (tid \text{ in } 0, 1) then

stm write(sum 0 1, stm read(sum 0 1) + stm read(value))

6:

7:

else if (tid \text{ in } 2, 3) then

stm_write(sum_2_3, stm_read(sum_2_3) + stm_read(value))

8:

9:

else if (tid \text{ in } 4, 5) then

stm write(sum 4 5, stm read(sum 4 5) + stm read(value))

10:

else if (tid \text{ in } 6, 7) then

11:

12:

stm_write(sum_6_7, stm_read(sum_6_7) + stm_read(value))

13:

stm commit()

b try to commit

comm

```

the thread that is performing the sum and stores it in the respective shared variable. Thus, keeping threads that share a sum variable on sibling cores improves the cache usage. We used the TinySTM (FELBER et al., 2010) library for the synchronization of shared variables, with the default configuration: *lazy* version management, *eager* conflict detection and CM *suicide*.

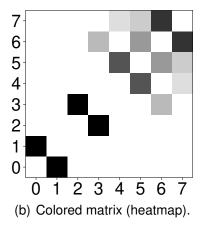

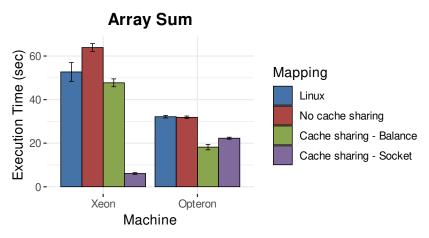

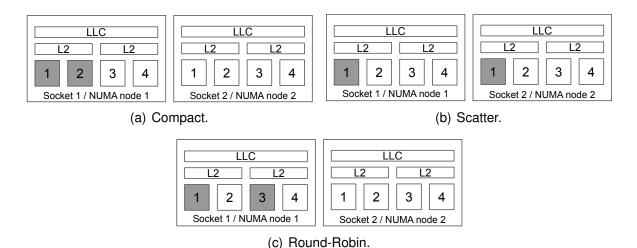

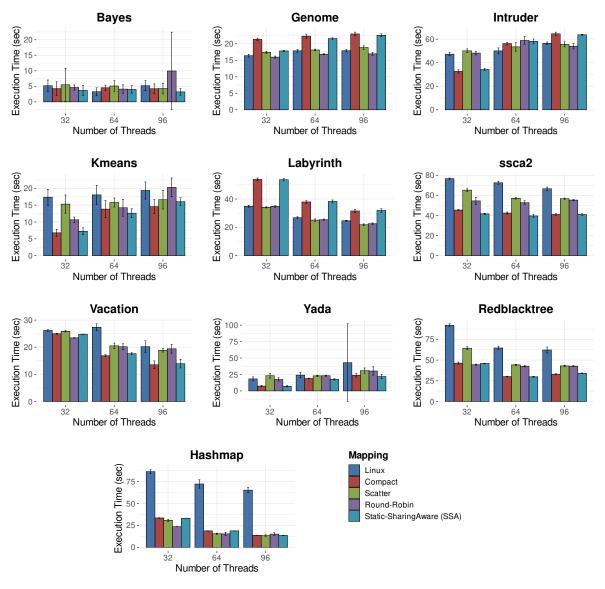

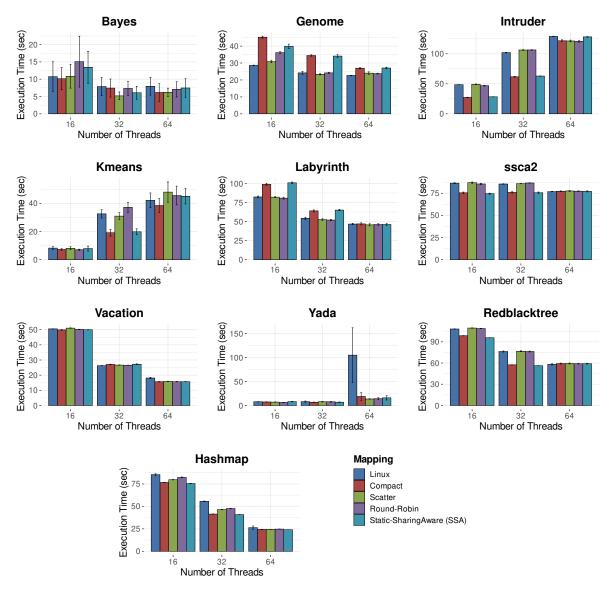

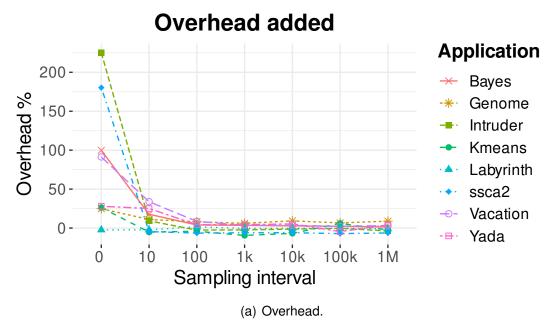

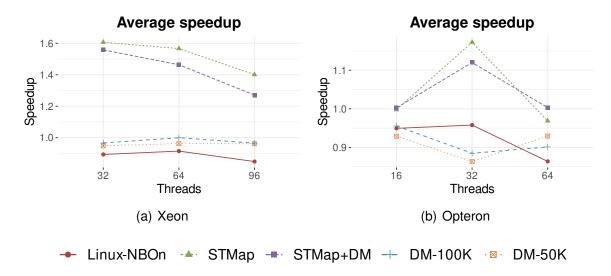

We executed this application on the following NUMA machines: *Xeon*, with 8 Intel E5-4650 processors, totaling 96 cores and 8 NUMA nodes and *Opteron*, with 4 AMD Opteron 6276 processors, totaling 64 threads and also 8 NUMA nodes (more details on the machines in Section 6.1.1). For the tests, 4 different configurations were used: the default "Linux scheduler", "no cache sharing", "Cache sharing - Balance" and "Cache sharing - Socket". With exception of "Linux scheduler", the mapping strategies are shown in Figure 3.

(c) Cache sharing - Socket.

Figure 3 – Thread mapping strategies for the Array Sum application.

The idea of "no cache sharing" is to map threads that share the same variable to different NUMA nodes, forcing remote accesses and cache coherency messages between the nodes. In contrast, in the "Cache sharing - Balance" approach, the idea is to map threads that share a variable to sibling cores on the same NUMA node to share caches. However, for this configuration we map each pair of shared variables to different sockets.

Finally, for "Cache sharing - Socket", the idea is to place threads on sibling cores, sharing all cache levels. Since this application uses 8 threads, using this configuration all threads will be mapped to only one socket. To pin threads to cores the function pthread\_setaffinity\_np was utilized. The mapping was applied when a thread calls the function stm\_init\_thread of the TinySTM library. This function informs the STM runtime that the thread that has called it will perform transactional operations. Figure 4 presents the execution time in seconds on each machine.

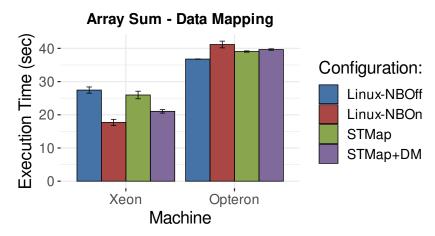

Figure 4 – Execution time of the Array Sum application.

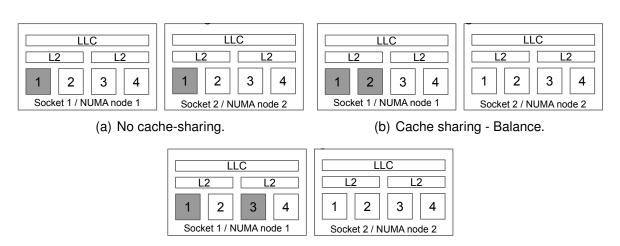

On the Opteron machine, the Linux scheduler had similar results as the "no cache sharing" configuration. When the application was running, we observed that the scheduler tries to balance threads, distributing them to the NUMA nodes, without taking the sharing behavior into account. This explains that the results are similar to "no cache sharing". On Xeon, the NUMA effects are more clear since forcing threads to run on distinct sockets, i.e., "no cache sharing" configuration, presented the worst performance.

For the "Cache sharing - Balance" configuration, on Xeon the execution time was reduced by 9.46% whereas in Opteron it was reduced by 43.02%. However, the most interesting result appears using "Cache sharing - Socket" mapping on the Xeon. Using this configuration, the execution time was reduced by 88.46%. Although in Opteron the result of "Socket" was also positive (30.69% of reduction time), the "Balance" configuration was better. We think that the good results of "Socket" on Xeon can be explained by the size of the last-level cache (LLC). The size of the data structures used by the array sum is 64MB. The size of LLC of the Xeon is 30MB whereas in Opteron it is

6MB. In that case, almost half of the memory used by the application fits entirely on the LLC of the Xeon. For the Opteron, mapping the variables to distinct cores increases the performance gains compared to "Socket" configuration, because more cache was available to the application.

# 2.5 Summary

This chapter presented the background related to this thesis. It also included a small experiment with a synthetic application to illustrate the possible benefits of sharing-aware thread mapping for STM applications.

# 3 RELATED WORK

This chapter presents the works related to the thesis subject. Section 3.1 describes transactional schedulers, one technique used to reduce the number of aborts during transactional execution, hence, improving the performance. Recent works use scheduling techniques for STM with the objective of optimizing resources, like cache and page sharing or to reduce the latency on data access. This kind of schedulers are described in Section (3.2), which presents an exhaustive list of works that uses thread and data mapping to improve the performance of STM applications. The next Section (3.3) also describes works that explore thread and data mapping to improve the performance of applications that do not use STM. To perform a successful mapping it is necessary to perform an in-depth analysis of STM applications, regarding sharing behavior. Hence, Section 3.4 describes works that perform workload characterization of STM applications and sharing behavior of general applications.

#### 3.1 Transactional schedulers

Albeit a Contention Manager (CM) can help to reduce the number of aborts in a transactional execution, it has limitations. The CM acts only in a **reactive** way, dealing with a conflict when it occurs and not avoiding it (YOO; LEE, 2008; DRAGOJEVIĆ et al., 2009; NICÁCIO; BALDASSIN; ARAÚJO, 2012). Transactional scheduling acts in a **proactive** way, using heuristics to prevent conflicts and to decide *when* and *where* a transaction should be executed (DRAGOJEVIĆ et al., 2009).

This section presents state-of-the-art transactional scheduling techniques. In order to identify the works on this subject, the surveys (HENDLER; SUISSA-PELEG, 2015) and (DI SANZO, 2017) were used as a basis. Also, this section describe works published after the surveys. However, transactional schedulers focused on HTM, GPU (Graphics Processing Unit) or real-time systems are not included, because they are not on the scope of this thesis. Di Sanzo (2017) classifies the schedulers as reactive, prediction-driven, feedback-driven (all heuristic based) and machine learning or analytical (based on performance models (TAY, 2018)). In the next sections, we will follow this

classification to describe the transactional schedulers.

#### 3.1.1 Feedback-driven

Feedback techniques are based on constantly comparing if the *actual behavior* of a system is the *desired* (JANERT, 2013). Application parameters are monitored during the execution of a transaction (*actual behavior*), and in each new iteration, they are used as input for the scheduler to take decisions, i.e., a corrective action in order to achieve the *desired behavior*. This step is repeated during execution, trying to dynamically adjust the application (DI SANZO, 2017).

One of the first works to propose a transaction scheduler for STM was the *Adaptive transaction scheduling* (ATS) (YOO; LEE, 2008), and the idea was to work together with the CM: each thread has a *contention intensity* (CI), recalculated each time that a transaction finishes (commit or abort). When the CI is great than a predefined threshold, threads are inserted in a global queue to be serialized. This approach takes into consideration that when the CI is high, it is better to limit parallelism, avoiding possible conflicts.

In Ansari et al. (2008a), an adaptive concurrency control (ACC) technique was proposed which limits the maximum number of concurrent threads executing transactions. The idea is that an excessive number of threads can hurt the performance in a high contention environment, mainly due to a higher number of aborts. The technique keeps track of a *Transaction Commit Ratio* (TCR), i.e., the percentage of committed transactions in the total number of transactions executed, and uses it to dynamically adapt the number of concurrent threads. The ACC uses two parameters: a *target TCR range* and a time *interval* for calculating the TCR. Four adaptive concurrency control algorithms were proposed, varying the heuristic to change the total number of active threads, but all based on TCR.

In Ansari et al. (2008b), the authors proposed a new concurrency control algorithm, called *P-only Concurrency Controller* (PoCC), extending the ACC work. The main idea is to keep TCR at a configurable value (called *set point*) instead of a range as in the previous work. If a high *set point* is chosen, then the number of threads will quickly reduce when TCR decreases. On the other hand, it will have a slower response when TCR grows suddenly.

Chan, Lam and Wang (2011) also propose a new concurrency control technique. For this purpose, a parameter *quota* is recalculated every predetermined amount of time. When a new transaction is to be started, it needs to check if there is sufficient quota available, otherwise, it will wait. There are two proposals for calculating the *quota*. The first one, called *Throttle*, adjusts the quota based on the commit *ratio*, which is compared with a predefined threshold, and the quota is adjusted according to it. The second one, called *Probe*, uses commit *rate* (total of commits per unit of time) instead

of *ratio*. Also, it uses a try and error approach to find the best quota, instead of a fixed threshold.

Ansari (2014) published another work using TCR as the main heuristic. The difference from their first work (ANSARI et al., 2008a) and PoCC is that in this new algorithm, called *Weighted Adaptive Concurrency Control* (WACC), the TCR is calculated per thread. Similar to PoCC, that tried to keep TCR at a configurable value (*set point*), WACC uses the notion of *expected TCR*. It predicts the global TCR that should be achieved if the determined subset of threads is activated. Thus, it is possible to predict if the *set point* will be reached if the determined subset of threads will be allowed to concurrently run. Like in the first work (ANSARI et al., 2008a), four approaches are proposed, using different heuristics (all based on TCR) to define the total number of threads.

One of the main objectives of Rito and Cachopo (2014), is to avoid excessive serialization using a fine-grained approach. They have proposed the ProPS (*Progressively Pessimistic Scheduling*) technique. In ProPS, a global *concurrency level* (CL) matrix keeps information about pairs of atomic operations i and j. For the authors, each transaction that executes the same block of code, execute the same operation of type i. Accessing the matrix on the index  $CL_{ij}$ , it is possible to know how many transactions executing atomic operations of type i could be executed concurrently with another one executing j atomic operations. In the beginning, the values in the matrix are set to be equal to the maximum of threads or cores of the machine, i.e., all cores could execute all types of transactions without restriction. When a specific  $CL_{ij}$  decreases (typically by an abort of i or j), ProPS reduces the number of transactions executing i and j. By design, ProPS reduces exponentially (*progressively pessimistic*) the concurrency on aborts between atomic operations and increases it linearly at commit.

The idea proposed by Pereira, Amaral and Araújo (2014) is to use the *percentage of effective work* (PEW) of a transaction as the main heuristic. The PEW replaces CI in approaches like ATS. It is calculated for each transaction, and it is based on the total of cycles executed until the transaction finishes (commit or abort). Transactions with less effective work done are prioritized. If a transaction aborts and the PEW is high, then it is wasting too many work (cycles) and should have a lower priority. There are queues of transactions according to their priorities. The authors noted that only using PEW, there is still a high number of conflicts between transactions with the same priority. Thus, an additional heuristic was included: a *success-reward policy* (SRP). According to a predefined *reward* threshold, a transaction could change its position in the queue.

In Ravichandran and Pande (2014), the authors classified applications as *fully scalable* and *scalability limited*. Applications under the former classification decrease their execution time as the number of cores of the machine grows. The latter is the opposite, hurting the application performance as the number of cores is increased. The authors have proposed F2C2-STM (Flux-based Feedback-driven Concurrency Control), which

focuses on *scalability limited* applications. F2C2-STM is inspired by TCP's (Transmission Control Protocol) network congestion control algorithm, to adjust the maximum number of concurrent threads allowed to run. The heuristic utilized is the transaction throughput. However, to compute the global throughput between all threads, a global variable is needed. To avoid synchronization, the authors chose to calculate the throughput only in one thread. Thus, they have assumed that the transactional workload is roughly the same between all threads. To find the best concurrency level, like in Chan, Lam and Wang (2011), they have used a try and error approach, monitoring the transaction throughput on each modification.

#### 3.1.2 Reactive

Reactive techniques are activated after a conflict is detected. The main objective is to avoid the same conflict to occur again (DI SANZO, 2017).

The Collision Avoidance and Resolution (CAR-STM) scheduling-based mechanism (DOLEV; HENDLER; SUISSA, 2008) presents two new CMs and a scheduler. Each core has one queue, and the runtime system restricts the maximum number of threads to be equals to the cores available. The first CM proposed is called Basic. When it detects a conflict between two transactions, it aborts the newer transaction and move it to the queue of the older. The second, called Permanent, also aborts the newer transaction in case of conflicts. However, it marks the aborted as a subordinate of the older. If a transaction needs to be moved to another queue, Permanent will also move all its subordinates. A proactive centralized module tries to choose the queue for a new transaction, based on a conflict probability with the running transactions on each queue.

On Steal-on-Abort (SoA) (ANSARI et al., 2009), the idea is to find dynamically an optimal order to execute transactions, minimizing aborts. Each thread has two queues. The first one, called main queue, keeps new transactions that should be processed by the thread. The second queue is called "steal". When a transaction aborts due to a conflict, instead of restarting immediately, the opponent transaction "steals" the aborted one and put in the steal queue of the thread. When the opponent transaction commits, transactions on the steal queue are moved to the main queue. The authors proposed different strategies to choose in what position of the queue the stolen transaction will be put in. According to the authors, SoA benefits applications that have a high number of repeated conflicts.

In Attiya and Milani (2009, 2012), the focus of the proposed schedulers are workloads with read-dominated transactions and lazy versioning. The authors explain that many proposed schedulers focuses on avoiding repeated conflicts, serializing transactions. Also, they do not perform well under read-dominated workloads, serializing more transactions than necessary. With this motivation, the BIMODAL scheduler is proposed.

On BIMODAL, each core has a work queue. Also, a global *RO-queue*, for read-only transactions is shared between all cores. When two transactions conflict, if the aborted is a writing one, it will be moved to the same queue of the conflicting. If it is read-only, it will be moved to the RO-queue. When the RO-queue reaches a threshold of enqueued transactions (or the other queues are empty), the BIMODAL will prioritize the transactions in the RO-queue. The scheduler is proposed in a theoretical way. It was formally proved and compared with SoA.

Sharp and Morgan (2013) argue that prior transactional schedulers deal with concurrent conflicts only, i.e., between a reader and a writer. The objective of the authors is to deal with *semantic conflicts*. This kind of conflict occurs when there is no concurrent conflict and yet it is not possible for transactions to proceed. They have cited as an example a transaction that needs to consume an item from a buffer but the buffer is empty, or a withdraw in an account without funds. With this motivation the Hugh scheduler is proposed. When a transaction aborts, it first needs to register itself in a *transaction table*. Next, a speculative phase begins, executing a permutation of transactions that is in the *transaction table*. This phase tries to find a permutation where the maximum of pending transactions can commit. Finally, in the commit phase, all successful permutations are sent to an algorithm to decide which permutation can commit. It chooses the permutation with the greatest number of transactions. The authors also proposed Hugh2 (SHARP; BLEWITT; MORGAN, 2014), using the same idea on a different STM implementation.