**UNIVERSIDADE FEDERAL DE PELOTAS**

**Centro de Desenvolvimento Tecnológico**

Programa de Pós-Graduação em Computação

**Dissertação**

**Energy/Quality-Aware Hardware Solutions for the Residual Coding Loop

Components of the High Efficiency Video Coding Standard**

**Luciano Almeida Braatz**

**Pelotas, 2018**

**Luciano Almeida Braatz**

**Energy/Quality-Aware Hardware Solutions for the Residual Coding Loop

Components of the High Efficiency Video Coding Standard**

Dissertação apresentada ao Programa

de Pós-Graduação em Computação da

Universidade Federal de Pelotas, como

requisito parcial à obtenção do título de

Mestre em Ciência da Computação

Advisor: Prof. Dr. Marcelo Schiavon Porto

Coadvisors: Prof. Dr. Daniel Munari Palomino

Prof. Dr. Luciano Volcan Agostini

Pelotas, 2018

Universidade Federal de Pelotas / Sistema de Bibliotecas

Catalogação na Publicação

B794e Braatz, Luciano Almeida

Energy/quality-aware hardware solutions for the residual coding loop components of the high efficiency video coding standard / Luciano Almeida Braatz ; Marcelo Schiavon Porto, orientador ; Daniel Munari Palomino, Luciano Volcan Agostini, coorientadores. — Pelotas, 2018.

111 f.

Dissertação (Mestrado) — Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, 2018.

1. Video coding. 2. HEVC. 3. Residual coding loop. 4. Hardware design. 5. Energy/quality awareness. I. Porto, Marcelo Schiavon, orient. II. Palomino, Daniel Munari, coorient. III. Agostini, Luciano Volcan, coorient. IV. Título.

CDD : 005

## **AGRADECIMENTOS**

Aos meus pais, Nelson e Mariza, pelo apoio e por sempre acreditarem no meu sucesso.

Aos familiares e amigos, pela compreensão da ausência durante esta jornada.

Aos professores Marcelo Porto, Daniel Palomino, Luciano Agostini e Bruno Zatt pelo auxílio na idealização do tema, sua orientação, paciência e apoio.

Aos colegas do Grupo de Arquiteturas e Circuitos Integrados pela parceria e ajuda no desenvolvimento deste projeto.

*Theorie ohne Praktik ist verwirrt;

Praktik ohne Theorie ist unzulänglich.*

— G. J. VOGLER

## ABSTRACT

BRAATZ, Luciano Almeida. **Energy/Quality-Aware Hardware Solutions for the Residual Coding Loop Components of the High Efficiency Video Coding Standard.** 2018. 111 f. Dissertação (Mestrado em Ciência da Computação) – Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, Pelotas, 2018.

Multimedia applications, such as digital videos, are very popular nowadays, especially on mobile devices. Moreover, there is an expectation of continuous growth of the Internet-based digital videos traffic throughout the next years. Video coders, e.g. the High Efficiency Video Coding (HEVC), are very important in this context as the video coders can rationalize Internet resources by reducing the amount of video-related data flowing through the network. Unfortunately, this data reduction requires a huge computational effort. Thus, hardware accelerators can be used as a feasible solution, providing high-throughput on low-power. The HEVC residual coding loop (RCL), composed of direct transform, direct quantization, inverse quantization, and inverse transform, is a highly-requested stage of video coding standards since it is used multiple times to test several coding modes (CMs). Therefore, the objective of this work is to provide multiple energy/quality-aware dedicated hardware solutions to increase throughput for the components of RCL in HEVC, allowing real time processing of many CM by the RCL. Thus, the HEVC encoder using the presented solutions is expected to be more coding efficient than the ones using the solution proposed by the existing related works. Innovative solutions are proposed in this work to increase throughput, which has direct impact on the coding efficiency in the RCL components, with low power dissipation. A direct DCT was proposed based on the Fast Fourier Transform (FFT), which allows an intensive hardware reuse, and energy-consumption reduction, able to operate up to 2.54 GHz while dissipating 12.33 mW of power; an energy/quality scalable inverse DCT is presented using a bypass engine based on statistical analysis, setting a trade-off between coding-efficiency and energy-efficiency, which operates up to 737.46 MHz and dissipates between 13.87 mW and 16.84 mW; and a project space exploration of quantization architectures is also presented, with power dissipation of 152.13 mW and 31.15 mW at 888.10 MHz and 1.36 GHz, respectively, including an integrated direct/inverse quantization, which reduces the number of arithmetical operations by integrating direct quantization and inverse quantization, dissipating 369.37 mW at 1.68 GHz. The developed hardware architectures are able to process up to 108, 32, 38, 58, and 72 CM of UHD 4K videos at 60fps for the DCT, IDCT, direct quantization, inverse quantization, and integrated direct/inverse quantization hardware architectures, respectively. When compared with

related works, the developed RCL components hardware architectures can operate on higher frequencies, present higher throughputs, and are more energy efficient.

**Keywords:** video coding; hevc; residual coding loop; hardware design; energy/quality awareness

## RESUMO

BRAATZ, Luciano Almeida. **Soluções em Hardware com Foco em Aumento da Qualidade e Economia de Energia para os Componentes do Laço de Codificação Residual do Padrão HEVC**. 2018. 111 f. Dissertação (Mestrado em Ciência da Computação) – Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, Pelotas, 2018.

Aplicações multimídia, como vídeos digitais, são muito populares hoje em dia, especialmente em dispositivos móveis. Além disso, há uma expectativa de crescimento contínuo do tráfego de vídeos digitais baseados na Internet nos próximos anos. Codificadores de vídeo, como o HEVC (do inglês *High-Efficiency Video Coding*), são muito importantes neste contexto, pois os codificadores de vídeo podem racionalizar os recursos da Internet reduzindo o tráfego de dados relacionados a vídeos na rede. Infelizmente, essa redução no volume de dados requer um enorme esforço computacional. Assim, o uso de aceleradores de hardware se apresenta como uma solução viável, pela sua capacidade de apresentar alto *throughput* e baixo consumo energético. O laço de codificação residual do HEVC (RCL, do inglês *Residual Coding Loop*), composto por transformada direta, quantificação direta, quantização inversa e transformada inversa, é um estágio altamente solicitado de padrões de codificação de vídeo, pois é usado para testar vários modos de codificação. Portanto, o objetivo deste trabalho é fornecer soluções de hardware dedicadas com foco em eficiência energética e no aumento do *throughput* dos componentes do RCL no HEVC, permitindo que os componentes do RCL possam processar diversos modos de codificação em tempo real. Assim, o codificador HEVC que usa as soluções apresentadas deverá ser mais eficiente em termos de codificação do que os que usam as soluções propostas pelos trabalhos relacionados existentes. Este trabalho propõe soluções inovadoras para aumentar o *throughput* dos componentes do RCL, com impacto direto na eficiência de codificação e baixa dissipação de energia. A DCT, proposta com base na Transformada Rápida de Fourier (FFT, do inglês *Fast Fourier Transform*), permite a reutilização intensiva de hardware e redução de consumo de energia, sendo capaz de operar a até 2,54 GHz enquanto dissipá 12,33 mW de potência; uma IDCT com compromisso entre energia e qualidade é apresentada usando um mecanismo de *bypass* com base em análise estatística, estabelecendo um compromisso entre eficiência de codificação e eficiência energética, opera até 737,46 MHz e dissipá entre 13,87 mW e 16,84 mW; uma exploração do espaço de projeto de arquiteturas de quantização também é apresentada, com uma dissipação de potência entre 152,13 mW e 31,15 mW a 888,10 Mhz e 1,36 GHz, respectivamente; um módulo integrado de quantização direta e in-

versa que reduz o número de operações aritméticas integrando quantização direta e quantificação inversa, dissipando 369,37 mW a 1,68 GHz. As arquiteturas de hardware desenvolvidas são capazes de processar até 108, 32, 38, 58 e 72 modos de codificação de vídeos UHD 4K a 60fps para DCT, IDCT, quantização direta, quantização inversa e a arquitetura integrada de quantização direta e inversa, respectivamente. Comparado aos trabalhos relacionados, as arquiteturas de hardware dedicadas para os componentes da RCL operam com frequências mais altas, apresentam throughputs maiores e são mais eficientes energeticamente.

**Palavras-Chave:** codificação de vídeo; hevc; laço de codificação residual; projeto de hardware; foco em qualidade e energia

## LIST OF FIGURES

|           |                                                                                                                                                                           |    |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 1  | HEVC encoder data flow                                                                                                                                                    | 23 |

| Figure 2  | Quadtree partitioning example                                                                                                                                             | 25 |

| Figure 3  | CU partitioning applied to a frame in the BasketballDrill video (ZHOU; ZHOU; CHEN, 2013)                                                                                  | 26 |

| Figure 4  | PU formats allowed in HEVC                                                                                                                                                | 26 |

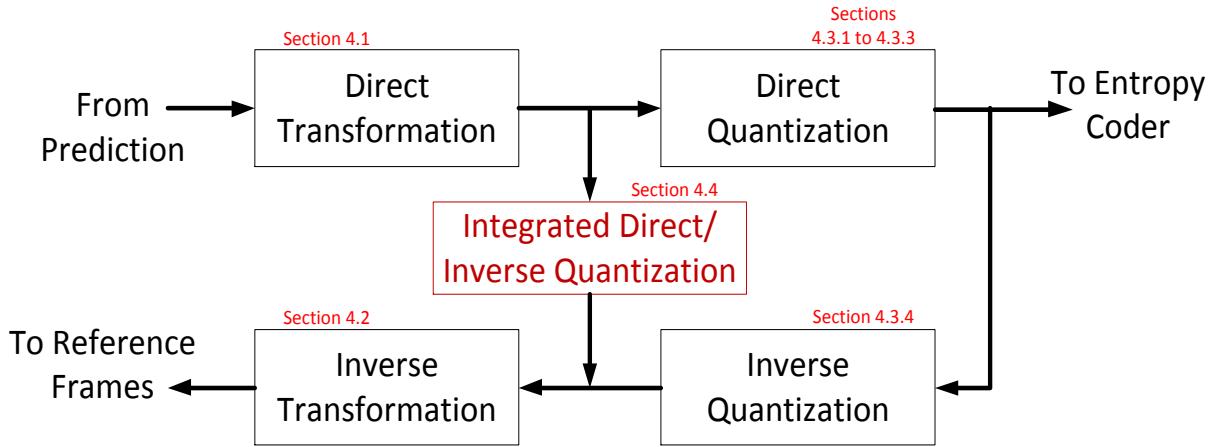

| Figure 5  | RCL block diagram                                                                                                                                                         | 27 |

| Figure 6  | Example of RCL operation                                                                                                                                                  | 28 |

| Figure 7  | 4-point 1D-DCT block diagram                                                                                                                                              | 32 |

| Figure 8  | Difference between DCT and IDCT. (a) EOD algorithm. (b) Processing order.                                                                                                 | 33 |

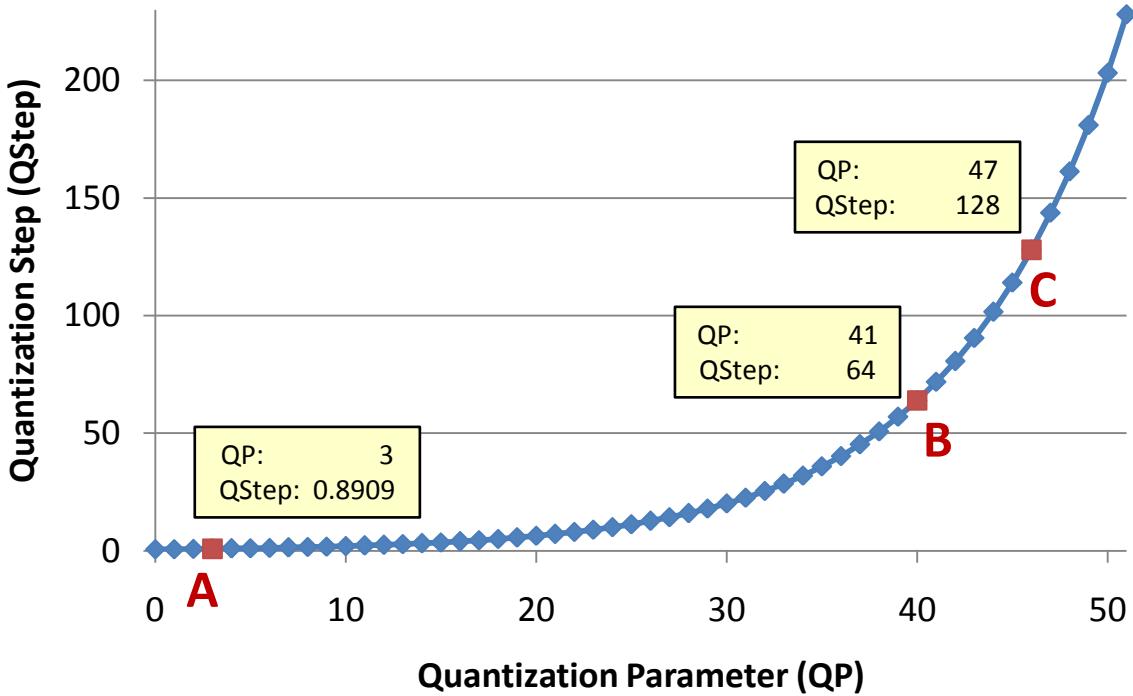

| Figure 9  | Quantization step value according to QP value                                                                                                                             | 35 |

| Figure 10 | Relationship between different QM sizes                                                                                                                                   | 36 |

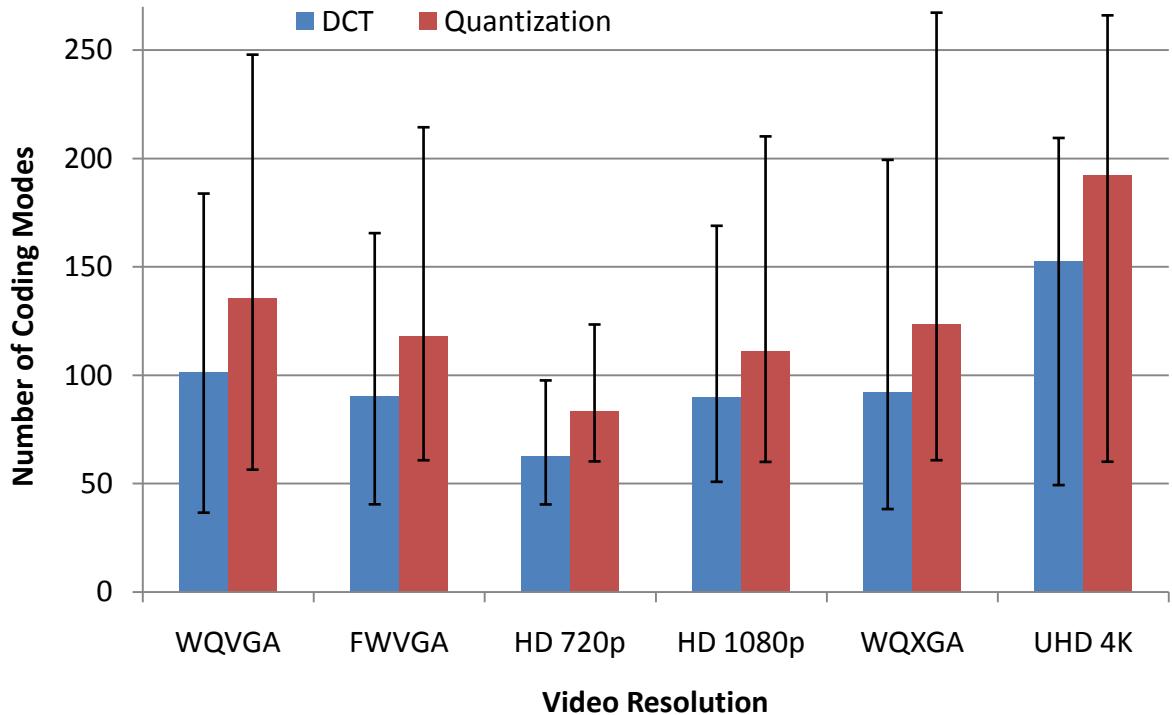

| Figure 11 | Number of CM processed by RCL components, grouped by resolutions                                                                                                          | 44 |

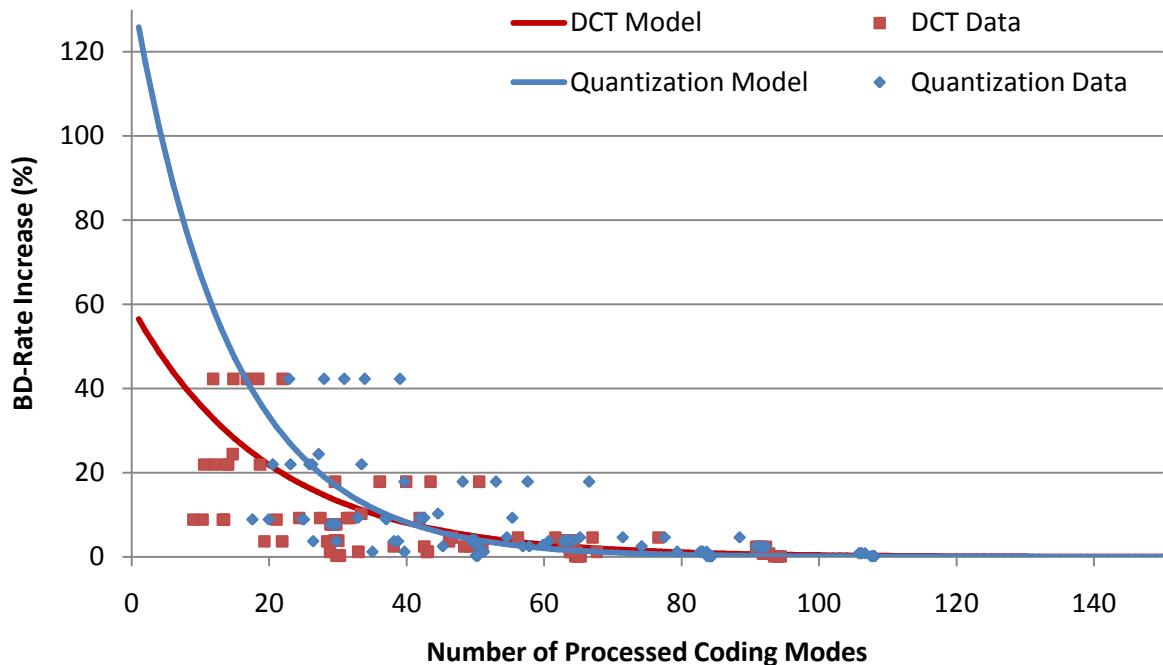

| Figure 12 | BD-Rate impact tendencies according to the LCR components processing rates                                                                                                | 48 |

| Figure 13 | RCL diagram block                                                                                                                                                         | 54 |

| Figure 14 | A 32-point real DFT block diagram, using radix-2 DIT FFT                                                                                                                  | 56 |

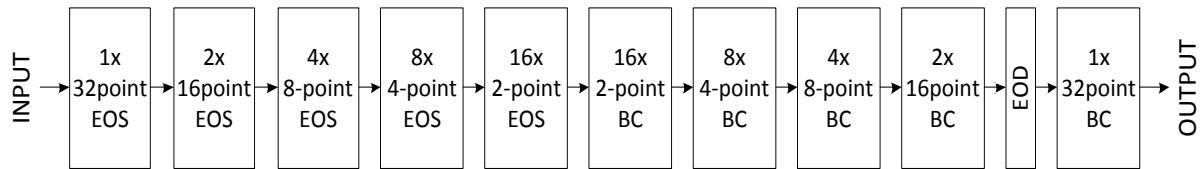

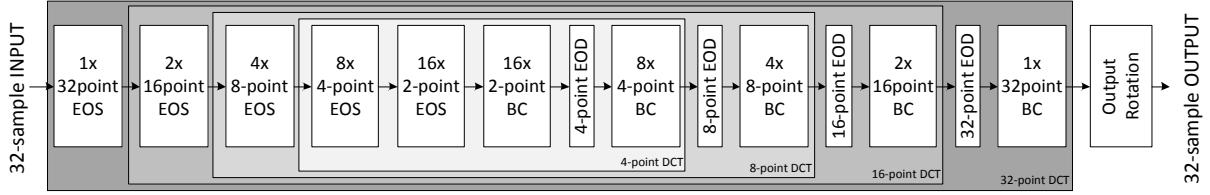

| Figure 15 | Proposed DCT block diagram                                                                                                                                                | 57 |

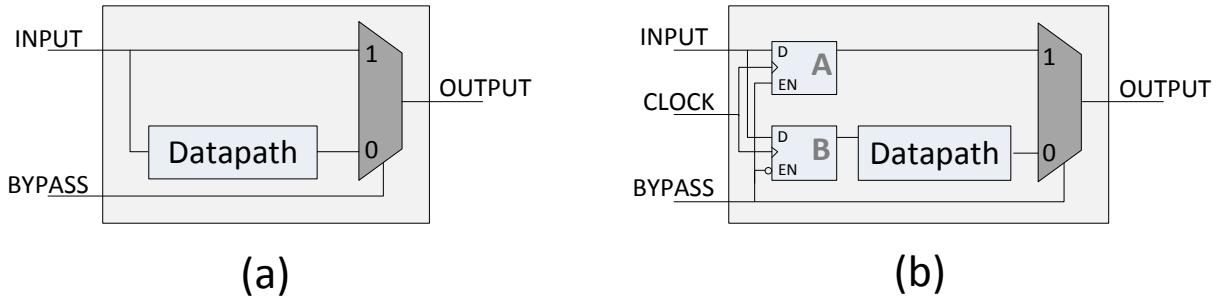

| Figure 16 | Bypass approaches. (a) Simple-multiplexed bypass (b) Clock-gated bypass                                                                                                   | 58 |

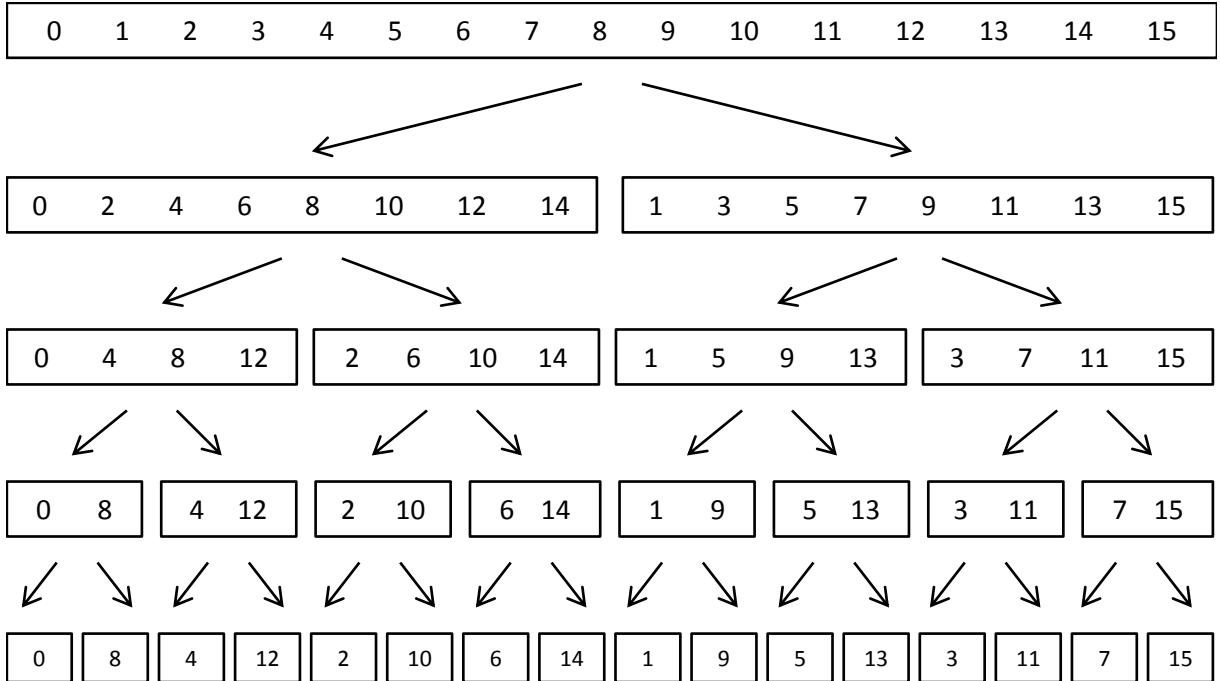

| Figure 17 | Recursive 16-point even/odd separation (SMITH, 1997)                                                                                                                      | 59 |

| Figure 18 | BC blocks interposition according to the BC size                                                                                                                          | 59 |

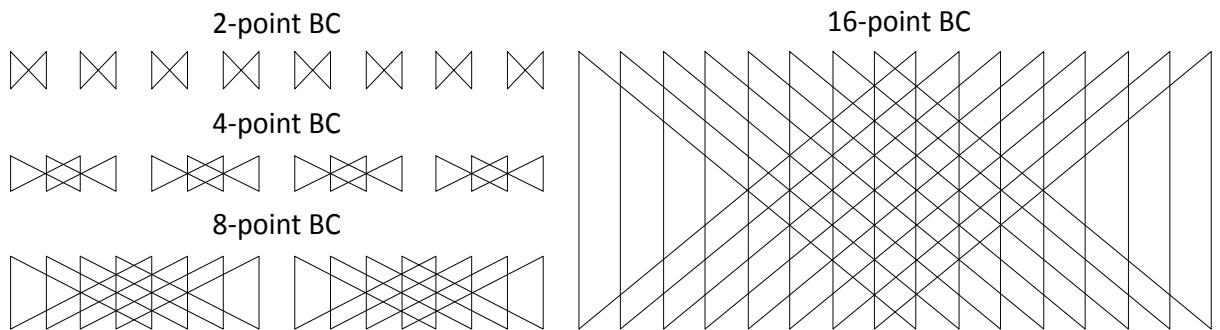

| Figure 19 | Proposed DCT sub block data flow. (a) BC block. (b) EOD block. (c) Output rotation block.                                                                                 | 60 |

| Figure 20 | Regular 1D-IDCT block diagram                                                                                                                                             | 61 |

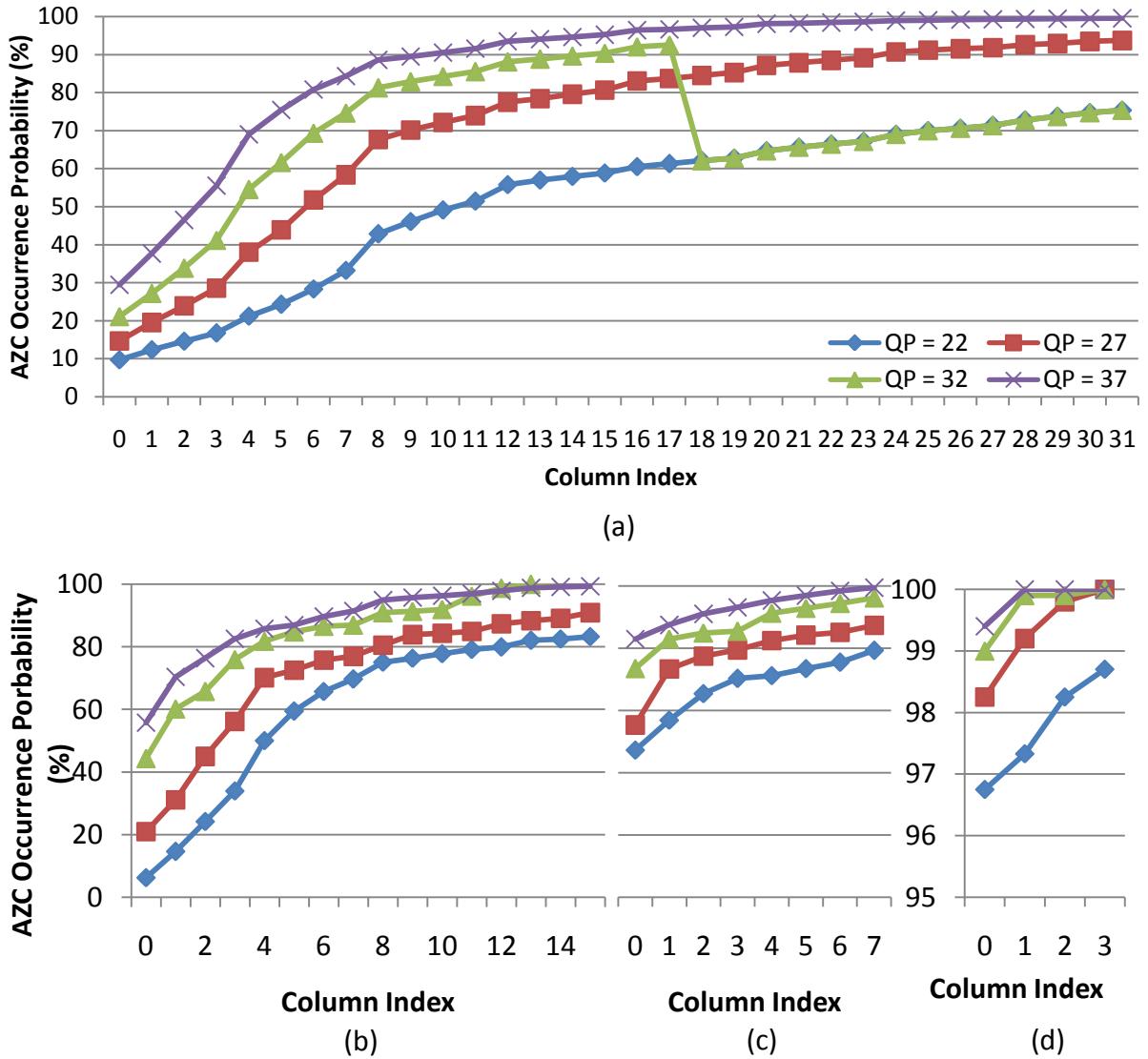

| Figure 21 | AZC occurrence probability, grouped by QP and column index. (a) 32-point first 1D-IDCT. (b) 16-point first 1D-IDCT. (c) 8-point first 1D-IDCT. (d) 4-point first 1D-IDCT. | 65 |

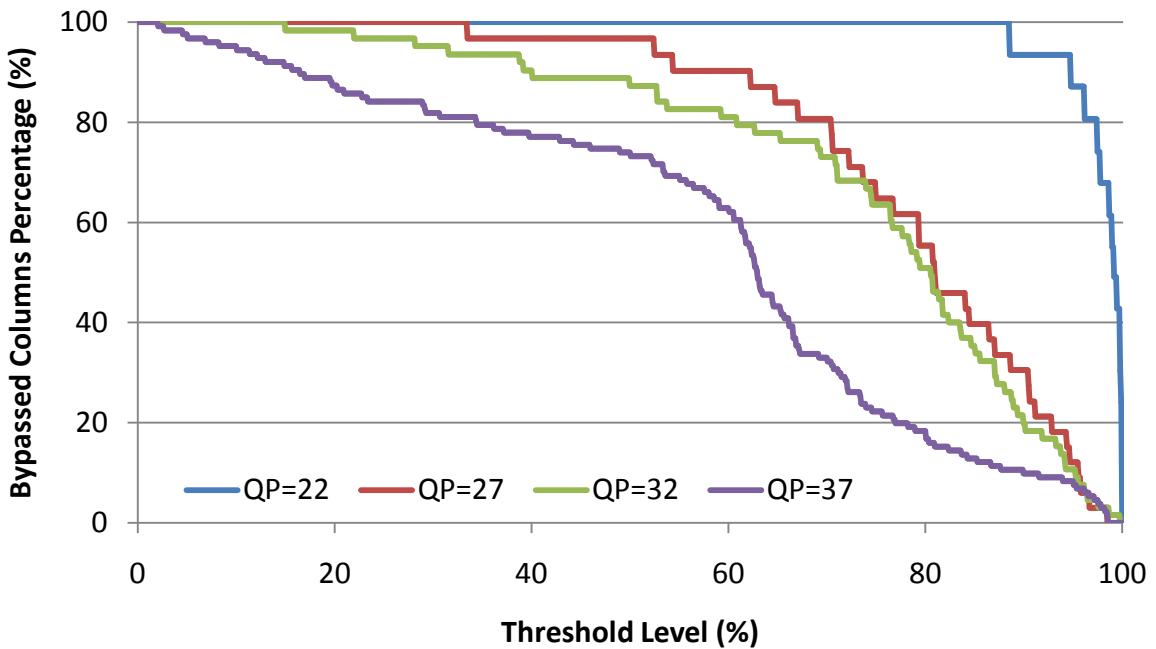

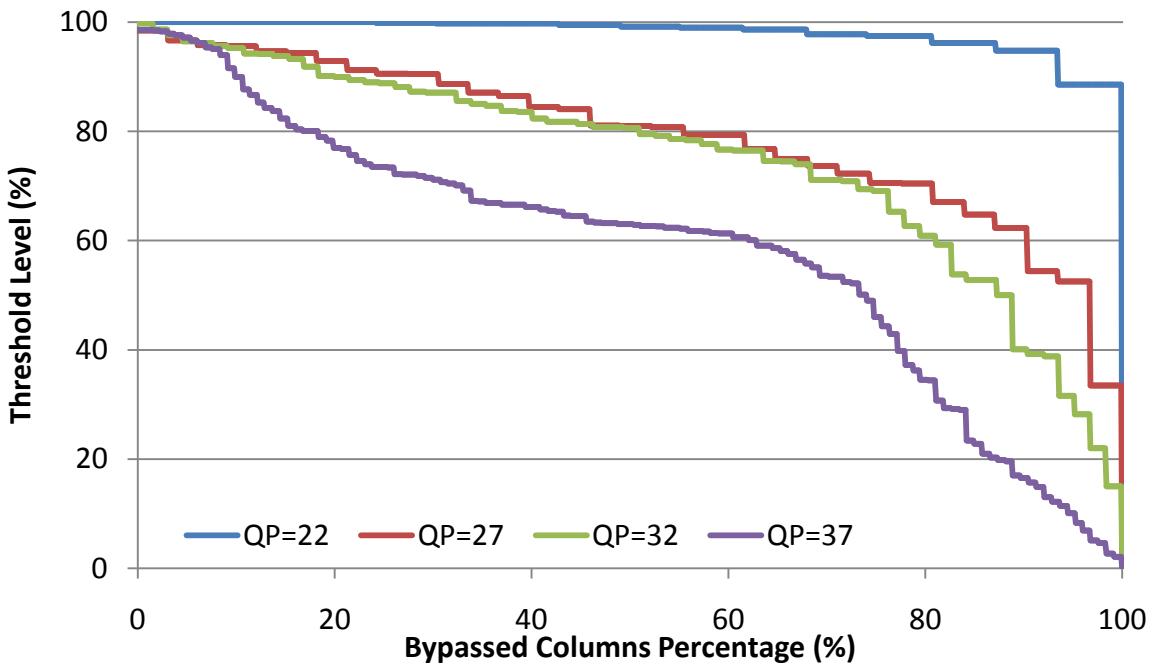

| Figure 22 | BCP data as a function of the threshold level and the QP value                                                                                                            | 66 |

| Figure 23 | Threshold level as a function of BCP and QP values                                                                                                                        | 67 |

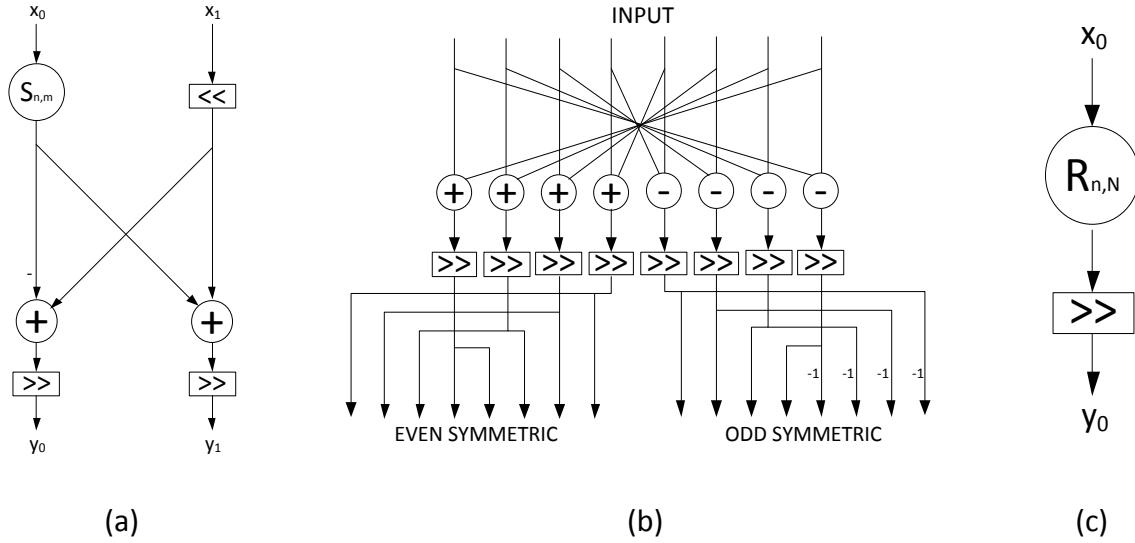

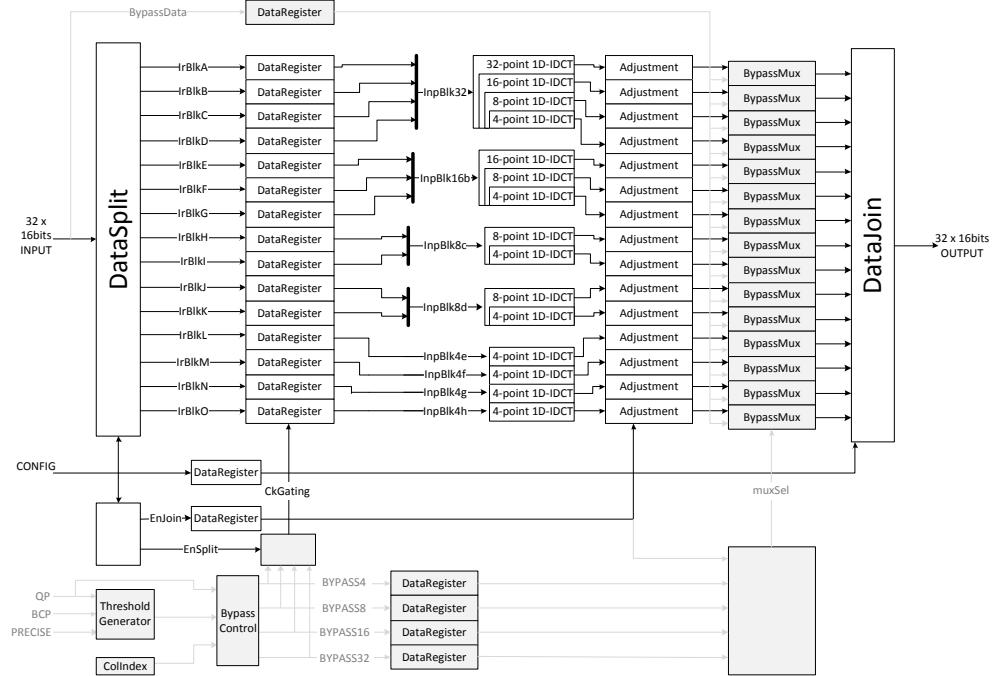

| Figure 24 | Bypass controlled approximated 1D-IDCT architecture                                                                                                                       | 69 |

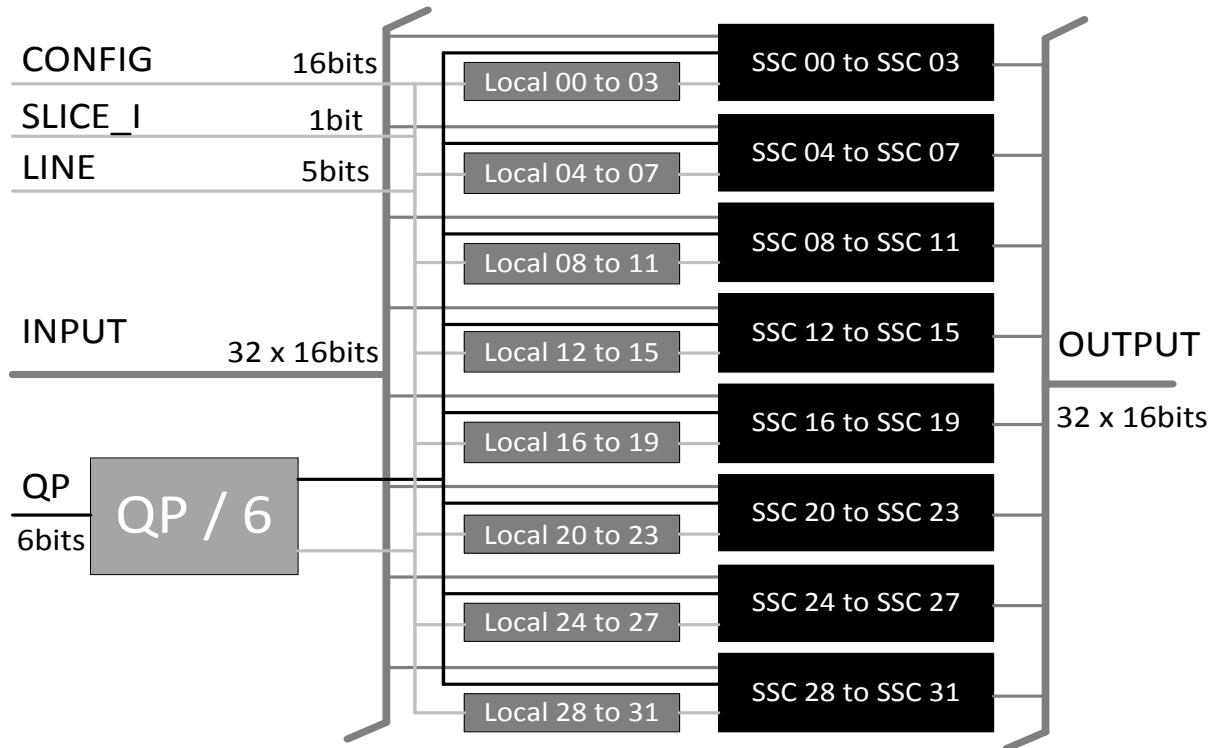

| Figure 25 | Top-level block diagram of generic parallel quantization component                                                                                                        | 71 |

| Figure 26 | Local block diagram                                                                                                                                                       | 71 |

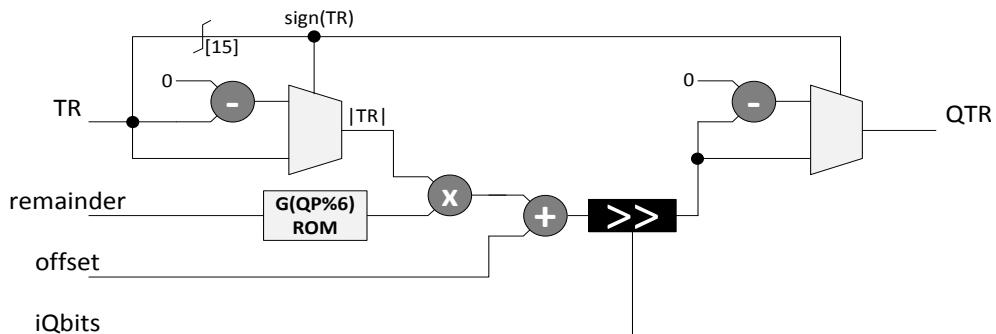

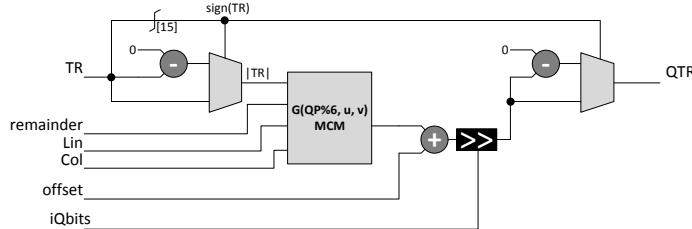

| Figure 27 | DQ-SSC with flat-quantization using MCM                                                                                                                                   | 72 |

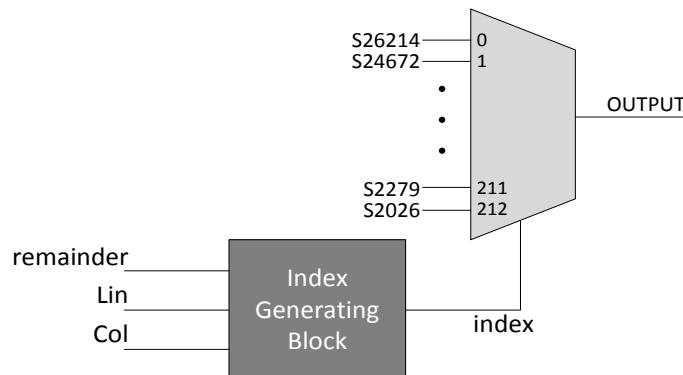

| Figure 28 | Block diagram of MCM block for DQ-SSC with flat quantization                                                                                                              | 72 |

| Figure 29 | DQ-SSC with flat-quantization and generic multiplier usage                                                                                                                | 73 |

|           |                                                                         |    |

|-----------|-------------------------------------------------------------------------|----|

| Figure 30 | DQ-SSC with FDQ support using generic multiplier . . . . .              | 74 |

| Figure 31 | Two-step selection structure for the FDQ-supporting MCM block . . . . . | 74 |

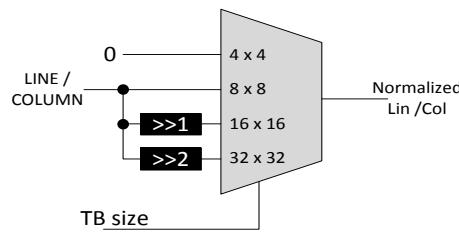

| Figure 32 | Lin/Col value normalization . . . . .                                   | 75 |

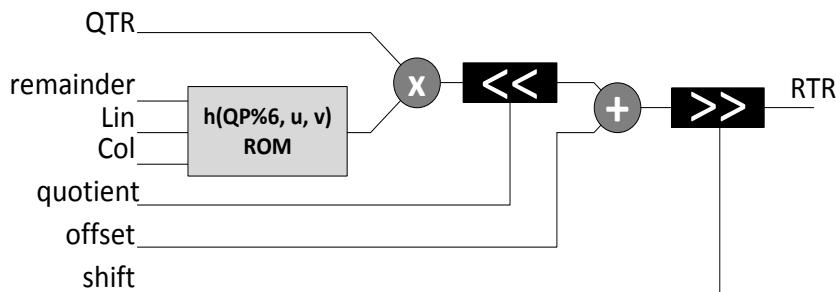

| Figure 33 | IQ-SSC with FDQ support using generic multiplier . . . . .              | 75 |

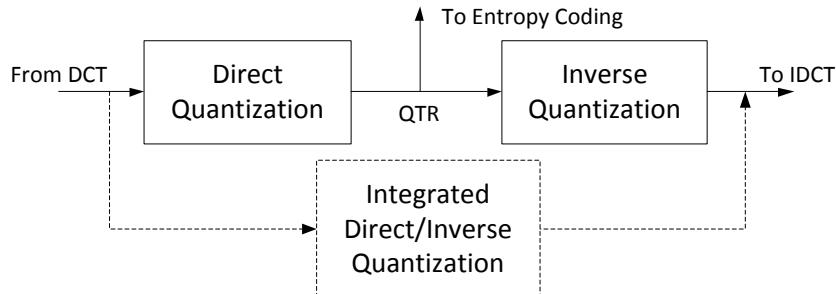

| Figure 34 | Integrated Direct/Inverse Quantization placement . . . . .              | 77 |

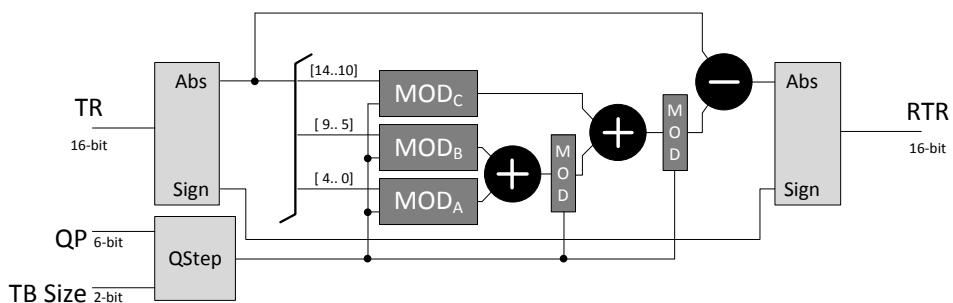

| Figure 35 | IDIQ SSC block diagram . . . . .                                        | 78 |

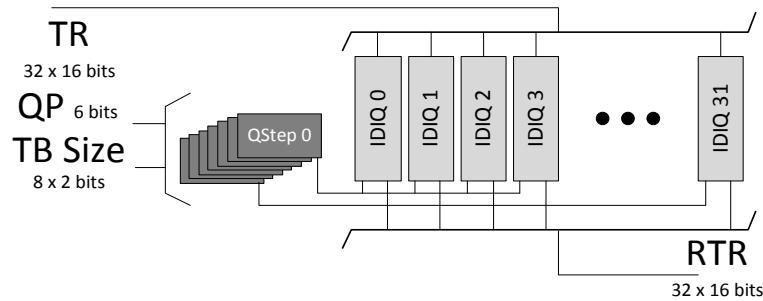

| Figure 36 | PIDIQ architecture block diagram . . . . .                              | 79 |

## LIST OF TABLES

|          |                                                                                                                             |    |

|----------|-----------------------------------------------------------------------------------------------------------------------------|----|

| Table 1  | Arithmetical operations performed by 2D-DCT (JESKE, 2013) . . . . .                                                         | 30 |

| Table 2  | Offset and shift parameters for different sized 1D-DCT (JESKE, 2013) . . . . .                                              | 32 |

| Table 3  | CTC Video Sequences (BOSSEN, 2013) . . . . .                                                                                | 38 |

| Table 4  | Number of coding modes processed by RCL components, grouped by QP value . . . . .                                           | 41 |

| Table 5  | Number of coding modes processed by RCL components, grouped by video and video resolution . . . . .                         | 42 |

| Table 6  | Number of coding modes processed by RCL components, grouped by video resolution . . . . .                                   | 43 |

| Table 7  | Number of coding modes processed by RCL components, grouped by configuration profile . . . . .                              | 43 |

| Table 8  | Minimum frequency for the DCT and quantization hardware modules, in GHz . . . . .                                           | 45 |

| Table 9  | Impact of reducing the TB size range on BD-Rate, number of processed coding modes of the DCT and the quantization . . . . . | 47 |

| Table 10 | Related works estimated impact on BD-Rate due to processing rate limitations . . . . .                                      | 49 |

| Table 11 | FDQ usage impact on BD-Rate (in %), grouped by video resolution . . . . .                                                   | 51 |

| Table 12 | FDQ usage impact on BD-Rate (in %), grouped by configuration profile . . . . .                                              | 51 |

| Table 13 | Encoded TB size pattern . . . . .                                                                                           | 61 |

| Table 14 | Impact of bypass usage on coding efficiency . . . . .                                                                       | 68 |

| Table 15 | $G(QP\%6)$ constants to be implemented in MCM . . . . .                                                                     | 73 |

| Table 16 | Synthesis Results for FFT-inspired HEVC 1D-DCT . . . . .                                                                    | 81 |

| Table 17 | Comparison of FFT-inspired HEVC 1D-DCT hardware architecture with related works . . . . .                                   | 82 |

| Table 18 | BD-Rate impact of throughput limitation of works listed in Table 17 . . . . .                                               | 85 |

| Table 19 | Synthesis Results for Regular and EQS 1D-IDCT . . . . .                                                                     | 86 |

| Table 20 | Comparison of the regular and EQS 1D-IDCT with related work . . . . .                                                       | 87 |

| Table 21 | BD-Rate impact of throughput limitation of works listed in Table 20 . . . . .                                               | 87 |

| Table 22 | Synthesis results of the direct quantization hardware design space exploration . . . . .                                    | 88 |

| Table 23 | Comparison of the flat/MCM DQ-SSC with related work (DIAS; ROMA; SOUSA, 2015) . . . . .                                     | 89 |

| Table 24 | Synthesis results of the inverse quantization hardware design space exploration . . . . .                                   | 90 |

|          |                                                                                                     |    |

|----------|-----------------------------------------------------------------------------------------------------|----|

| Table 25 | Comparison of the flat/GM IQ-SSC with related work (DIAS; ROMA; SOUSA, 2015) . . . . .              | 90 |

| Table 26 | IDIQ and PIDIQ syntheses results . . . . .                                                          | 91 |

| Table 27 | Comparison of the IDIQ hardware architectures with related work (DIAS; ROMA; SOUSA, 2015) . . . . . | 91 |

## LIST OF ABBREVIATIONS AND ACRONYMS

|         |                                                   |

|---------|---------------------------------------------------|

| 1D-DCT  | One-dimensional Discrete Cosine Transform         |

| 1D-IDCT | One-dimensional Inverse Discrete Cosine Transform |

| 2D-DCT  | Two-dimensional Discrete Cosine Transform         |

| AZC     | Almost Zeroed Column                              |

| BCP     | Bypassed Columns Percentage                       |

| BC      | Butterfly Cluster                                 |

| BD-Rate | Bjøntegåard Distance on Bit Rate                  |

| BD-BR   | BD-Rate                                           |

| BRO     | Bit-Reversal Ordering                             |

| CB      | Coding Block                                      |

| CM      | Coding Mode                                       |

| #CM     | Number of Coding Modes                            |

| CPU     | Central Processing Unit                           |

| CTB     | Coding Tree Block                                 |

| CTC     | Common Test Conditions                            |

| CTU     | Coding Tree Unit                                  |

| CU      | Coding Unit                                       |

| DCT     | Discrete Cosine Transform                         |

| DFT     | Discrete Fourier Transform                        |

| DIT     | Decimation-in-time                                |

| DQ-SSC  | Direct Quantization Single-Sample Core            |

| DSP     | Digital Signal Processor                          |

| DST     | Discrete Sine Transform                           |

| EOD     | Even/Odd Decomposition                            |

| EOS     | Even/Odd Separation                               |

| eps     | Energy per Sample                                 |

|        |                                                                         |

|--------|-------------------------------------------------------------------------|

| EQS    | Energy/Quality Scalable                                                 |

| FDQ    | Frequency-Dependent Quantization                                        |

| FFT    | Fast Fourier Transform                                                  |

| FPGA   | Field Programmable Gate Array                                           |

| fps    | Frames per Second                                                       |

| FWVGA  | Full Wide Video Graphic Array                                           |

| GM     | Generic Multiplication                                                  |

| GPU    | Graphical Processing Unit                                               |

| HD     | High Definition                                                         |

| HEVC   | High Efficiency Video Codign                                            |

| HM     | HEVC Test Model                                                         |

| HVS    | Human Visual System                                                     |

| IDIQ   | Integrated Direct/Inverse Quantization                                  |

| IEC    | International Electrotechnical Commission                               |

| IQ-SSC | Inverse Quantization Single-Sample Core                                 |

| ISO    | International Standardization Organization                              |

| ITU-T  | International Telegraph Union, Telecommunication Standardization Sector |

| JCT-VC | Joint Collaborative Team on Video Coding                                |

| LCR    | Laço de Codificação Residual                                            |

| LUT    | Look-Up Table                                                           |

| MCM    | Multiplierless Constant Multiplication                                  |

| MPEG   | Motion Picture Experts Group                                            |

| MPSoC  | Multi-Processed System On Chip                                          |

| N/A    | Not applicable                                                          |

| N/D    | Not defined                                                             |

| OU     | Operational Unit                                                        |

| PB     | Prediction Block                                                        |

| PIDIQ  | Parallel Integrated Direct/Inverse Quantization                         |

| PU     | Prediction Unit                                                         |

| PVT    | Process Voltage-Temperature                                             |

| QM     | Quantization Matrix                                                     |

| QP     | Quantization Parameter                                                  |

| QStep  | Quantization Step                                                       |

| QTR    | Quantized Transformed Residual                                          |

|       |                                  |

|-------|----------------------------------|

| R-D   | Rate-Distortion                  |

| RCL   | Residual Coding Loop             |

| RC    | Cadence Encounter RTL Compiler   |

| RDO   | Rate-Distortion Optimization     |

| RD    | Residual Data                    |

| ROM   | Read-Only Memory                 |

| RQT   | Residual Quadtree                |

| RR    | Reconstructed Residuals          |

| RTL   | Register-Transfer Level          |

| spc   | Samples per Cycle                |

| sps   | Samples per Second               |

| SSC   | Single-Sample Core               |

| TB    | Transform Block                  |

| TCF   | Toggle Count File                |

| TR    | Transformed Residual             |

| TU    | Transform Unit                   |

| UHD   | Ultra-High Definition            |

| USB   | Universal Serial Bus             |

| VCD   | Value Change Dump                |

| VCEG  | Video Coding Experts Group       |

| VQVGA | Wide Quarter Video Graphic Array |

| WQXGA | Wide Quad Extended Graphic Array |

# CONTENTS

|            |                                                                         |    |

|------------|-------------------------------------------------------------------------|----|

| <b>1</b>   | <b>INTRODUCTION</b>                                                     | 18 |

| <b>2</b>   | <b>HIGH EFFICIENCY VIDEO CODING</b>                                     | 22 |

| <b>2.1</b> | <b>HEVC Operation</b>                                                   | 22 |

| 2.1.1      | Partitioning Structure                                                  | 24 |

| 2.1.2      | Residual Coding Loop                                                    | 27 |

| <b>2.2</b> | <b>Reference Software and Common Test Conditions</b>                    | 37 |

| <b>3</b>   | <b>HEVC RESIDUE CODING LOOP (RCL) ANALYSIS</b>                          | 40 |

| 3.1        | Throughput Requirements for the HEVC Residual Coding Loop               | 40 |

| 3.2        | BD-Rate Evaluation of the RCL                                           | 45 |

| 3.3        | Analysis of the Frequency-Dependent Quantization (FDQ)                  | 50 |

| 3.4        | Final considerations                                                    | 51 |

| <b>4</b>   | <b>HARDWARE SOLUTIONS FOR THE RESIDUAL CODING LOOP (RCL) COMPONENTS</b> | 53 |

| <b>4.1</b> | <b>FFT-Inspired HEVC 1D-DCT Hardware Design</b>                         | 54 |

| 4.1.1      | Radix-2 DIT FFT algorithm                                               | 55 |

| 4.1.2      | Adjusting the radix-2 DIT FFT for application in HEVC DCT               | 55 |

| 4.1.3      | FFT-inspired HEVC 1D-DCT hardware architecture                          | 56 |

| <b>4.2</b> | <b>HEVC 1D-IDCT Hardware Designs</b>                                    | 60 |

| 4.2.1      | Regular 1D-IDCT                                                         | 60 |

| 4.2.2      | Energy/quality scalable solution for the first 1D-IDCT                  | 63 |

| <b>4.3</b> | <b>Project Space Exploration of Quantization Architectures</b>          | 69 |

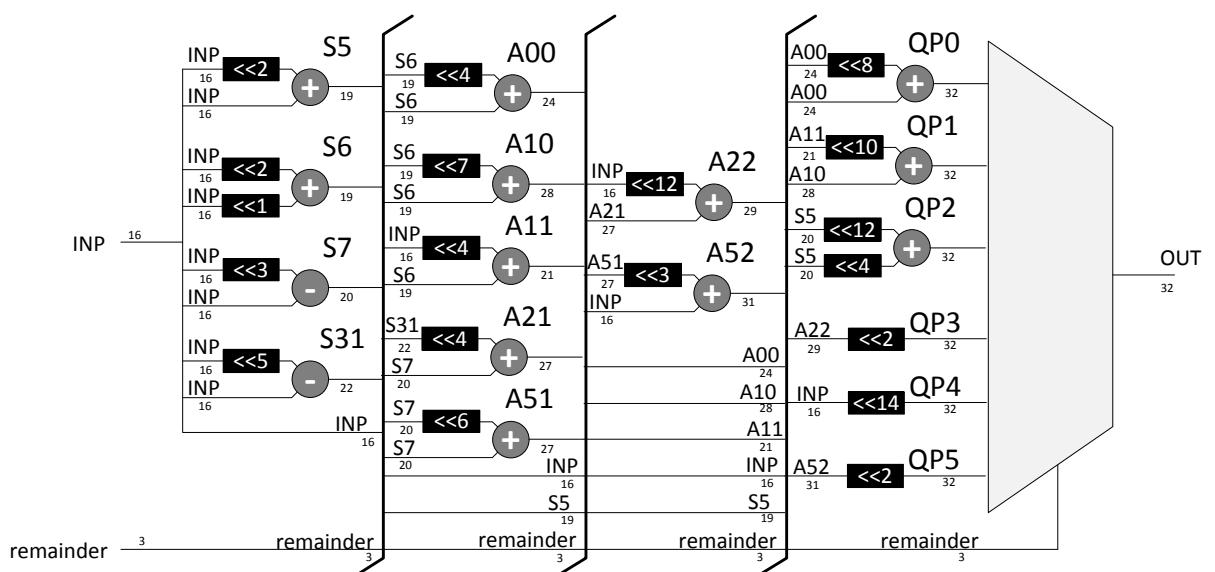

| 4.3.1      | Direct flat-quantization using multiple-constant multiplication         | 71 |

| 4.3.2      | Direct flat-quantization using generic multiplication                   | 73 |

| 4.3.3      | Direct quantization with FDQ support                                    | 74 |

| 4.3.4      | Generic inverse quantization single-sample core                         | 75 |

| <b>4.4</b> | <b>Integrated Direct/inverse Quantization hardware design</b>           | 76 |

| <b>5</b>   | <b>SYNTHESIS RESULTS AND COMPARISONS</b>                                | 80 |

| <b>5.1</b> | <b>FFT-inspired HEVC 1D-DCT synthesis results</b>                       | 81 |

| <b>5.2</b> | <b>HEVC 1D-IDCT synthesis results</b>                                   | 85 |

| <b>5.3</b> | <b>Direct and Inverse Quantization hardware syntheses results</b>       | 88 |

| <b>5.4</b> | <b>Integrated Direct/Inverse Quantization synthesis results</b>         | 90 |

| <b>5.5</b> | <b>Final Considerations</b>                                             | 91 |

| <b>6</b>   | <b>CONCLUSION</b>                                                       | 93 |

| <b>6.1</b> | <b>Future works</b>                                                     | 94 |

|                                                                       |     |

|-----------------------------------------------------------------------|-----|

| <b>REFERENCES</b> . . . . .                                           | 96  |

| <b>APPENDIX A TRANSFORM MATRICES</b> . . . . .                        | 101 |

| <b>APPENDIX B QUANTIZATION MATRICES</b> . . . . .                     | 104 |

| <b>APPENDIX C BD-RATE IMPACT EVALUATION OF THE RCL DATA</b> . . . . . | 108 |

| <b>APPENDIX D QSTEP CONSTANT VALUES</b> . . . . .                     | 110 |

| <b>APPENDIX E PUBLICATIONS</b> . . . . .                              | 111 |

# 1 INTRODUCTION

Multimedia applications, such as digital videos, are very popular nowadays, especially on mobile devices. According to CISCO (2017), 82% of total Internet traffic in 2021 will be related to digital video content. For instance, it would take more than 5 million years for a person to watch the amount of video content crossing internet monthly in 2021. CISCO (2017) also predicted a 19.668 PBytes (petabytes) monthly traffic of digital video content in mobile devices in 2021. Such traffic is more than 11 times bigger than the monthly traffic registered in 2016 (1.756 PBytes).

Nonetheless, uncompressed digital videos require a prohibitive amount of data for their representation. For instance, an UHD 4K video, with a resolution of 3840x2160 pixels, using 24 bits per pixel, and with a frame rate of 120 frames per second (fps), requires 23.89Gbps to broadcast a 10-minute video, or 1.79TBytes for its storage.

Fortunately, digital video data present high level of redundancy. Therefore, much of the information used to represent digital videos can be suppressed by referencing previously processed digital video data. Video coding solutions, such as the state-of-the-art in video coding - High Efficiency Video Coding (HEVC) (ITU-T, 2015), exploit such characteristics. Video coders explore techniques which offer new ways to represent digital videos, suppressing redundant data. Thus, it is possible to encode a digital video reducing the amount of data required to representing the digital video in up to two orders of magnitude (AGOSTINI, 2007). On the other hand, the techniques used in video coders can demand a huge computational effort, due to the amount of data to be processed, and how thoroughly the encoding algorithms search for redundancies (CORREA et al., 2012).

Therefore, encoding ultra-high definition videos in real time using software solutions running on general-purpose processors is difficult to achieve, due to the above-mentioned computational effort requirements. Nonetheless, software-based video encoders are able to encode high-resolution videos in real time by requiring high parallelism level (multithreading), processors operating in high-frequency, and/or significant simplification of the video encoding algorithms. Hence, software-based real-time video encoders have expensive, energy-consuming hardware requirements.

Devices with digital video capabilities, such as mobile devices have limited resources, such as CPU, memory, and energy, i.e. the hardware configurations of mobile devices hardly comply with the hardware requirements of software-based real-time video encoders. Therefore, it is important to develop high-throughput hardware architectures implementing video coding tools to reduce coding time and to allow real-time encoding of beyond high-resolution videos.

Mobile devices can benefit from high-throughput video-encoding dedicated hardware architectures since their use allow the mobile devices to encode digital video in real-time. The real-time digital video encoding capability is important to avoid the use of storage space in the time span between capturing and encoding digital videos, as well as improving the user experience since the user can watch a video as soon as he finishes recording it. The use of video-encoding dedicated hardware architectures supports mobile devices energy-saving requirements since such hardware architectures can be powered off while they are not in use or the energy consumption can be dosed according to the current video encoding quality.

The residual coding loop (RCL), composed of direct transform, direct quantization, inverse quantization, and inverse transform, is a highly-requested stage of the video coding standards since it is used multiple times to test several coding modes (CM) in the prediction stage (BUDAGAVI; FULDSETH; BJONTEGAARD, 2014). Based on the results of the CM testing, the encoder chooses the best trade-off between the encoded video file size and the visual quality of the decoded video. Experiments with the HEVC Test Model, version 16.7 (HM16.7), the reference software of the HEVC, in chapter 3 showed RCL processing between 36 and 267 times the number of samples in the video data, on average, while testing different CM. Given this processing requirements, encoding UHD videos in real time requires high-frequency operated hardware architectures, e.g. RCL components hardware architectures must operate at  $2.0GHz$  to be able to encode UHD 4K videos at 60fps following the same behavior of the HM16.7. RCL components hardware architectures operating at lower frequencies reduce the capability of processing as many CM as the hardware architecture operating under the specified full-frequency. Hence, the reduction of the working frequency of RCL components hardware architectures lead to a bottlenecked processing capability of the encoder. Thus, less CM can be tested, which can lead to suboptimal CM choices and consequent losses in the encoder coding efficiency. Therefore, the RCL must present the highest throughput, the lowest latency, and the lowest possible power dissipation. The throughput increase allows increasing the number of tested CM. The low latency can improve the overall timewise performance of the encoder, since the intermediary RCL results can lead to early termination of the encoding process. And, the low power dissipation is essential while being used in battery-powered devices.

There are several works in the literature focusing on the different components of

the RCL, such as BONATTO et al. (2017), MASERA; MARTINA; MASERA (2017), RENDA et al. (2017), BASIRI; MAHAMMAD (2017); CHATTERJEE; SARAWADEKAR (2017), ANSARI; MANSOURI; AHAITOUF (2016), JRIDI; MEHER (2016), and DIAS; ROMA; SOUSA (2015). The architecture proposed in those works support processing between one (ANSARI; MANSOURI; AHAITOUF, 2016) and 245 (BASIRI; MAHAMMAD, 2017) CM in HD 1080p videos at 30fps, and between one (BONATTO et al., 2017) (CHATTERJEE; SARAWADEKAR, 2017) and 30 (BASIRI; MAHAMMAD, 2017) CM in UHD 4K videos at 60fps. However, experiments in chapter 3 show that optimal encoding can be achieved by processing up to 267 CM. Moreover, the processing restriction in the related works requires an encoder algorithmic simplification which can decrease the encoder efficiency. In conclusion, the related works seem to overlook their coding losses due to their usual single CM processing targets. The usage of hardware architectures for RCL components with higher throughput capability allows the exploration of multiple CM in real time. As the number of CM processed increases, it is more likely to find the best CM (global maxima, instead of the local maxima provided by related works). Therefore, the limited throughput in related works can have a significant (and negative) impact on the encoder coding efficiency, regarding the trade-off between the quality and the size of the encoded video. In other words, the claim of real-time encoding in related works should be bound by the coding efficiency loss due to the limitation of the number of CM processed, since RCL components hardware designs must be able to process up to the above mentioned 267 CM to be called real-time RCL components hardware designs.

The objective of this work is to develop multiple energy/quality-aware dedicated hardware solutions to increase the throughput of the components of RCL in HEVC standard, which allows processing dozens of CM in high-resolution videos in real time. In such context, the contributions of this work are:

- An analysis of the throughput requirements of the HEVC RCL components;

- An analysis of the impact of the throughput limitation on the encoded video size;

- A frequency-dependent quantization tool impact analysis on the encoded video (size and quality) and on the hardware architecture (area, frequency and power);

- A dedicated hardware design of an FFT-inspired direct 1D-DCT;

- A regular 1D-IDCT dedicated hardware design and energy/quality scalable 1D-IDCT dedicated hardware design;

- A project space exploration of the direct and inverse quantization hardware architectures;

- An integrated direct/inverse quantization hardware architecture.

This work proposes innovative dedicated hardware solutions for the HEVC RCL components, focusing in low power, higher throughput and better coding efficiency. The 1D-DCT presented is based on the Fast Fourier Transform (FFT), which allows an intensive hardware reuse and consequent energy-consumption reduction. Furthermore, an energy/quality scalable 1D-IDCT is presented using a bypass engine based on statistical analysis, allowing the adjustment of the trade-off between coding-efficiency and energy-efficiency. Moreover, a project space exploration of quantization architecture is made to maximize throughput- and energy-efficiency of the direct- and inverse-quantization, considering the flat-quantization and the frequency dependent quantization (FDQ), the two quantization methods supported by HEVC. Also, an integrated direct/inverse quantization is presented, which improves the throughput and reduces energy consumption, by reducing the number of arithmetical operations through the integration of the direct quantization and the inverse quantization.

The remaining of this work is organized as follows: chapter 2 describes the HEVC encoder, its resources and the more relevant encoding tools for this master thesis, chapter 3 presents statistical analyses regarding the RCL use, impact of limiting RCL usage, and the cost-effectiveness of using an optional HEVC coding tool, chapter 4 describes the RCL components hardware solutions designed during this work, chapter 5 presents the results of the hardware solutions described in chapter 4 and compares them with related works, and chapter 6 presents the conclusions and future works.

## 2 HIGH EFFICIENCY VIDEO CODING

The High Efficiency Video Coding (HEVC) standard, developed by the Joint Collaborative Team on Video Coding (JCT-VC), is considered the state-of-the-art in video coders. The JCT-VC is composed of members of the Video Coding Experts Group (VCEG), from the International Telegraph Union, Telecommunications Standardization Sector (ITU-T), and members of the Motion Picture Experts Group (MPEG), from the International Standardization Organization/International Electrotechnical Commission (ISO/IEC) technical committee. HEVC was released in 2013 under the premise of reducing by half the video size when compared with the previous encoding video standard, the H.264 (ITU-T, 2003), while maintaining the encoded video objective quality (ITU-T, 2015). The encoding efficiency of HEVC is due to the adoption of several new or improved coding tools. The following sections describe the operation of the HEVC, and detail the resources available for HEVC – the HEVC Test Model (HM) reference software (FLYNN et al., 2011) and the Common Test Conditions (CTCs) (BOSSEN, 2013) – to validate and compare results of works related to HEVC.

### 2.1 HEVC Operation

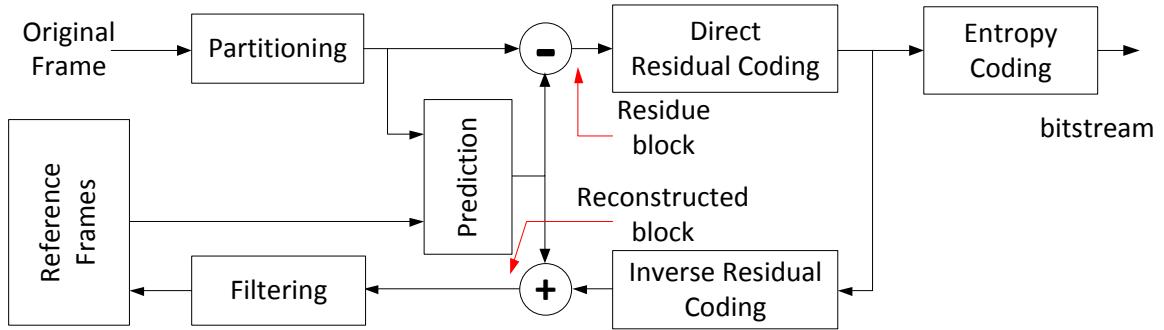

The HEVC standard uses block-based hybrid coding techniques (SCHWARZ; SCHIERL; MARPE, 2014). Therefore, digital videos are encoded through video samples prediction, prediction errors (residuals) transformation, and entropy encoding of prediction information and transformed residuals. The video samples used in the prediction stage are sample blocks extracted from video frames. Figure 1 presents the data flow for HEVC encoder.

The original frame is the raw digital video frame input, which is partitioned into small blocks by the partitioning stage to be processed by the following stages. In the prediction stage, the current block is compared with the reference frames, in a search for the most similar block. The prediction stage can use one of two prediction modes:

- *Intra-picture prediction*: In the intra-picture prediction, the decoded border of adjacent blocks are used as reference data for spatial prediction. Intra-picture predi-

Figure 1 – HEVC encoder data flow

tion supports 33 directional modes, plus planar prediction mode (surface fitting), and DC (flat) prediction mode. The selected intra-picture prediction modes are encoded by deriving most probable modes based on modes used in previously encoded PBs (LEINEMA; HAN, 2014).

- *Inter-pictures prediction:* The encoding process for inter-pictures prediction consists of choosing motion data comprising the selected reference picture and motion vector to be applied for the prediction of the samples of each block. The encoder and decoder generate identical inter-pictures prediction by applying motion compensation using the motion vector and mode decision data (SULLIVAN et al., 2012).

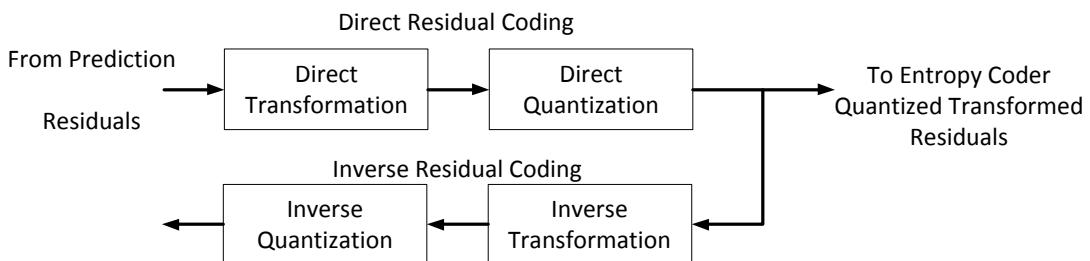

The most similar block is subtracted from the original block to generate the residue block, which will be processed by the direct residual coding stage and inverse residual coding stage. The direct residual is composed of the direct transform component and the direct quantization component. The direct transform component transforms residual data (RD) from the spatial domain to transformed residuals (TR) in the frequency domain. The direct transform concentrates the information energy in few low-frequency coefficients in TR. The direct quantization scales down TR, reducing the amplitude for low-frequency TR and setting most high-frequency TRs to zero, which improves the compression efficiency of entropy coding. The quantized transformed residues (QTR) are used by the entropy coding to calculate the bit-rate used in the Rate-Distortion Optimization (RDO) tool or to generate the output bitstream of the coded video. The QTR data are also processed by the inverse quantization and, subsequently, by the inverse transform. The reconstructed residues (RR) are combined with block prediction data to reconstruct the block as it would be reconstructed in the decoder, to generate the distortion metric used by RDO, or to be used as reference in next blocks predictions. Therefore, the RCL components have high-processing demand. Thus, hardware-implemented RCL components are required to achieve real-time encoding of high-resolution videos.

The RDO calculates the Rate-Distortion cost (RDCost) for each CM and chooses the CM with the lowest RDCost for the actual encoding. Bit-rate and distortion metrics are combined into the RDCost, expressed in (1), where  $D$  is the distortion metric,  $R$  is the bit-rate metric, and  $\lambda$  is the Lagrange multiplier, which balances the trade-off between distortion (quality) and bit-rate (size) (SCHWARZ; SCHIERL; MARPE, 2014).

$$RDCost = D + \lambda \times R \quad (1)$$

The focus of this work is the high-throughput, low-power hardware implementations of RCL components (direct residual coding and inverse residual coding, in Figure 1). Therefore, the RCL and its components will be detailed in section 2.1.2. Nonetheless, the HEVC partitioning structure (partitioning stage, on Figure 1) must be further detailed, in section 2.1.1, to better understand the RCL operation.

### 2.1.1 Partitioning Structure

In HEVC partition structure there are four types of units, with distinct characteristics and functions: Coding Tree Units (CTU), Coding Units (CU), Prediction Units (PU), and Transform Units (TU) (SULLIVAN et al., 2012). Furthermore, there are four block types: Coding Tree Blocks (CTB), Coding Blocks (CB), Prediction Blocks (PB), and Transform Blocks (TB). The blocks are bi-dimensional collections of data associated to one of the color channels in the samples of a unit. For instance, a PU is composed of one luminance PB (Y channel) and two chrominance PBs (U and V channels). Therefore, there is an equivalent relationship between TUs and TBs, between CUs and CBs, and between CTUs and CTBs. On the other hand, the units follow a hierarchy such as a CTU is a collection of CUs and a CU is a collection of PUs and TUs. The division occurs in a structure called quadtree (quadtree).

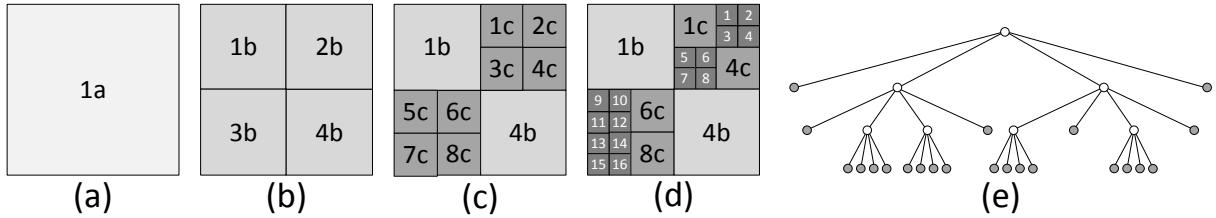

The quadtree takes the highest-hierarchy unit as its root node. The root node can remain whole or be split into four nodes of the same size. Each resulting node can be further split or not, recursively, as long as the node size is bigger than the minimum node size specified (BUDAGAVI; FULDSETH; BJONTEGAARD, 2014). Figure 2 shows an example of a quadtree division. The block in Figure 2(a) is a CTU representing the root node of the quadtree. The root node is split into four equal-sized nodes (1b to 4b) in Figure 2(b). In Figure 2(c), two of the four blocks (2b and 3b) are further split, and 1b and 4b blocks remain with the same size, turn into leaf nodes, and are converted into CUs. In the sequence, only the resulting blocks from 2b and 3b split (1c to 8c) are evaluated. Figure 2(d) shows that 1c, 4c, 6c and 8c blocks are not split and thus are converted into CUs, while blocks 2c, 3c, 5c, and 7c are further split. The resulting blocks from the last split (1d to 16d) are considered leaf nodes and converted into CUs since they have the minimum size allowed for a CU. Figure 2(e) shows the

quadtree representing the partitioning of CTU 1a.

Figure 2 – Quadtree partitioning example

#### 2.1.1.1 Coding Tree Unit

The CTUs are square-sized units with sizes of 64x64, 32x32, and 16x16. Nonetheless, different CTUs size ranges can be defined in the HM configuration files. The CTU size flexibility can be explored to adapt to the requirements of a specific application, such as memory restriction or coding/decoding time restriction. Usually, the use of bigger CTUs improves the coding efficiency by further reduction on the encoded video size (SULLIVAN et al., 2012).

#### 2.1.1.2 Coding Units

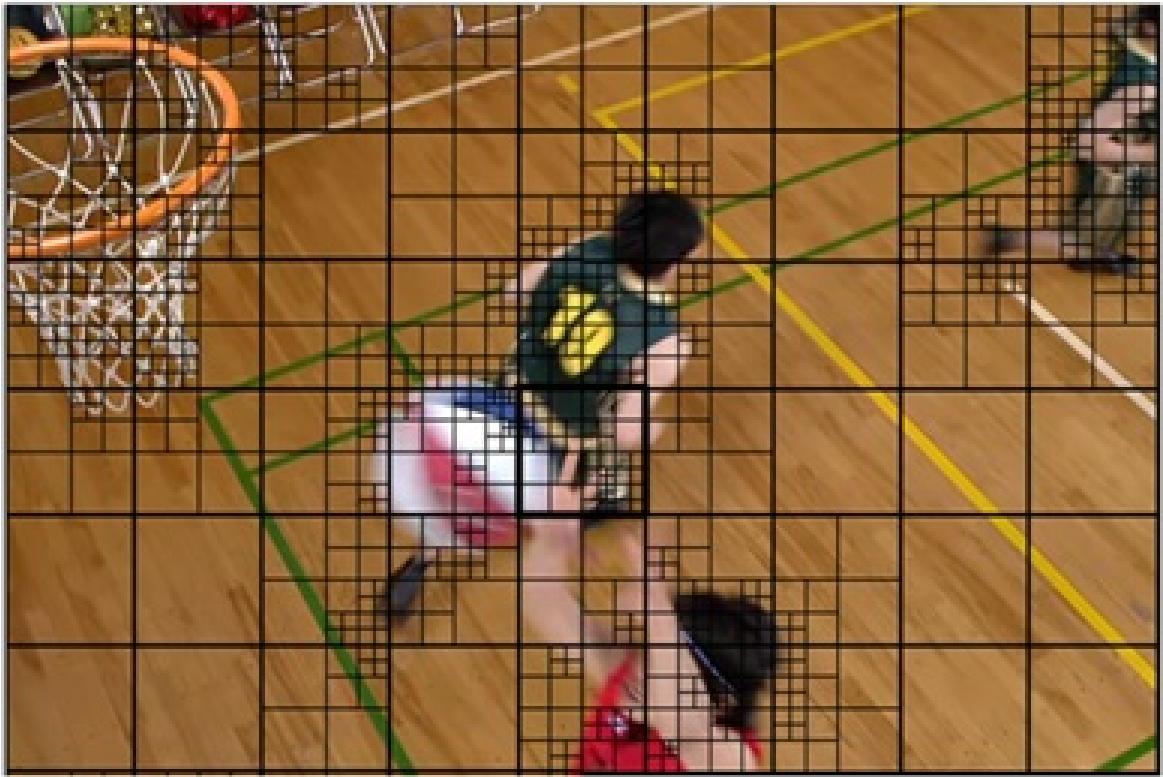

The leaf nodes of CTU-rooted quadtrees are called CUs. The sizes allowed for CUs are 64x64, 32x32, 16x16, 8x8, and  $4 \times 4$ . Larger CUs are more appropriate to encode homogeneous regions. On the other hand, image regions with more details can be better encoded using a collection of smaller CUs. Thus, the bigger the image details level, smaller is the CU size recommended. Figure 3 shows the CU partitioning applied to a frame in the BasketballDrill video.

#### 2.1.1.3 Prediction Units

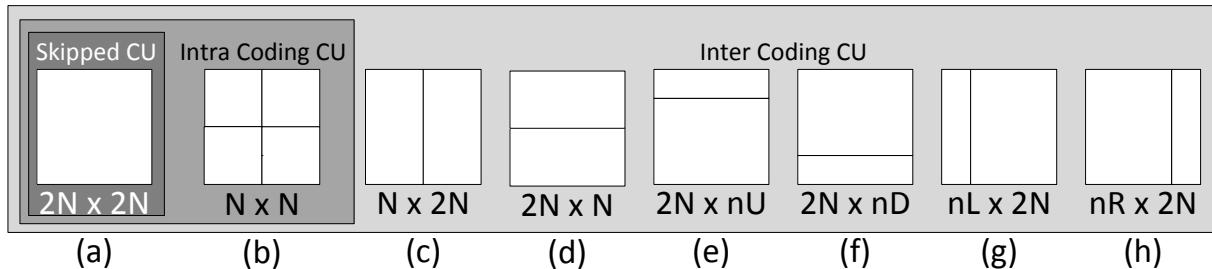

Leaf nodes of a CU-rooted quadtree can be merged or combined into quadtrees having PUs as leaf nodes. Therefore, rectangular- or polygonal-shaped PUs are possible. Such formats are accomplished by recursively split CU-rooted quadtrees until the smaller unit size possible, and grouping adjacent leaf nodes, regardless their sizes to achieve such formats. However, to avoid unnecessary computational effort, some formats were predefined. The predefined sizes/formats for PUs and PBs are: 64x64,  $64 \times 48$ , 64x32, 64x16, 48x64, 32x64, 32x32, 32x24, 32x16, 32x8, 24x32, 16x64, 16x32, 16x16, 16x12, 16x8, 16x4, 12x16, 8x32, 8x16, 8x8, 8x4, 4x16, and 4x8. The prediction type in which the CU is used limits the type of allowed PU formats. Each CU can be sorted into three categories, according to the CU prediction type (SULLIVAN et al., 2012):

- *Intra Coded CU*: This category is applied to CUs used by the intra-picture prediction. A PB in an Intra Coded CU outputs a prediction direction (0 to 34) and

Figure 3 – CU partitioning applied to a frame in the BasketballDrill video (ZHOU; ZHOU; CHEN, 2013)

a residue block. Only square-shaped PUs (formats (a) and (b) in Figure 4) are used in Intra Coded CUs.

- *Inter Coded CU*: Applicable to CUs used by the inter-pictures prediction, its PB outputs a motion vector and a residue block. All predefined formats are allowed for Inter Coded CU PBs (formats (a) to (h) in Figure 4).

- *Skipped CU*: The Skipped CU category is a special case of the Inter Coded CU, where both the motion vector and the residue block are equal to zero. Skipped CUs cannot be split. Therefore, the respective PB must have the same size of the CU. The only format allowed for the PB is format (a) in Figure 4.

Figure 4 – PU formats allowed in HEVC

Frequently, chrominance PBs follow the partitioning scheme from the luminance PB in the same PU. However, when the CU size is  $8 \times 8$  and the method of division is NxN, as in Figure 4(b), the 2Nx2N division method, in Figure 4(a) is used instead in the chrominance PB, avoiding a PU smaller than  $4 \times 8/8 \times 4$ .

#### 2.1.1.4 Transform Units

As it occurs with the PUs, one TU (or a set of TUs) is derived from each CU. The TUs are the leaf nodes of a CU-rooted quadtree, called Residual Quadtree (RQT). A TU is a unit containing residues in the spatial domain or quantized and transformed residues. In each TU, an integer discrete transform with the same dimension of the TU is applied to the residues in the spatial domain. The residues in the frequency domain, which are the transform outputs, are sent to the decoder after being quantized, in each TU (ITU-T, 2015). The residues in spatial domain can come from several PUs, which are regrouped into the CU used as root node for the TU quadtree (BUDAGAVI; FULDSETH; BJONTEGAARD, 2014). TUs were specified in four sizes: 32x32, 16x16, 8x8, and  $4 \times 4$ .

#### 2.1.2 Residual Coding Loop

The HEVC RCL, the focus of this work, is composed of a direct transform, direct quantization, inverse quantization, and inverse transform. The RCL block diagram is shown in Figure 5.

Figure 5 – RCL block diagram

Due to the characteristics of the residue information, the direct transform concentrates the relevant residue information in the low-frequencies related transformed residuals. On the other hand, most of the high-frequency related transformed residuals are orders of magnitude smaller than the low-frequency related transformed residuals. Direct quantization reduces the magnitude of the transformed residuals, reducing most of the quantized transformed residuals to zero, improving the entropy coding efficiency.

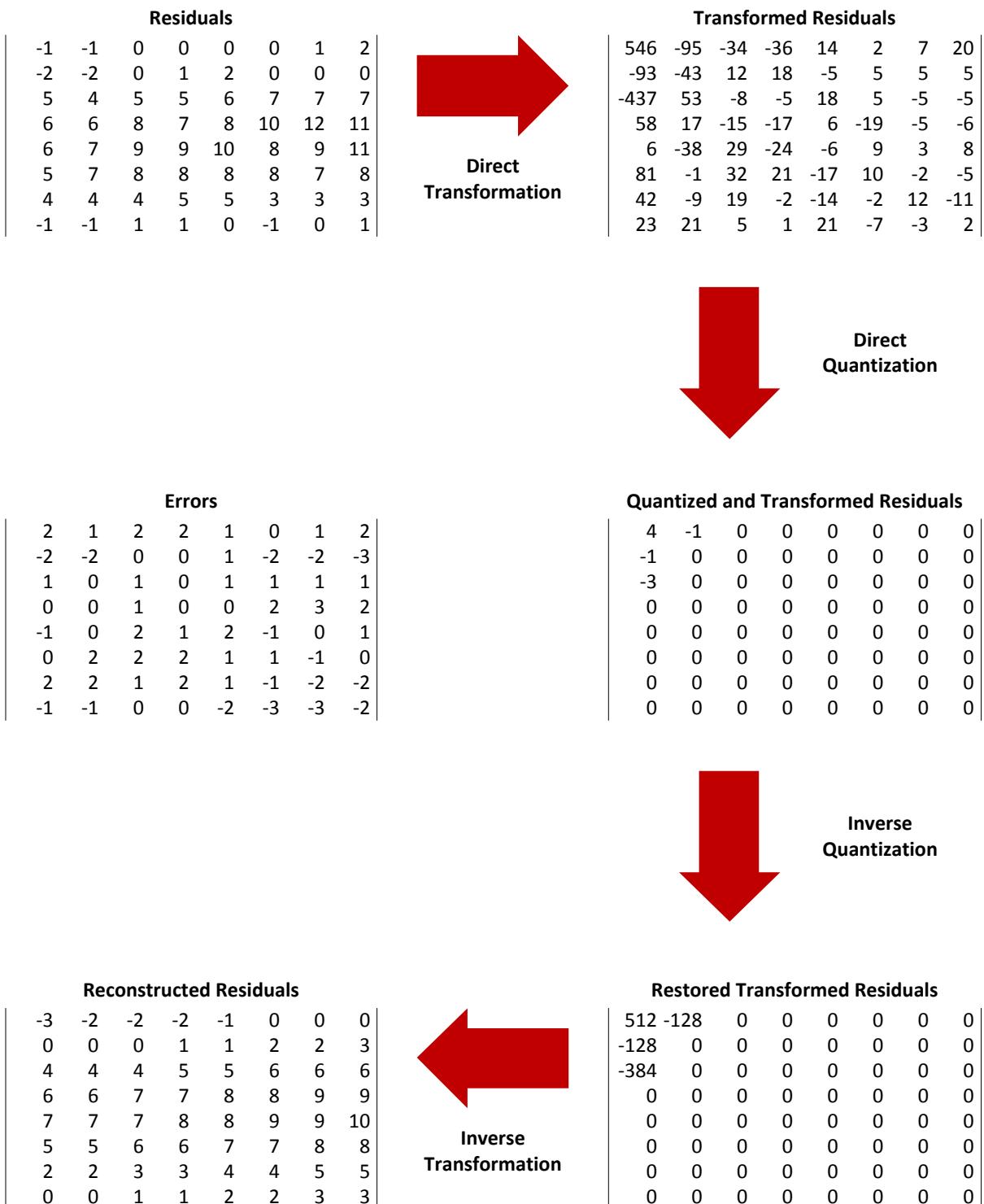

Figure 6 shows an example of the RCL using real data collected from HM. One can notice that 60 out of 64 quantized transformed residuals (QTR) values are zero, while the non-zero QTR values range from -3 to 4. This range of values eases the entropy coding because there is a large number of sequential bits with the same value.

The losses associated to the HEVC RCL are shown in the Error matrix, in Figure 6. The Error matrix is given by the difference between the original residues and the restored transformed residuals (RTR). Such errors are information losses introduced by the direct quantization.

Figure 6 – Example of RCL operation

The quantization information losses are more apparent in the high-frequency Transformed Residuals (TR) data, since they are usually converted to zero in the direct quantization stage, making them unrecoverable. Nonetheless, those losses have a small impact on the perceptual quality of the reconstructed video image, since the Human Visual System (HVS) is less sensitive to high-frequency components of images (HAQUE; TABATABAI; MORIGAMI, 2011). Moreover, the losses inserted in the direct quantization stage can build up errors, as the images used in the encoder as reference are different from reconstructed images in the decoder. Therefore, the encoder implements and uses the inverse quantization and inverse transform to reconstruct the reference images as they are reconstructed in the decoder.

The HEVC RCL is used extensively during video encoding, since it must process different CM (combination of block sizes and prediction modes) to generate bitrate and distortion metrics, allowing the RDO to select the best trade-off between output encoded video size and reconstructed video image quality. However, there are a few special operation modes in HEVC (BUDAGAVI; FULDSETH; BJONTEGAARD, 2014) which affect RCL operation:

1. I\_PCM Mode: The prediction, the transform, the quantization and the entropy encoding are not used in I\_PCM mode. This mode is recommended when the residuals in one CU are not suitable for hybrid coding processing, such as images with excessive noise. Such blocks processed by hybrid coding can generate an excessive quantity of bits. Therefore, the encoding processing is merely an adjustment on the output samples bit depth, when bit depth of input samples are different from bit depth of output samples.

2. Lossless mode: The transform and quantization are bypassed in this mode. Therefore, the decoder can reconstruct the video exactly as the original video. The lossless mode is defined at CU level, therefore, it is possible to mix lossy and lossless CUs in the same frame. The lossless mode can improve the coding of mixed-content videos, such as natural videos combined with text or synthesized images. In these cases, CUs with natural video data can use lossy encoding, while CUs containing synthesized elements can use lossless encoding.

3. Transform skipping mode: Using transform skipping mode, the transform is not used and the residuals on the spatial domain are applied directly to the direct quantization. This mode is used in cases where there are well-defined borders, such as synthesized images or texts. The use of transform and quantization in this type of images can deteriorate border definitions. Moreover, the transform skipping mode is restricted to  $4 \times 4$  TBs.

The following subsections described the four components of the HEVC RCL:

### 2.1.2.1 Direct Transform

The HEVC specifies transform matrices with sizes 32x32, 16x16, 8x8, and 4 × 4. According to BUDAGAVI; FULDSETH; BJONTEGAARD (2014), more options in transform sizes allow bigger coding efficiency, although more transform sizes increase the computational effort.

The Discrete Cosine Transform (DCT) is the main transform method used in the HEVC and it is applied to all TB sizes. Alternatively, the Discrete Sine Transform (DST) can be used in intra-predicted luminance-residuals of 4 × 4 TBs. The two-dimensional DCT (2D-DCT) of size NxN produce transformed residue  $F(u, v)$  from input residuals  $f(u, v)$ , as expressed in (2).

$$F(u, v) = \sqrt{\frac{2}{N}} \sqrt{\frac{2}{M}} \sum_{i=0}^{N-1} \sum_{j=0}^{M-1} \Lambda_i \Lambda_j \cos\left[\frac{\pi u}{2N}(2i+1)\right] \cos\left[\frac{\pi v}{2M}(2j+1)\right] f(u, v) \quad (2)$$

where  $\Lambda_k = 1$  and  $\sqrt{2}$  for  $k=0$  and  $k>0$ , respectively.

The transform operation through (2) uses a huge number of additions and multiplications, as seen in Table 1.

Table 1 – Arithmetical operations performed by 2D-DCT (JESKE, 2013)

| Size    | Additions | Multiplications |

|---------|-----------|-----------------|

| 4 x 4   | 240       | 256             |

| 8 x 8   | 4,032     | 4,096           |

| 16 x 16 | 65,280    | 65,536          |

| 32 x 32 | 1,047,552 | 1,048,576       |

Since the transforms are always squared, i.e.  $N = M$ , and the way (2) is represented in (3), one can notice the DCT operation can be done in two steps (GHANBARI, 2003).

$$F(u, v) = \left\{ \sqrt{\frac{2}{N}} \sum_{i=0}^{N-1} \Lambda_i \cos\left[\frac{\pi u}{2N}(2i+1)\right] \right\} \times \left\{ \sqrt{\frac{2}{M}} \sum_{j=0}^{M-1} \Lambda_j \cos\left[\frac{\pi v}{2M}(2j+1)\right] \right\} \times f(u, v) \quad (3)$$

Thus, the HEVC 2D-DCT can be processed through two executions of one-dimension direct transforms, using a buffer to store the partial results and transpose the coefficient matrix, according to (4) and (5), or in (6) using matrix notation. The transposition of the intermediate matrix  $f'(u, v)$  in (4) is denoted by the permutation of  $u$  and  $v$  indexes in (5).

$$f'(u, v) = \sqrt{\frac{2}{N}} \sum_{i=0}^{N-1} \Lambda_i \cos \left[ \frac{\pi u}{2N} (2i + 1) \right] f(u, v) \quad (4)$$

$$F(u, v) = \sqrt{\frac{2}{M}} \sum_{j=0}^{M-1} \Lambda_j \cos \left[ \frac{\pi u}{2M} (2j + 1) \right] f'(v, u) \quad (5)$$

$$F = C \times (f \times C)^T \quad (6)$$

The  $C_N$  matrices used in (6) are the transform matrices, where  $N$  denotes the size of the matrix. Basis vectors  $c_i$  of  $C_N$ , defined as  $c_i = [c_{i0}, \dots, c_{i(N-1)}]^T$ , where  $i = 0, \dots, M - 1$ , are normal and orthogonal. Orthogonal vectors are vectors compliant to the property  $c_i \times c_j^T = 0$  where  $i \neq j$ . Orthogonal vector allow output data be uncorrelated, which help increasing entropy efficiency. Since  $C_N$  basis vectors are normal vectors, compliant to the property  $c_i c_i^T = 1$ , a flat frequency response in the output transform matrix is assured.

Matrices  $C_N$  for blocks  $32 \times 32$ ,  $16 \times 16$ ,  $8 \times 8$ , and  $4 \times 4$ , are previously calculated and approximated to integer values. A straightforward manner to define the integer approximation for the matrix elements is to multiply each element for an integer number (usually between  $2^5$  e  $2^{16}$ ) and round them up to the nearest integer. Tables 28 to 31 in Appendix A represent the integer approximations matrices used by HEVC for the DCTs with block size  $4 \times 4$ ,  $8 \times 8$ ,  $16 \times 16$ , and  $32 \times 32$ , respectively.

Given the row indexes and column indexes ranging from 0 to  $N - 1$ , the even-indexed rows in all matrices behave like even functions, i.e., the left half of the row (columns 0 to  $(N - 1)/2$ ) is mirrored in the right half of the row (columns  $N/2$  to  $N - 1$ ). On the other hand, the odd-indexed rows behave like odd functions. Therefore, it is said that even-indexed rows present even symmetry, and odd-indexed rows present odd symmetry (BUDAGAVI; FULDSETH; BJONTEGAARD, 2014).

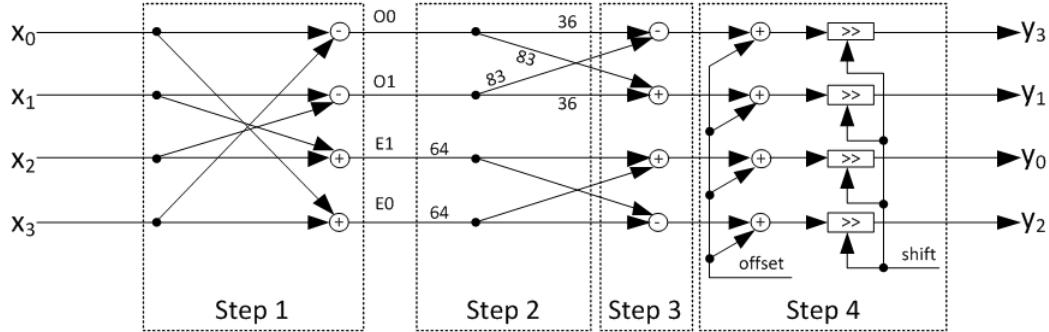

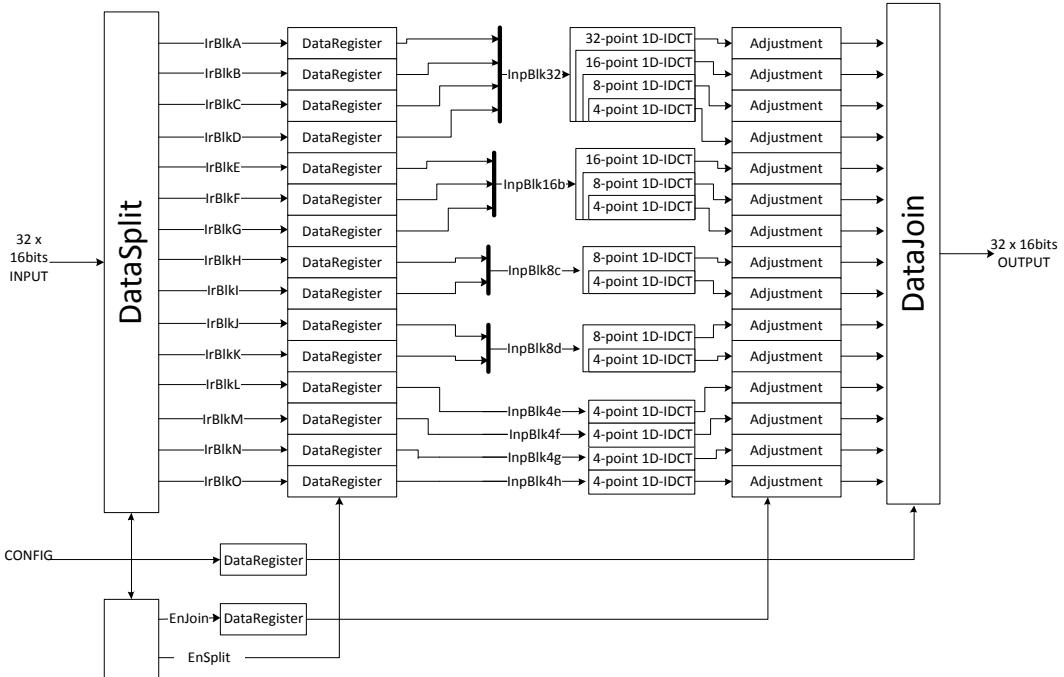

Based on these observations, HUNG; LANDMAN (1997) developed the Even/Odd Decomposition (EOD) algorithm. Using EOD algorithm, a 4-point 1D-DCT, shown in Figure 7, can be calculated using the following steps:

1. For each line, perform additions and subtraction in butterfly, according to Figure 7;

2. Multiply the previous results by the unique coefficients in Table 28 (36, 64, and 83);

3. Sum and subtract results from the previous step;

4. Adjust the bitlength in 1D-DCT output, rounding up to the nearest integer.

In step 4, the rounded bitlength adjust is performed by the addition of an offset value to the results from step 3, and a right shift operation. The offset value and the

Figure 7 – 4-point 1D-DCT block diagram

Table 2 – Offset and shift parameters for different sized 1D-DCT (JESKE, 2013)

| DCT     | 1st 1D-DCT |       | 2nd 1D-DCT |       |

|---------|------------|-------|------------|-------|

|         | offset     | shift | offset     | shift |

| 4 x 4   | 1          | 1     | 128        | 8     |

| 8 x 8   | 2          | 2     | 256        | 9     |

| 16 x 16 | 4          | 3     | 512        | 10    |

| 32 x 32 | 8          | 4     | 1024       | 11    |

number of bits shifted in step 4 have different values for the first 1D-IDCT or the second 1D-IDCT and for different TB sizes. Table 2 shows offset and shift values for the four matrices sizes.

Moreover, the coefficients highlighted in Tables 29 to 31, in Appendix A, are the coefficients of the left-half of the even-indexed rows of the transform matrices, where the coefficients of any given transform matrix are exactly the coefficients of the immediate smaller transform matrix. For instance, the coefficients in the  $4 \times 4$  transform matrix (Table 28) are the highlighted coefficients in the  $8 \times 8$  transform matrix (Table 29). Therefore, in a hardware-implemented 1D-DCT, it is possible to reuse the hardware. The hardware reuse consists in using architectures of smaller 1D-DCT to process the samples of even-indexed rows of the immediate bigger 1D-DCT.

### *Direct Discrete Sine Transform*

The HEVC standard can use a fixed point representation of Type-7 discrete sine transform (DST) to be applied to  $4 \times 4$  luminance intra-prediction residual blocks. The forward DST transform matrix is given in Table 32, in Appendix A, although the inverse DST transform matrix is the transposition of the forward DST transform matrix. The usage of the DST provides around 1% bit-rate reduction while coding intra pictures(SAXENA; FERNANDES, 2013).

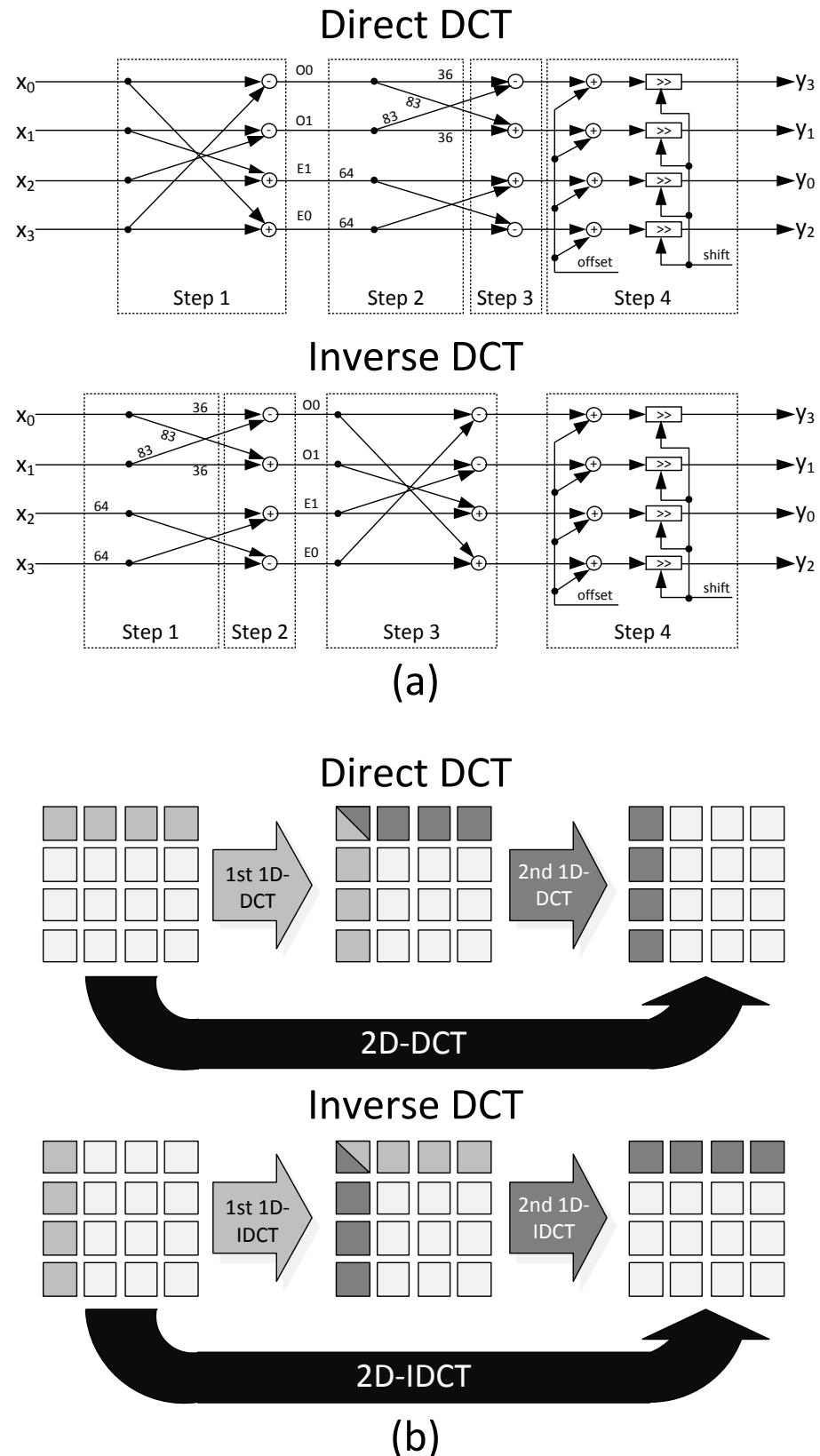

Figure 8 – Difference between DCT and IDCT. (a) EOD algorithm. (b) Processing order.

### 2.1.2.2 Inverse Transform

Inverse transform changes the representation of RTR from the frequency domain to spatial domain. The inverse transform is quite similar to the direct transform. Although, there are two main differences:

1. *Processing direction*: As shown in Figure 8, direct transform inputs (from the TB) are processed row-by-row and direct transform outputs are stored column-by-column. On the other hand, inverse transform inputs are processed by reading input TB data column-by-column and inverse transform outputs are stored row-by-row. Figure 8(b) shows the difference in processing direction between direct transform and inverse transform. Although inverse transform uses the same transform matrices  $C_N$ , the matrix notation of inverse transform is:  $F = (C_N \times f) \times C_N^T$ .

2. *Operation Order in EOD Algorithm*: A variation of EOD algorithm can be applied to the inverse transform, where the butterflies operations (stage 1 in Figure 7) occur after the weighted sum of RTR (stages 2 and 3 in Figure 7), as shown in Figure 8(a).

### 2.1.2.3 Direct Quantization

The quantization in the HEVC is performed as a function of the Quantization Parameter (QP) value, where it can assume values between 0 to 51. The QP value impacts on encoding time, output video size and reconstructed video quality. Bigger QP values are used to reduce output video size and encoding time, although they also reduce the reconstructed video quality. On the other hand, smaller QP values have less impact on the reconstructed video quality, despite the increase in the output file size and in the encoding time. Quantization consists in dividing transformed residuals by a Quantization Step (QStep) and rounding them to the nearest integer towards zero. The quantization is responsible for improving the conditioning of the transformed residuals and increasing the entropy coder efficiency. The quantization step value is determined by (7).

$$QStep = 2^{\frac{QP-4}{6}} \quad (7)$$

QStep values, as a function of QP, has a logarithmic characteristic, as shown in Figure 9. Point A in Figure 9 is one of many QStep values presenting fractional value. Processing fractional data requires high computational effort, therefore a simplification is required. On the other hand, point B and C, highlighted in Figure 9, show how QStep value doubles each time QP value increases of six. Therefore, QP can be divided by six, where the remainder of the division is used to determine the value of QStep, and

the quotient of the division indicates the number of bits to be shifted to right (equivalent to divide by  $2^n$ ).

Figure 9 – Quantization step value according to QP value

Although the division-by-six approach can reduce the computational effort on the quantization, still a division by a fractional value must be processed. A simplified version of quantization is presented by BUDAGAVI et al. (2013), where the QStep values related to QP ranging from 0 to 5 are processed in advance and stored. Such QStep values are inverted and shifted 14 bits to the left. Therefore, an integer approximation of direct quantization is presented in (8), where  $G = [26214, 23302, 20560, 18396, 16384, 14564]^T$  is the vector with inverse approximations of QStep related to QP ranging from 0 to 5 and  $\lfloor \cdot \rfloor$  is the rounding to the nearest integer towards zero.

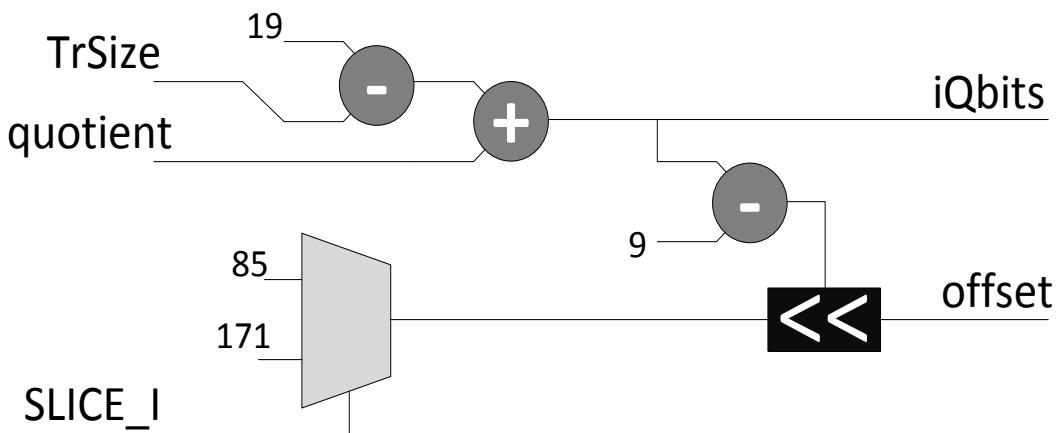

The integer approximation for the direct quantization processing is given by (8), where:

- $qBits$ , given by (9), is the number of bits that quantized transformed residue value must be shifted to the right to compensate the bitlength expansion of  $G(QP\%6)$  and to adjust to the TB size ( $N$ );

- $offset$ , given by (10), is a rounding correction parameter for the quantized transformed residue. Offset depends on the prediction type and the  $qBits$  parameter.

$$Z = sign(W) \times [|W| \times G(QP\%6) + offset] \gg shift \quad (8)$$

$$qBits = 21 + \left\lceil \frac{QP}{6} \right\rceil - \log_2 N \quad (9)$$

$$offset = \begin{cases} 171 \ll (qBits - 9) & , \text{ if slice type is Intra-predicted} \\ 85 \ll (qBits - 9) & , \text{ otherwise} \end{cases} \quad (10)$$

Since the HVS is less sensitive to high-frequency information, the HEVC can use the frequency-dependent quantization (FDQ) tool, which explores this HVS property. Therefore, FDQ usage reduces even further high-frequency transformed residuals and increases the coding efficiency. Moreover, (PRAGNELL; SANCHEZ, 2016) claim FDQ usage has a negligible effect on the perceptual quality of the reconstructed video. The QStep applied to quantized residues according to its frequency are given by (11), where  $u$  and  $v$  (ranging from 0 to 7) are the row and column position of the residue in the output transform matrix, respectively, and  $f'(u, v)$  is the normalized spatial-radial frequency, in cycles per degree (PRAGNELL; SANCHEZ, 2016). Thus, the FDQ-compliant direct quantization equation is given by (12).

$$w(u, v) = 2, 2 \times [0.192 + 0.114 \times f'(u, v)] \times e^{-[0.114 \times f'(u, v)]^{1,1}} \quad (11)$$

$$Z = sign(W) \times [|W| \times G(QP\%6) \times w(u, v) + offset] >> shift \quad (12)$$

The use of FDQ increases the number of quantization coefficients from six to 384, which could increase the memory access and energy consumption. The FDQ tool is optional in HEVC and disabled by default in its reference software (PRAGNELL; SANCHEZ, 2016).

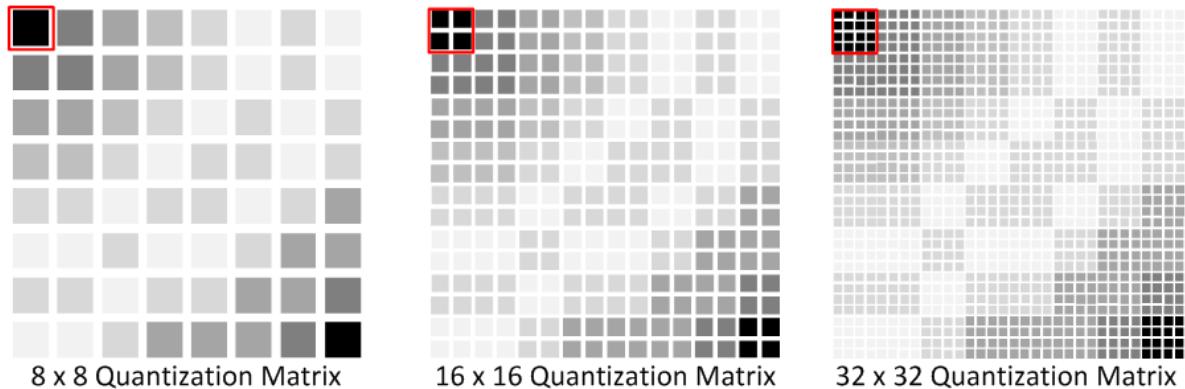

Figure 10 – Relationship between different QM sizes

Despite the HEVC support of TBs up to  $32 \times 32$ , only  $8 \times 8$  quantization matrices (QM) are present in the HM (Tables 33 to 38 in appendix B), since the QM for  $16 \times 16$  and  $32 \times 32$  TBs are derived from the  $8 \times 8$  QM. Each  $8 \times 8$  QM coefficient is replicated twice in both directions to generate  $16 \times 16$  QM. Similarly, each  $8 \times 8$  QM coefficient is replicated four times in both directions to generate  $32 \times 32$  QM. Figure 10 shows the coefficient relationship between  $8 \times 8$  QMs,  $16 \times 16$  QMs, and  $32 \times 32$  QMs. There

are no  $4 \times 4$  QMs since  $4 \times 4$  TBs are not subjected to FDQ. Therefore,  $4 \times 4$  TBs are processed as FDQ is disabled, regardless its configuration.

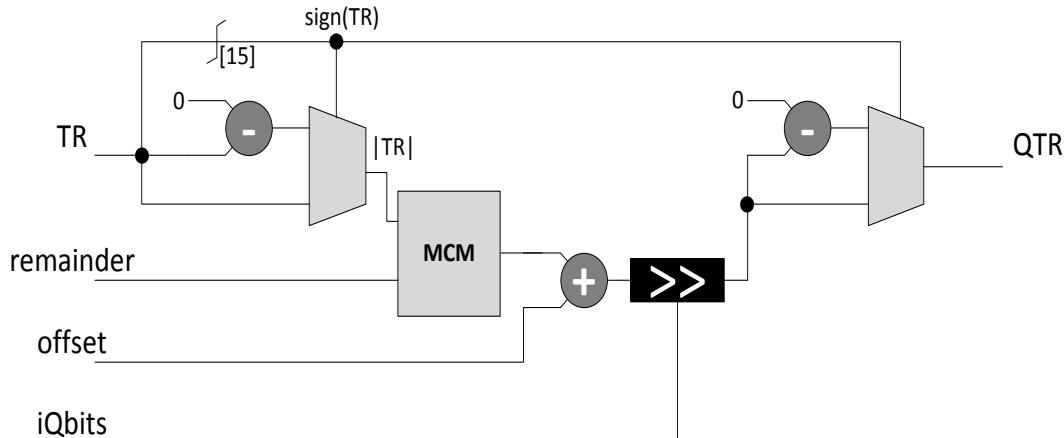

#### 2.1.2.4 Inverse Quantization

The inverse quantization recovers the approximated TR values. It is achieved by multiplying the QTR by QStep, weighted according to the frequency if FDQ is enabled. The integer version of inverse quantization is given by (13) and (14) for the flat-inverse quantization and for the inverse quantization with FDQ support, respectively, where  $W'$  is the recovered transformed residue (RTR),  $Z$  is the quantized transformed residue,  $h(QP\%6) = [40, 45, 51, 57, 64, 72]^T$  is an array complementary to  $G(QP\%6)$ , and  $w(u, v)$  is the frequency-weighting function (11).

$$W' = \left\{ [(Z \times h(QP\%6)) << \left\lfloor \frac{QP}{6} \right\rfloor + [1 \ll (log_2 N - 2)]] \right\} >> (log_2 N - 1) \quad (13)$$

$$W' = \left\{ \left[ (Z \times \frac{h(QP\%6)}{w(u, v)}) << \left\lfloor \frac{QP}{6} \right\rfloor + [1 \ll (log_2 N - 2)] \right\} >> (log_2 N - 1) \quad (14)$$

In conclusion, the HEVC coder requires high computational effort due to the many encoding tools used to minimize the output encoded video file. Among such encoding tools, the RCL is highly required to provide information for the RDO process. Furthermore, HEVC encoding applications in video recording capable devices must encode videos in real-time to avoid storing huge amount of data between the image capture and the video encoding. Thus, HEVC RCL components must be implemented in hardware to achieve the required throughput for real-time video encoding.

## 2.2 Reference Software and Common Test Conditions

The HEVC Test Model Software (HM) is the reference software developed by the specialists of JCT-VC. The HM provides an HEVC standard implementation reference and serves as a basis to validate results from experiments seeking optimizations in the standard (FLYNN et al., 2011). Although the HM can be used as a reference for the generation of a valid HEVC bitstream, it was not developed for real-time encoding.

Along with the reference software, a Common Test Condition (CTC) was also defined (BOSSEN, 2013). The CTC is a collection of test video sequences and standardized configuration profiles which allow a fair, straightforward comparison between solutions using the CTCs. The CTC defined test video sequences (listed in Table 3) present different resolutions and content characteristics that must be considered for experimentations.

Along with the test video sequences, BOSSEN (2013) also defined four QP values

Table 3 – CTC Video Sequences (BOSSEN, 2013)

| Class         | Name                | Resolution | Frame Rate | #Frames | Bitlength |

|---------------|---------------------|------------|------------|---------|-----------|

| A<br>WQXGA    | Traffic             | 2560x1600  | 30         | 150     | 8         |

|               | PeopleOnStreet      | 2560x1600  | 30         | 150     | 8         |

|               | NebutaFestival      | 2560x1600  | 60         | 300     | 10        |

|               | SteamLocomotive     | 2560x1600  | 60         | 300     | 10        |

| B<br>HD 1080p | Kimono              | 1920x1080  | 24         | 240     | 8         |

|               | ParkScene           | 1920x1080  | 24         | 240     | 8         |

|               | Cactus              | 1920x1080  | 24         | 240     | 8         |

|               | BQTerrace           | 1920x1080  | 60         | 600     | 8         |

|               | BasketballDrive     | 1920x1080  | 50         | 500     | 8         |

| C<br>FWVGA    | RaceHorses          | 832x480    | 30         | 300     | 8         |

|               | BQMall              | 832x480    | 60         | 600     | 8         |

|               | PartyScene          | 832x480    | 50         | 500     | 8         |

| D<br>WQVGA    | RaceHorses          | 416x240    | 50         | 500     | 8         |

|               | BQSquare            | 416x240    | 60         | 600     | 8         |

|               | BlowingBubbles      | 416x240    | 50         | 500     | 8         |

|               | BasketballPass      | 416x240    | 50         | 500     | 8         |

| E<br>HD 720p  | FourPeople          | 1280x720   | 60         | 600     | 8         |

|               | Johnny              | 1280x720   | 60         | 600     | 8         |

|               | KristenAndSara      | 1280x720   | 60         | 600     | 8         |

| F             | BasketballDrillText | 832x480    | 50         | 500     | 8         |

|               | ChinaSpeed          | 1024x768   | 30         | 300     | 8         |

|               | SlideEditing        | 1280x760   | 30         | 300     | 8         |

|               | SlideShow           | 1280x760   | 20         | 500     | 8         |

to be used in experimentations: 22, 27, 32, and 37. Moreover, there are four standardized configuration profiles for the HEVC encoder defined in the CTCs (BOSSEN, 2013):

- *All Intra* – The All-Intra configuration profile encodes all frames in the video using only intra-picture prediction. Moreover, frames are encoded in the same order they were recorded/generated. All-Intra configuration profile is the fastest configuration profile since an intra-picture prediction requires lesser computational effort than an inter-pictures prediction. On the other hand, All-Intra configuration profile presents lower compression rate than inter-frames encoding (BOSSEN, 2013).

- *Low Delay* – The Low-Delay configuration profile encodes all frames in the same order they were recorded/generated. In the Low-Delay configuration profile, the first frame is encoded using only intra-picture predictions. All the following frames allow inter-picture biprediction, using up to four reference frames (BOSSEN, 2013). Biprediction is achieved by combining two distinct intermediate inter-

picture predictions (SULLIVAN et al., 2012). The Low-Delay configuration profile has the advantage of high compression. However, it is not recommended for encoded videos to be broadcasted using Low-Delay configuration profile since information losses early in the video will propagate errors in the image up to its end.

- *Low Delay, P-frames only* – It is a variation of the Low-Delay configuration profile. In Low-Delay, P-frames only, configuration profile does not use bi predictions. Therefore, only one inter-frame prediction is made for each block in the frames following the first (BOSSEN, 2013). The Low-Delay, P-frames only, configuration profile present a small reduction in the compression rate, comparing to the Low-Delay configuration profile.

- *Random Access* – The Random-Access configuration profile divides the video into groups of 32 frames, by default. In each group, the first frame is encoded using only intra-picture predictions. The remaining frames in the group can be encoded using inter-pictures bi predictions. The inter-pictures predictions use only frames in the same group as references (BOSSEN, 2013). The Random-Access configuration profile encodes frames out of the order they are recorded/generated. The Random-Access configuration profile is the most appropriate to be used when coding videos for video broadcasting. It can reduce bit-rate, by encoding most of the frames using inter-pictures prediction. On the other hand, the periodic intra-picture frame encoding purges errors in the video caused by missing data in the previous group of frames. Moreover, while using HEVC for digital-TV broadcasting using Random-Access configuration profile, the video decoder must wait until an intra-picture predicted frame is received, and can decode the following video. Using Low-Delay configuration profile, a TV show could be watched only if the TV set is turned on, or the channel is changed, at the exact beginning of the TV show.

## 3 HEVC RESIDUE CODING LOOP (RCL) ANALYSIS

This chapter presents experiments performed using HEVC reference software (HM) to evaluate the RCL throughput required to process all CM evaluated by the HM encoder, while another experiment evaluates the impact on the coding efficiency of RCL components hardware architectures throughput limitations. Moreover, the contribution of the frequency-dependent quantization (FDQ) tool to the HEVC coding efficiency is evaluated. All test video sequences in the CTCs (BOSSEN, 2013) were encoded while performing these experiments, where each video was encoded for QP values of 22, 27, 32, and 37, using All-Intra, Low-Delay, and Random-Access configuration profiles.

### 3.1 Throughput Requirements for the HEVC Residual Coding Loop

The purpose of the throughput requirement for the HEVC RCL experiment is to find how intensively RCL components are used during video encoding. The components in the RCL present symmetries between their direct modules and inverse modules, i.e. the throughput in the DCT component is the same throughput of the IDCT, as the throughput in the direct quantization is the same throughput of the inverse quantization. On the other hand, the throughput in the transform (DCT) can be different from the throughput in the quantization. The difference between the DCT throughput and the quantization throughput is due to the special RCL operational modes, as discussed in Section 2.1.2, or due to the use of the DST instead of the DCT in  $4 \times 4$  TBs.