# UNIVERSIDADE FEDERAL DE PELOTAS Centro de Desenvolvimento Tecnológico

# Programa de Pós-Graduação em Computação

Tese

Heuristic-based Algorithms and Hardware Designs for Fast Intra-picture Prediction in AV1 Video Coding

Marcel Moscarelli Corrêa

# MARCEL MOSCARELLI CORRÊA

Heuristic-based Algorithms and Hardware Designs for Fast Intra-picture Prediction in AV1 Video Coding

Ph.D. Thesis submitted to the Graduate Program in Computing of the Federal University of Pelotas as partial requirement for the degree of Doctor of Philosophy.

Advisor: Luciano Volcan Agostini, Ph.D.

Co-advisors: Guilherme Ribeiro Corrêa, Ph.D.

Daniel Munari Palomino, Ph.D.

# Universidade Federal de Pelotas / Sistema de Bibliotecas Catalogação na Publicação

## C823h Corrêa, Marcel Moscarelli

Heuristic-based algorithms and hardware designs for fast intra-picture prediction in AV1 video coding / Marcel Moscarelli Corrêa; Luciano Volcan Agostini, orientador; Guilherme Ribeiro Corrêa, Daniel Munari Palomino, coorientadores. — Pelotas, 2023.

126 f.: il.

Tese (Doutorado) — Programa de Pós-Graduação em Computação, Centro de Desenvolvimento Tecnológico, Universidade Federal de Pelotas, 2023.

1. Codificação de vídeo. 2. Predição intra. 3. Decisão de modo. 4. AV1. 5. Arquitetura em hardware. I. Agostini, Luciano Volcan, orient. II. Corrêa, Guilherme Ribeiro, coorient. III. Palomino, Daniel Munari, coorient. IV. Título.

CDD: 005

#### Marcel Moscarelli Corrêa

# **Heuristic-based Algorithms and Hardware Designs for** Fast Intra-picture Prediction in AV1 Video Coding

Tese aprovada como requisito parcial para obtenção do grau de Doutor em Ciência da Computação no Programa de Pós-Graduação em Computação da Universidade Federal de Pelotas.

Data da Defesa: 14 de fevereiro de 2023.

#### Banca examinadora:

Prof. Dr. Luciano Volcan Agostini (Orientador)

Doutor em Ciência da Computação pela Universidade Federal do Rio Grande do Sul

Prof. Dr. Guilherme Ribeiro Corrêa (Coorientador)

Doutor em Engenharia Eletrotécnica e de Computadores pela Universidade de Coimbra

Prof. Dr. Daniel Munari Palomino (Coorientador)

Doutor em Ciência da Computação pela Universidade Federal do Rio Grande do Sul

Prof. Dr. Nuno Filipe Valentim Roma

Doutor em Engenharia Eletrotécnica e de Computadores pelo Instituto Superior Técnico

Prof. Dr. Gustavo Freitas Sanchez

Doutor em Ciência da Computação pela Pontifícia Universidade Católica do Rio Grande do Sul

Prof. Dr. Wagner Ishizaka Penny

Doutor em Ciência da Computação pela Universidade Federal de Pelotas

Prof. Dr. Marilton Sanchotene de Aguiar

Doutor em Ciência da Computação pela Universidade Federal do Rio Grande do Sul

Agradeço às instituições públicas de ensino pela educação gratuita e de qualidade que me foi fornecida.

"Sob os ventos da redemocratização, dizíamos:

ditadura nunca mais!

Hoje, depois do terrível desafio que superamos, devemos dizer:

democracia para sempre!"

(Lula)

#### **RESUMO**

CORRÊA, Marcel Moscarelli. Heuristic-based Algorithms and Hardware Designs for Fast Intra-picture Prediction in AV1 Video Coding. 2023. 126f.

Tese (Doutorado em Ciência da Computação) – Programa de Pós-Graduação em Computação. Universidade Federal de Pelotas, Pelotas.

A codificação de vídeo para fins de compressão é indispensável para qualquer aplicação ou serviço baseado na manipulação de vídeos digitais. Sem compressão, conteúdo de vídeo digital moderno requer uma quantidade proibitiva de dados. Um formato de codificação de vídeo define o formato de representação do conteúdo de vídeo em uma forma comprimida, para ser utilizada de maneira conveniente para armazenamento e transmissão. Formatos de vídeo são tipicamente padronizados e têm codificadores e decodificadores de vídeo desenvolvidos para eles, implementados tanto em software quanto em hardware. Esta tese apresenta algoritmos apropriados para implementação em hardware, capazes de reduzir o número de operações associadas à etapa de decisão de modo da predição intraquadros em um codificador de vídeo, que é um dos módulos do codificador que mais consome recursos de processamento. Ainda, esta tese também apresenta arquiteturas em hardware que implementam os algoritmos propostos, otimizadas para baixa potência dissipada e alta eficiência energética. Todas as soluções de software e hardware descritas nesta tese têm como alvo o formato AOMedia Video 1 (AV1), que é o estado da arte em formatos de vídeo abertos e livres de royalties. Todos os algoritmos propostos foram testados no software de referência do codificador AV1, utilizando-se condições comuns de teste deste campo de pesquisa, e todas as arquiteturas de hardware foram descritas em VHDL e sintetizadas para tecnologia TSMC 40nm. Os resultados de eficiência de compressão e tempo de codificação dos algoritmos propostos e, também, os resultados de custo em portas lógicas e consumo de energia das arquiteturas de hardware, confirmam que as soluções desenvolvidas durante este projeto de doutorado atendem as demandas das tecnologias atuais de vídeo, como a codificação de resoluções *Ultra-High Definition* (UHD) em alta velocidade e alta qualidade visual.

Palavras-chave: Codificação de vídeo; predição intra; decisão de modo; AV1; arquitetura em hardware.

#### **ABSTRACT**

CORRÊA, Marcel Moscarelli. Heuristic-based Algorithms and Hardware Designs for Fast Intra-picture Prediction in AV1 Video Coding. 2023. 126f.

Thesis (Ph.D. in Computer Science) – Graduate Program in Computing. Federal University of Pelotas, Pelotas.

Video coding for compression purposes is paramount for any application or service based on digital video. Without compression, modern digital content requires a prohibitively large amount of data. A video coding format defines the format for video content representation in a compressed form, to be used conveniently for storage or transmission. Video formats are, typically, standardized and have video encoders and decoders made for them, in both software and hardware. This thesis presents hardware-friendly algorithms capable of reducing the number of operations of the video encoder mode decision process in the intra-picture prediction module, one of its most time-consuming modules. Additionally, it also presents intra-picture prediction hardware designs, optimized for both low power and high energy efficiency, implementing the proposed algorithms. All software and hardware solutions described in this thesis target the AOMedia Video 1 (AV1) format, which is state-of-the-art in open-source and royalty-free video coding. All algorithms proposed were evaluated in the AV1 reference software using common test conditions, and all hardware designs were described in VHDL and synthesized to TSMC 40nm standard-cells technology. The encoding efficiency and encoding time results for the proposed algorithms, as well as the gate count and energy consumption results for the hardware designs, confirm that solutions developed during this Ph.D. project meet the requirements of current video technology, such as coding of Ultra-High Definition (UHD) resolutions at high speeds and high visual quality.

Keywords: Video coding; intra prediction; mode decision; AV1; hardware design.

# **LIST OF FIGURES**

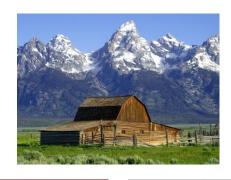

|                          | Example of the RGB (left) and YCbCr (right) channels separated. Picture: on Barn (Public domain)28                                                                                                       |

|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

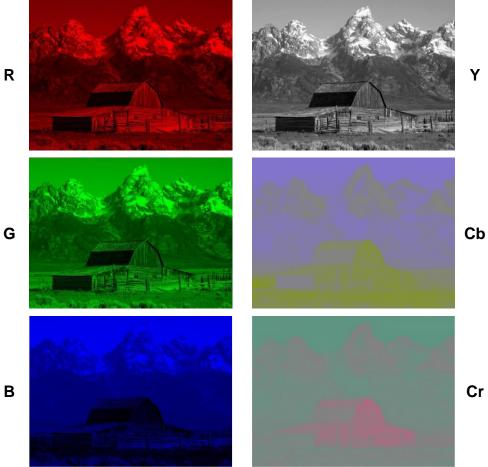

| Figure 2                 | Diagram of a typical hybrid block-based video coder32                                                                                                                                                    |

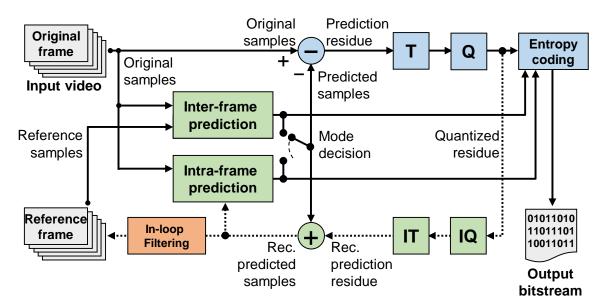

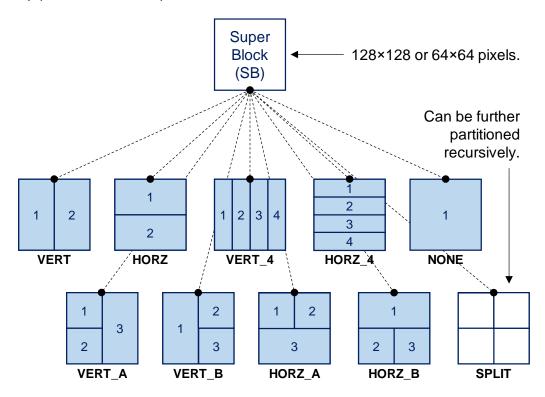

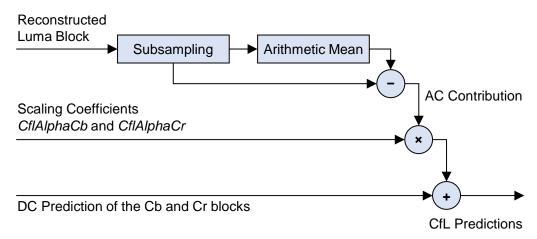

| subpartition             | AV1 10-way block partitioning tree. The numbers inside each final (in blue) indicate the order these will be processed by the following stages a). The name of each partition mode is shown below blocks |

|                          | Example of frame partitioning of the test sequence Crosswalk (Property of and licensed under CC BY-NC-ND 4.0)34                                                                                          |

| Inc.). Middle            | Left: Luminance frame of the test sequence Akiyo (Property of Stadium e: Same frame predicted with 8×8 AV1 intra prediction modes. Right: formation obtained36                                           |

| Figure 6<br>AV1 intra pr | Top: Input image. Bottom: Residual information of the same image after rediction                                                                                                                         |

| Figure 7                 | Block of size 8×4 to be predicted using reference arrays of size 1341                                                                                                                                    |

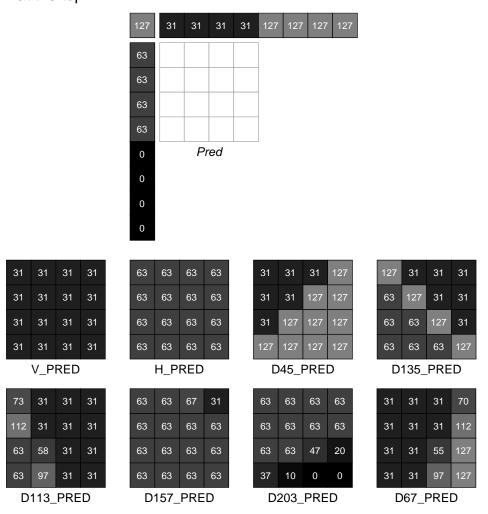

| Figure 8                 | DC algorithm for when all reference samples are available43                                                                                                                                              |

|                          | Example of DC predictions for a block of size 4×4 when (a) all samples e, (b) only left samples are available, (c) only top samples are available, samples are available                                 |

| Figure 10                | Paeth algorithm44                                                                                                                                                                                        |

| Figure 11                | Example of a Paeth prediction45                                                                                                                                                                          |

| Figure 12                | Smooth Vertical algorithm45                                                                                                                                                                              |

| Figure 13                | Smooth Horizontal algorithm45                                                                                                                                                                            |

| Figure 14<br>mode (midd  | Example of predictions using the Smooth mode (left), Smooth Vertical lle), and Smooth Horizontal mode (right)46                                                                                          |

| Figure 15                | RBF algorithm for a single 4×2 patch47                                                                                                                                                                   |

| Figure 16                | Example of the four stages of an RBF prediction of an 8x4 block47                                                                                                                                        |

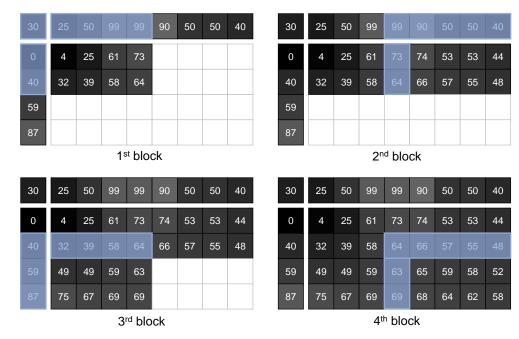

| Figure 17                | Stages of the CFL algorithm49                                                                                                                                                                            |

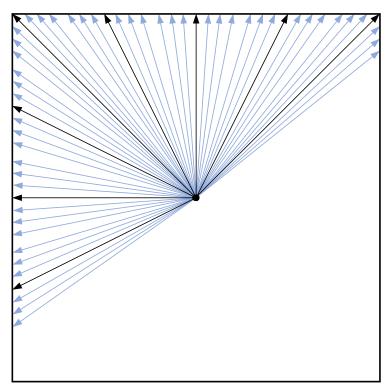

| Figure 18                | Nominal angles (black) and derived angles (blue) supported in AV150                                                                                                                                      |

| Figure 19                | Directional prediction algorithm for any prediction angle51                                                                                                                                              |

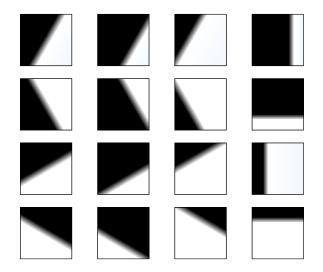

| Figure 20                | Example of predictions using the nominal directional modes53                                                                                                                                             |

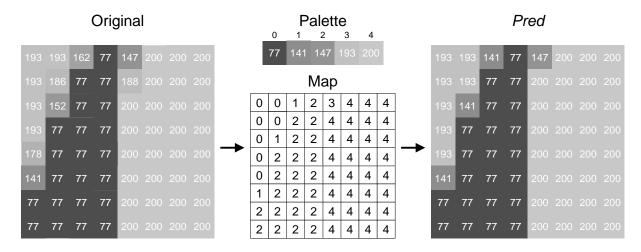

| Figure 21<br>an 8×8 bloc | Example of a prediction using the Color Palette mode for k54                                                                                                                                             |

| Figure 22                | Compound inter-intra prediction wedge masks55                                                                                                                                                            |

| Figure 23                | Compound inter-intra prediction mode-specific masks56                                                                                                                                                    |

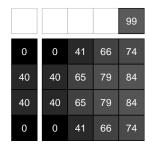

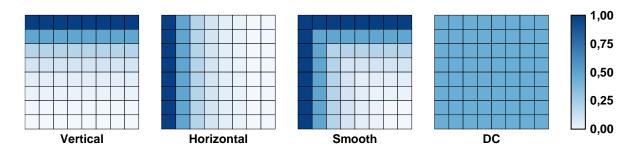

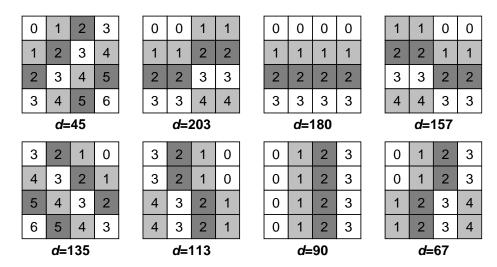

| an AV1 intra               | PDBs adapted to the reduced size of 4x4. Each direction <i>d</i> is named after a mode related to the same angle. The numbers inside each square identify <i>k</i> a sample belongs                                |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

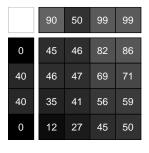

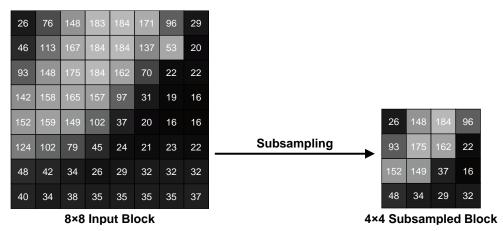

| Figure 25                  | Example of an 8x8 to 4x4 subsampling68                                                                                                                                                                             |

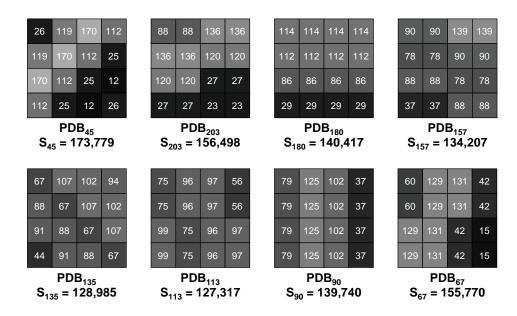

|                            | Example of PDBs and calculation of the dominant direction, based on the of the previous figure69                                                                                                                   |

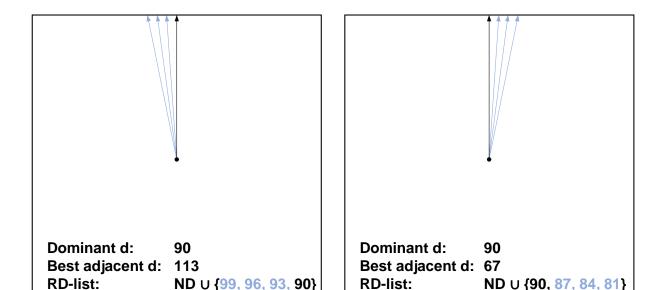

| -                          | Examples of RD-lists created from dominant direction 90, and best ection 113 (left side) and 67 (right side)71                                                                                                     |

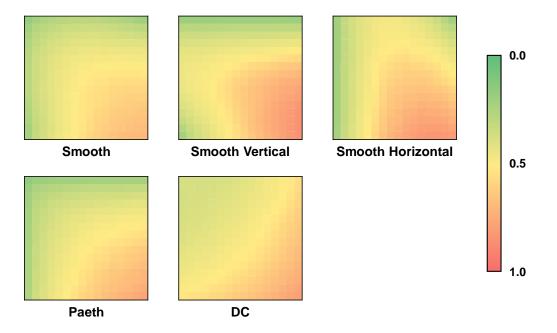

|                            | Heat maps showing the average error of non-directional intra modes when locks of size 16×1673                                                                                                                      |

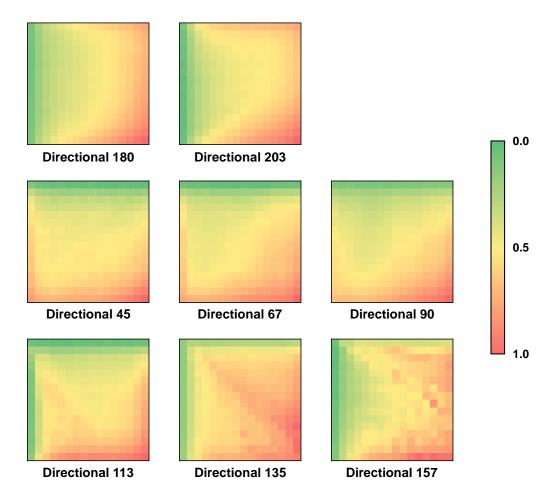

|                            | Heat maps showing the average error of nominal directional intra modes of to blocks of size 16×1673                                                                                                                |

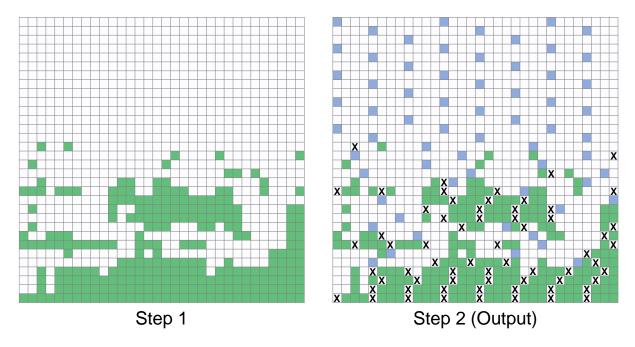

| mask. Right                | Left: 25% of the highest error positions are checked in the subsampling to 25% of the previously checked positions are unchecked uniformly and uniformly in the empty area                                         |

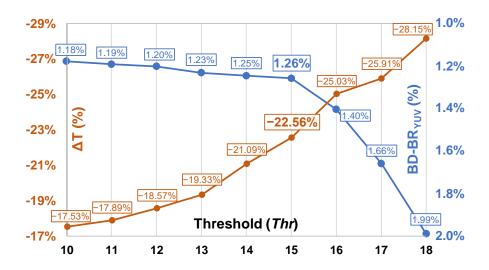

|                            | Encoding efficiency loss and encoding time difference for different alues, with <i>Thr</i> =15 showing the best trade-off77                                                                                        |

| Figure 32                  | Encoding efficiency curves for 15 different parameter combinations78                                                                                                                                               |

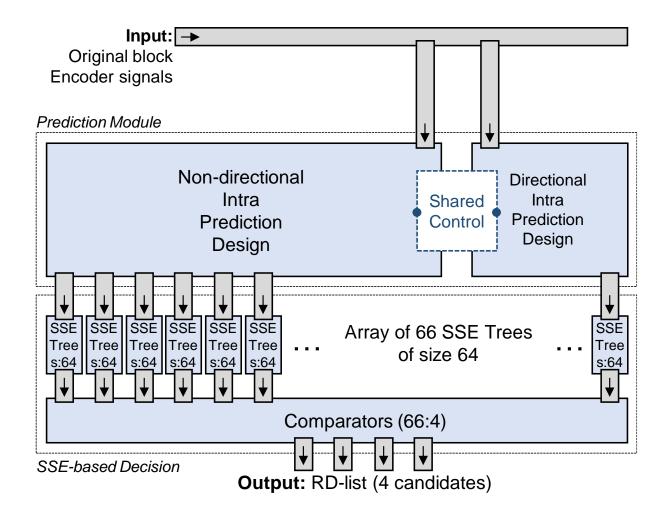

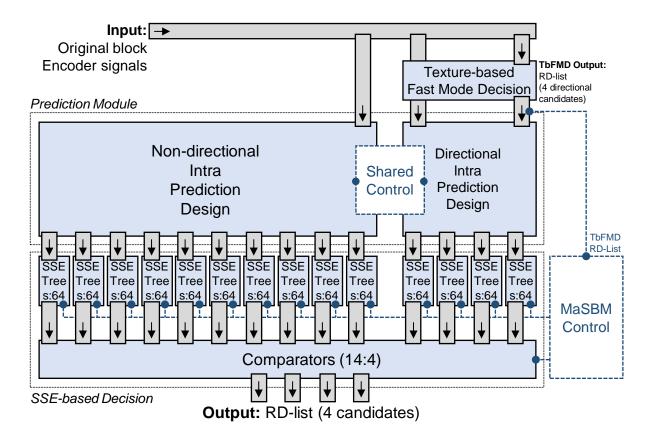

| Figure 33                  | Intra prediction base design82                                                                                                                                                                                     |

| Figure 34                  | Directional intra prediction design83                                                                                                                                                                              |

| Figure 35<br>directional p | Directional sample prediction unit, responsible for generating one predicted sample from a pair of two reference samples                                                                                           |

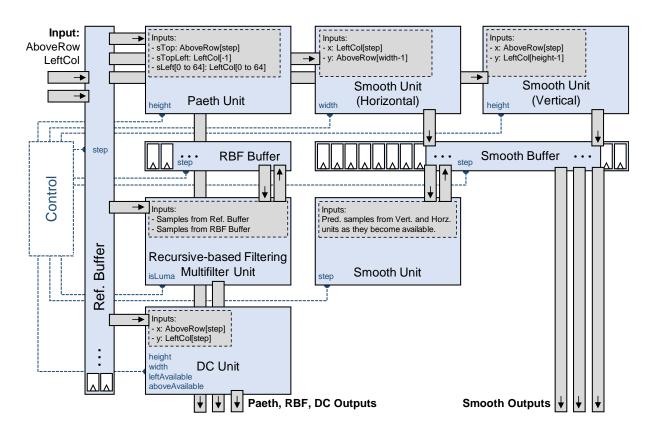

| Figure 36                  | Non-directional intra prediction design88                                                                                                                                                                          |

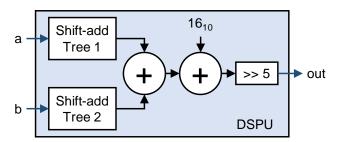

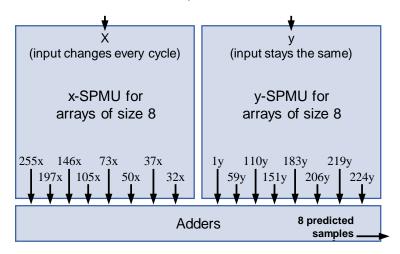

| Figure 37                  | Smooth prediction multiplier unit or size 889                                                                                                                                                                      |

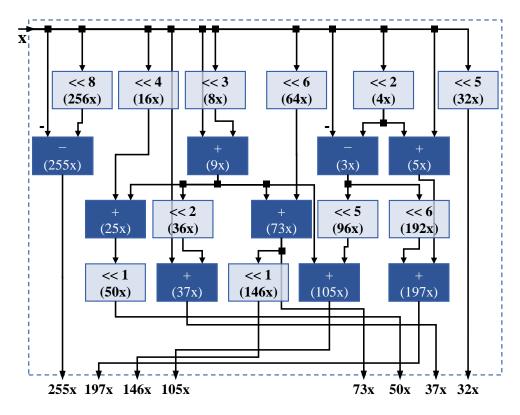

|                            | One of the two shift-add trees used in the SPMU for size 8, highly or subexpression reuse and minimum tree depth90                                                                                                 |

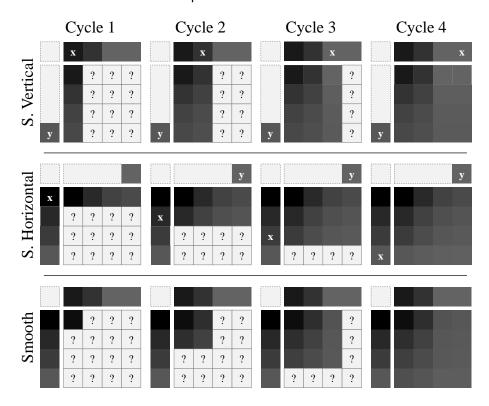

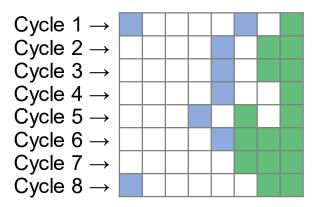

|                            | Prediction order of Smooth Vertical, Smooth Horizontal and Smooth blocks of size 4×4. In asymmetrical blocks, one of the modes will finish thers90                                                                 |

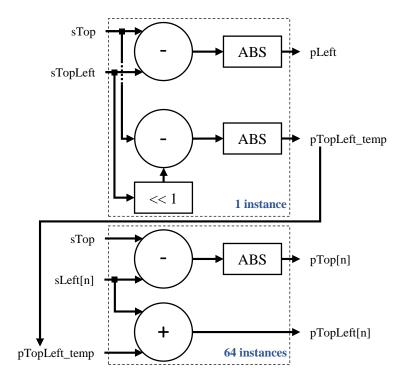

| Figure 40                  | Paeth calculation circuit. Bottom part is replicated 64 times92                                                                                                                                                    |

| Figure 41                  | Paeth comparison circuit. This is replicated 64 times92                                                                                                                                                            |

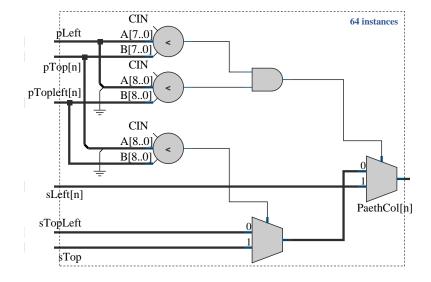

| Figure 42                  | DC Unit93                                                                                                                                                                                                          |

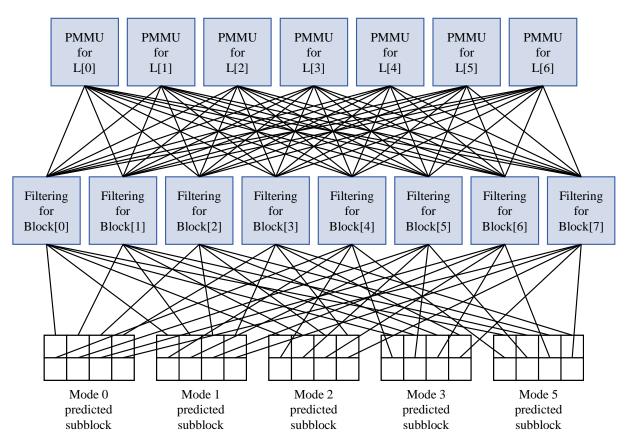

| Figure 43                  | Unified multifilter prediction unit94                                                                                                                                                                              |

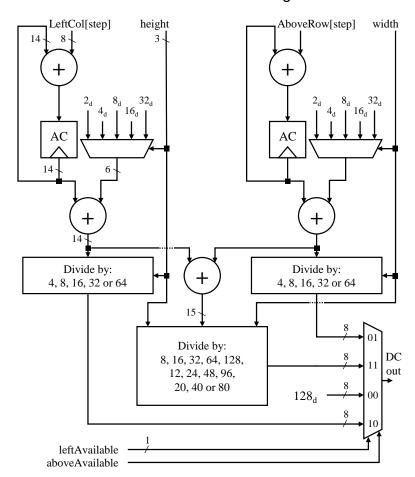

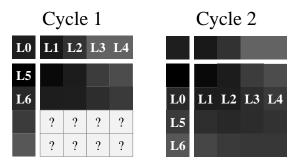

| of size 4×4.               | Prediction order of the Recursive-filtering-based multifilter unit for blocks If the block width is less than 64, two entire rows will be processed per wise, two entire rows will be processed every two cycles95 |

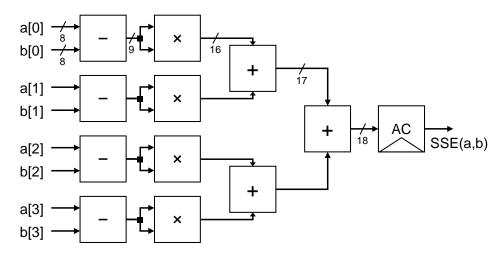

| Figure 45                  | Example of an SSE tree of size 498                                                                                                                                                                                 |

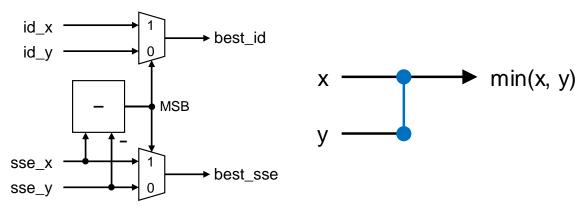

| Figure 46 | Left: 2:1 comparator. Right: Simplified notation for the same circuit9              | 8  |

|-----------|-------------------------------------------------------------------------------------|----|

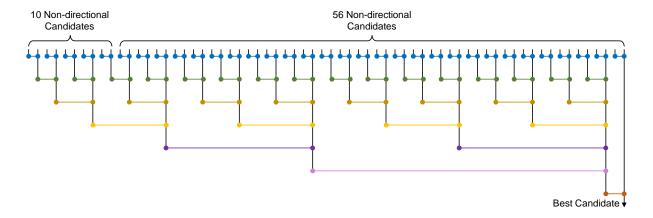

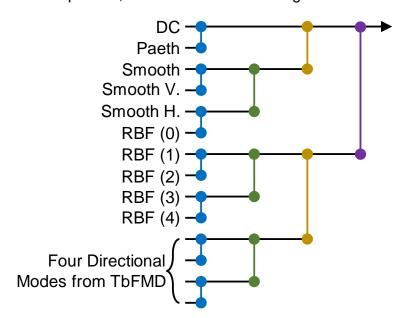

| •         | 66:1 comparator with seven levels of depth. Each color represents a level parators9 |    |

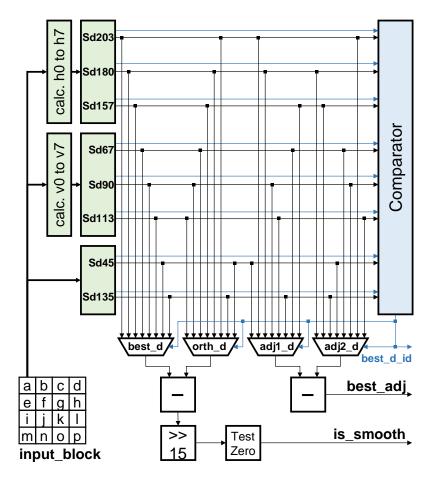

| Figure 48 | Texture-based fast mode decision design10                                           | 0  |

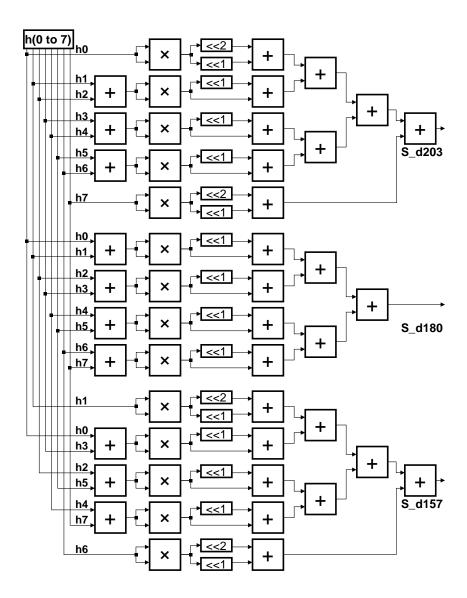

| Figure 49 | Processing unit for d=203, d=180 and d=15710                                        | 1  |

| Figure 50 | 14:1 comparator with four levels of depth10                                         | 2  |

| Figure 51 | Example of 8x8 subsampling mask to be applied to an SSE tree10                      | 3  |

| Figure 52 | Intra prediction hardware design optimized with TdFMD and MaSBM 10                  | )4 |

# **LIST OF TABLES**

| Table 1<br>(CHUANG 6          | Impact of individual intra prediction tools in an AV1 encoder et al., 2022)23                                    |

|-------------------------------|------------------------------------------------------------------------------------------------------------------|

| Table 2                       | Top-left reference sample derivation42                                                                           |

| Table 3                       | Above reference samples derivation42                                                                             |

| Table 4                       | Left reference samples derivation42                                                                              |

| Table 5                       | Contents of the SmoothCoefficients array according to each size46                                                |

| Table 6                       | Filter coefficients stored in the <i>IntraFilterTaps</i> array                                                   |

| Table 7 associated a          | All the directional modes supported by AV1 and their angles50                                                    |

| Table 8<br>directional p      | Possible values for the <i>dx</i> and <i>dy</i> variables in the orediction                                      |

| Table 9                       | Summary of AV1-related algorithmic optimization58                                                                |

| Table 10                      | Summary of AV1-related hardware designs60                                                                        |

| Table 11<br>adjacent dir      | RD-list created for sharp blocks according to the dominant and best ections70                                    |

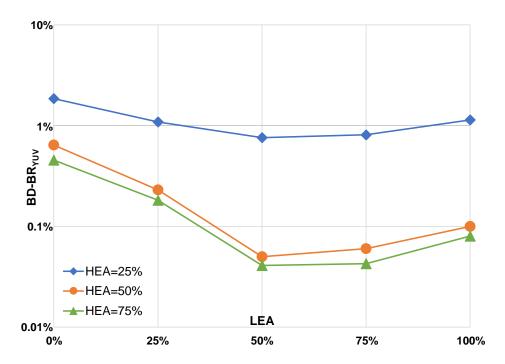

| Table 12<br>and <i>LEA</i> co | Encoding efficiency and encoding time difference results for different HEA mbinations78                          |

| Table 13<br>TbFMD and         | Encoding efficiency and time difference results for the integration of MaSBM per sequence, per class and total80 |

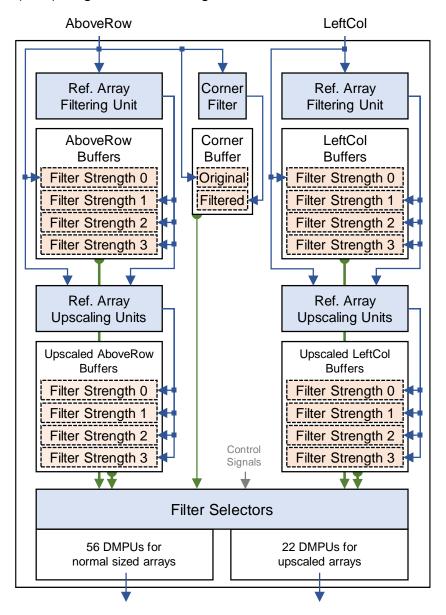

| Table 14                      | Filter selector for <i>AboveRow</i> (only nominal modes are shown)85                                             |

| Table 15                      | Filter selector for <i>LeftCol</i> (only nominal modes are shown)85                                              |

| Table 16<br>multiplicatio     | List of coefficients used by the parallel multiplierless n units95                                               |

| Table 17                      | Finite state machine description of the shared control unit97                                                    |

|                               | Synthesis results for the unoptimized non-directional ion module                                                 |

|                               | Synthesis results for the unoptimized directional intra                                                          |

| Table 20                      | Synthesis results for the unoptimized SSE-based decision module 106                                              |

| Table 21                      | Synthesis results for the unoptimized base design (total)106                                                     |

| Table 22 intra predict        | Synthesis results for the TbFMD-optimized directional ion module                                                 |

|                               | Synthesis results for the TbFMD-optimized SSE-based dule                                                         |

|          | •          |            |         |       |         |         | BM-optimized |         |

|----------|------------|------------|---------|-------|---------|---------|--------------|---------|

| Table 25 | Synthesis  | results fo | r fully | -opti | mized o | design  | (total)      | <br>109 |

|          |            | •          |         |       |         |         | unoptimized  | ,       |

| Table 27 | Test seque | ences use  | ed in t | he e  | xperim  | ents co | nducted      | <br>122 |

#### LIST OF ACRONYMS AND ABBREVIATIONS

1-D One-dimensional

2-D Two-dimensional

3-D Three-dimensional

AC Alternate Current (transform coefficient)

ADST Asymmetrical Discrete Sine Transform

AOMedia Alliance for Open Media

ASIC Application-specific Integrated Circuit

AV1 AOMedia Video 1

AVC Advanced Video Coding (H.264, MPEG-4 Part 10 standard)

BD-BR Bjøntegaard Delta Bit Rate

CABAC Context-adaptive Binary Arithmetic Coding

CAVLC Context-adaptive Variable-length Coding

CDEF Constrained Directional Enhancement Filter

CFL Chroma from Luma

Codec Coder/Decoder

CMYK Cyan, Magenta, Yellow, Key (color model)

CTC Common Test Conditions

dB Decibel

DBF Deblocking Filter

DC Direct Current (transform coefficient)

DCT Discrete Cosine Transform

DFS Depth-first Search

DMPU Directional Mode Prediction Units

DSPU Directional Sample Prediction Units

DSGF Dual Self-Guided Filter

FHD 1080p Full High Definition (1920×1080 pixels)

flipADST Inverted ADST

FSM Finite State Machine

HD High Definition

HD 720p 1280×720 pixels

HEA High Error Area

HEVC High Efficiency Video Coding (H.265, MPEG-H Part 2 standard)

HTTP Hypertext Transfer Protocol

IDTX Identity Transform

IEC International Electrotechnical Commission

IP Internet Protocol

ISO International Organization for Standardization

ITU International Telecommunication Union

ITU-T ITU Telecommunication Standardization Sector

JVET Joint Video Experts Team

KLT Karhunen-Loeve Transform

LEA Low Error Area

LRF Loop Restoration Filter

MaSBM Mode-adaptive Subsampling in Block Matching

ME Motion Estimation

MPEG Moving Picture Experts Group

MPEG-2 Video (H.262, MPEG-2 Part 2 standard)

MSE Mean Squared Error

PDB Perfectly Directional Blocks

PMMU Parallel Multiplierless Multiplication Units

PSNR Peak Signal-to-noise Ratio

RBF Recursive-based-filtering

RD Rate-distortion

RDO Rate-distortion Optimization

RGB Red, Green, Blue (color model)

RTL Register-transfer Level

SD Standard Definition

SAD Sum of Absolute Differences

SCC Screen Content Coding

SPMU Smooth Prediction Multiplication Unit

SSE Sum of Squared Errors

SSNWF Separable Symmetric Normalized Wiener Filter

SVM Support Vector Machine

TbFMD Texture-based Fast Mode Decision

TCP Transfer Control Protocol

TGM Text and Graphics with Motion

TSMC Taiwan Semiconductor Manufacturing Company

UHD Ultra-High Definition

UHD 4K 3840×2160 pixels

UHD 8K 7680×4320 pixels

UMPU Unified Multifilter Prediction Unit

VCEG Video Coding Experts Group

VHDL VHSIC Hardware Description Language

VHSIC Very High Speed Integrated Circuit

VP8 Royalty-free video codec developed by On2 Technologies

VP9 Royalty-free video codec developed by Google Inc.

VP10 Unfinished royalty-free video codec developed by Google Inc.

VVC Versatile Video Coding (H.266, MPEG-I Part 3 standard)

YCbCr Luminance, Blue-difference chrominance and Red-difference

chrominance (color model)

# **CONTENTS**

| LIST C | OF FIGURES                                          | 9  |

|--------|-----------------------------------------------------|----|

| LIST C | OF TABLES                                           | 12 |

| LIST C | OF ACRONYMS AND ABBREVIATIONS                       | 14 |

|        |                                                     |    |

|        | RODUCTION                                           |    |

| 1.1 Re | esearch Hypothesis                                  | 22 |

|        | ain Contributions                                   |    |

| 1.3 Th | nesis Organization                                  | 24 |

| 2 VIDI | EO CODING BACKGROUND                                | 26 |

| 2.1 Re | epresentation of Digital Videos                     | 26 |

| 2.2 Re | edundancies in Digital Videos                       | 28 |

| 2.3 Cd | ompression of Digital Videos                        | 30 |

| 2.4 Di | stortion Metrics                                    | 30 |

| 2.5 Hy | /brid Block-based Video Encoder                     | 32 |

| 2.5.1  | Frame Partitioning                                  | 32 |

| 2.5.2  | Prediction Stage                                    | 34 |

| 2.5.3  | Transform Coding                                    | 36 |

| 2.5.4  | Quantization                                        | 38 |

| 2.5.5  | Entropy Coding                                      | 38 |

| 2.5.6  | In-loop Filtering                                   | 39 |

| 2.5.7  | Mode Decision                                       | 39 |

| 3 AV1  | INTRA-PICTURE PREDICTION                            | 41 |

|        | eference Samples                                    |    |

|        | tra Prediction Modes                                |    |

| 3.2.1  | DC Mode                                             |    |

| 3.2.2  | Paeth Mode                                          |    |

| 3.2.3  | Smooth, Smooth Vertical and Smooth Horizontal Modes |    |

| 3.2.4  | Recursive-based-filtering (RBF) Modes               |    |

| 3.2.5  | Chroma-from-Luma Mode                               |    |

| 3.2.6  | Directional Prediction Modes                        | 50 |

| 3.2.7  | Screen Content Prediction Modes                                   | 54       |

|--------|-------------------------------------------------------------------|----------|

| 3.3 Cc | ompound Inter-intra Prediction                                    | 55       |

|        |                                                                   |          |

|        | ATED WORKS                                                        |          |

|        | /1-related Algorithmic Optimization                               |          |

| 4.2 A\ | /1-related Hardware Designs                                       |          |

| 4.2.1  | Designs for Intra Prediction                                      | 61       |

| 4.2.2  | Designs for Inter Prediction                                      | 62       |

| 4.2.3  | Designs for In-loop Filtering                                     | 63       |

| 4.2.4  | Designs for Entropy Coding                                        | 64       |

| 4.3 Re | esearch Opportunities                                             | 64       |

|        |                                                                   |          |

|        | IRISTIC-BASED ALGORITHMS FOR AV1 INTRA-PICTURE PREDIC             |          |

| 5.1 Al | gorithm 1: Texture-based Fast Mode Decision (TbFMD)               | 66       |

| 5.1.1  | Direction Detection Step                                          |          |

| 5.1.2  | RD-list Creation Step                                             | 69       |

| 5.2 AI | gorithm 2: Mode-adaptive Subsampling in Block Matching (MaSBI     | M)71     |

| 5.2.1  | Observation of SSE Error in Intra Prediction                      | 72       |

| 5.2.2  | Mode-adaptive SSE Subsampling Masks                               | 74       |

| 5.3 Re | esults and Discussion                                             | 76       |

| 5.3.1  | Results for Algorithm 1: Texture-based Fast Mode Decision (TbFMD) | )76      |

| 5.3.2  | Results for Algorithm 2: Mode-adaptive Subsampling in Block N     | Matching |

| (MaSB  | 3M)                                                               | 77       |

| 5.3.3  | Results for Algorithms 1 and 2 Combined                           | 79       |

| 6 HAR  | RDWARE DESIGNS FOR AV1 INTRA-PICTURE PREDICTION                   | 82       |

| 6.1 A\ | /1 Directional Intra Prediction Design                            | 83       |

| 6.1.1  | Reference Sample Filtering Units                                  | 84       |

| 6.1.2  | Reference Sample Upscaling Units                                  | 85       |

| 6.1.3  | Directional Mode Prediction Units                                 | 85       |

| 6.2 No | on-directional Intra Prediction Module                            | 87       |

| 6.2.1  | Smooth Vertical, Smooth Horizontal and Smooth Units               |          |

| 6.2.2  | Paeth Unit                                                        |          |

| 6.2.3  | DC Unit                                                           |          |

| 6.2.4  | Recursive-based-filtering Multifilter Unit                 | 94  |

|--------|------------------------------------------------------------|-----|

| 6.3 Sh | nared Control Unit                                         | 96  |

| 6.4 S  | SE-based Decision Design                                   | 97  |

| 6.5 De | esign Optimization with TdFDM and MaSBM Algorithms         | 99  |

| 6.5.1  | TdFDM Optimization                                         | 99  |

| 6.5.2  | MaSBM Optimization                                         | 102 |

| 6.6 Sy | nthesis Results and Discussion                             | 104 |

| 6.6.1  | Results for the Base Intra Prediction Design               | 105 |

| 6.6.2  | Results for the Optimized Intra Prediction Modules         | 107 |

| 7 CON  | NCLUSIONS                                                  | 110 |

| REFE   | RENCES                                                     | 112 |

| Apper  | ndix A – Experimental Setup                                | 122 |

| Apper  | ndix B – List of Published Papers During the Ph.D. Studies | 124 |

#### 1 INTRODUCTION

Internet-based video traffic has been pushing telecommunication infrastructures to their limit because of the ever-increasing demand for video-based services, such as social media, streaming, video conferencing, and cloud gaming. More recently, in 2019, the world started facing the SARS-CoV-2 pandemic, which led people to heavily depend on video services for their work, educational and social routines more than ever before.

According to Cisco Systems Inc. (2020), from 2017 to 2020, this type of traffic grew 29% annually and was expected to reach 325 exabytes per month by the end of 2022, representing 82% of the global internet traffic. It was also expected that in 2022, of all video traffic, 22.3% would be in Ultra-High Definition (UHD) resolutions, 56.8% in High Definition (HD), and 20.9% in Standard Definition (SD) or lower. Furthermore, by 2023, two-thirds of the installed television sets are expected to be UHD-capable, up from 33% in 2018. This will cause an even bigger impact on the infrastructure because the increase in video definition causes a multiplicative effect on the data volume. For example, a single UHD 4K (3640×2160 pixels) uncompressed frame has four times more data than a Full HD 1080p (FHD) (1920×1080 pixels) frame, and the increase in spatial resolution often comes paired with an increase in temporal resolution (frame refresh rate), which also leads to a linear increase in data.

To address this, standardization bodies such as the Telecommunication Standardization Sector of the International Telecommunication Union (ITU-T) and the International Electrotechnical Commission (IEC) of the International Organization for Standardization (ISO), have been developing video coding standards for decades, with the Versatile Video Coding (H.266/VVC) (ITU-T, 2020; BROSS et al., 2021) being the most efficient video coding standard developed. The H.266/VVC standard was released in July 2020, coming from a long line of successful video coding standards defined by a joint effort of the ISO/IEC MPEG (Moving Picture Experts Group) and the ITU-T VCEG (Video Coding Experts Group) that includes the well-known High Efficiency Video Coding (H.265/HEVC) (ITU-T, 2013; SULLIVAN et al., 2012), Advanced Video Coding (H.264/AVC) (ITU-T, 2003; WIEGAND et al., 2003), and MPEG-2 (ITU-T, 1995).

In recent years, the licensing for commercial use of such standards started to become prohibitively expensive and exceedingly bureaucratic due to a large number of patent holders associated to each standard, affecting even the largest companies, as explained by Rosenberg (2015) on behalf of the Cisco Systems Inc.:

Unfortunately, the patent licensing situation for H.265 has recently taken a turn for the worse. Two distinct patent licensing pools have formed so far, and many license holders are not represented in either. There is just one license pool for H.264. The total costs to license H.265 from these two pools is up to sixteen times more expensive than H.264, per unit. H.264 had an upper bound on yearly licensing costs, whereas H.265 has no such upper limit.

Motivated by this, companies started to look for royalty-free alternatives to the standards. Indeed, the incredible growth of the internet is a consequence of its founding core technologies being open and freely implementable (MUKHERJEE *et al.*, 2013), such as the HyperText Transfer Protocol (HTTP), Transfer Control Protocol (TCP), and Internet Protocol (IP). Nowadays, however, digital video technology became undeniably a central pillar of the internet experience, making free solutions for video coding a subject of great relevance.

A notable example was the start of the WebM project and the acquisition by Google Inc. of the company named On2 Technologies Inc., which originally developed the VP8 (BANKOSKI *et al.*, 2011; BANKOSKI; WILKINS; XU, 2011) coder/decoder (codec), later releasing VP8 freely under the CC BY 3.0 license. The VP9 (GRANGE; RIVAZ; HUNT, 2016; MUKHERJEE *et al.*, 2013) format was later developed by Google Inc., which is still used in various of Google's own video services. In 2015, as Google Inc. was working on a successor for VP9, called VP10, other companies were developing their own royalty-free and open-source video codecs: Cisco Systems Inc. and Mozilla Corporation were involved in the creation of Thor (BJØNTEGAARD *et al.*, 2016) and Daala (VALIN *et al.*, 2016), respectively.

In the end, these three companies, together with eleven more companies, joined efforts and founded the Alliance for Open Media (AOMedia) industry consortium, later releasing the AOMedia Video 1 (AV1) (RIVAZ; HAUGHTON, 2019; HAN *et al.*, 2021) in June 2018, to be the state-of-the-art royalty-free video format. The AV1 is highly based on features from all the unreleased VP10, Thor, and Daala codecs.

Several new coding tools were developed and enhanced in the next-generation codecs (AV1 and H.266/VVC) to deal with the new requirements of video applications and to provide high coding efficiency. These improvements include larger block sizes, flexible block partitioning structures, a higher number of intra prediction modes, the support of affine modes for inter prediction, more transform sizes and types,

improved implementations of quantization and entropy coding, more in-loop filters, and many other novelties.

Even though both the AV1 and H.266/VVC can achieve a satisfactory performance for current video content, this efficiency implicates a very high computational effort. As a consequence, video encoding is an unfeasible task for software solutions when real-time processing and high resolutions are desired, even for high-end devices.

Moreover, in a world where most video-enabled devices are powered by batteries, an efficient combination of hardware-friendly algorithms and Application-specific Integrated Circuit (ASIC) designs is mandatory to produce low-power devices and to allow for faster encoding and decoding speeds in video systems. Although solutions of this type have been proposed for previous codecs, these cannot be used directly in the current codecs without being redesigned to some extent.

## 1.1 Research Hypothesis

The current-generation video codecs, AV1 and H.266/VVC, outperform their predecessors by a significant margin. According to experiments conducted by Nguyen and Marpe (2018), AV1 shows an improvement of 23.4% when compared to VP9, and H.266/VVC shows an improvement of 31.6% when compared to H.264/HEVC, both measured in terms of Bjøntegaard Delta Bit Rate (BD-BR) (see Section 2.4).

Such improvements are due to the increased number of block sizes supported by these codecs, and also due to the increased set of modes supported by different stages of the coder. However, this also led to the growth of the combinatorial space, making the encoder task of selecting the best modes drastically more complex. Separate studies made by Saldanha *et al.* (2020) and Bossen *et al.* (2021) suggest that the H.266/VVC reference software requires up to 27 times more computational effort than the H.265/HEVC reference software, whilst a study made by Nguyen and Marpe (2018) shows that the AV1 reference software requires up to 58 times more run time than the VP9 reference software.

Regarding the intra-picture prediction stage of the AV1, which is the focus of this project, a study made by Chuang *et al.* (2022) evaluated the impact of each of the novel tools added to the AV1 intra-prediction (see Chapter 3) individually, in terms of encoding time difference and image distortion (see Section 2.4). Table 1 shows this impact in a test setup where each tool is enabled one at a time while the others are

disabled. It can be observed that some tools alone can increase the encoding runtime significantly and, when added together, these tools are expected to increase the runtime of the baseline intra prediction stage. Regardless of the encoding time impact, these tools must not be disabled, since it can also be observed in the same table that the reduction in image distortion is also very expressive.

Table 1 Impact of individual intra prediction tools in an AV1 encoder (CHUANG *et al.*, 2022).

| Tool                            | PSNR-Y (%) | Encoding Time (%) |

|---------------------------------|------------|-------------------|

| Intra Angle Delta               | -2.42      | 103.74            |

| Paeth Mode                      | -0.14      | 101.95            |

| Smooth Modes                    | -0.90      | 104.63            |

| Recursive-based-filtering Modes | -0.77      | 109.62            |

| Filtering of Ref. Samples       | -0.36      | 102.47            |

| Chroma from Luma Mode           | -0.36      | 101.04            |

| Intra Block Copy Mode           | -4.81      | 102.75            |

| Palette Mode                    | -6.47      | 100.77            |

The AV1 was chosen as the focus of this work due to its very high commercial relevance, for being both open-source and royalty-free, and also due to its academic relevance, for adding many novel and complex tools never studied before. Furthermore, considering the high relevance of the AV1 intra prediction and the research opportunities related to it, as will be explained in Chapter 4, this stage of the encoder was chosen to be the target of this research project.

Based on these facts, the question this research project sought to answer is:

"Considering the very high computational effort required by the AV1 intra-picture prediction, is it possible to generate novel algorithms and hardware-based solutions able to support the processing of ultra-high-definition videos in real-time?"

Justified by the large number of novel tools introduced to the intra-picture prediction stage, associated with the small number of works in the literature seeking to improve this stage of the encoder, two main research hypotheses were explored in this thesis.

# First hypothesis:

"Information about the direction and smoothness of the input image texture, as well as the error distribution pattern of each prediction mode, can both be used to develop heuristics to reduce the number of AV1 intra-picture prediction modes processed and the number of operations executed in distortion metric calculation for block matching."

Second hypothesis:

"An efficiently designed hardware architecture for the original AV1 algorithms and the proposed heuristic-based algorithms is a promising solution to allow the processing of ultra-high-definition videos in real-time by the AV1 intra prediction."

Then, considering these hypotheses, the main thesis investigated in this work is:

"It is possible to reduce the computational effort of the AV1 intra-picture prediction by developing hardware-friendly heuristic-based algorithms and, then, generating efficient hardware designs able to process ultra-high-definition videos in real-time."

#### 1.2 Main Contributions

The main contribution of this research project is the development of both software and hardware solutions for fast the intra prediction in AV1.

Many works were published with specific contributions as the project developed:

- Development of an AV1 intra-picture prediction hardware designs (CORRÊA et al., 2019a, 2019b, 2020a, 2020b; NETO et al., 2020, 2021a, 2021b, 2022);

- Development of hardware-friendly heuristic-based algorithms capable of reducing the number of operations in intra prediction (CORRÊA et al., 2022a, 2022b);

- Development of intra-picture prediction hardware designs optimized with the proposed algorithms (CORRÊA et al. 2022b).

## 1.3 Thesis Organization

This thesis is organized as follows:

Chapter 2 provides the basic video coding concepts needed for the understanding of the proposed solutions, and also provides information on different parts of an AV1 coder.

Chapter 3 provides an in-depth technical view of the AV1 intra-picture prediction techniques.

Chapter 4 presents a review of the related works that propose system-level solutions for complexity reduction in an AV1 encoder, as well as works that propose

dedicated hardware designs for modules of an AV1 encoder and decoder. It also discusses opportunities in the area of research.

Chapter 5 presents heuristic-based algorithms for the intra prediction stage of the AV1 encoder.

Chapter 6 presents hardware designs for the intra prediction stage of the AV1 encoder.

Chapter 7 presents the conclusions of this thesis, summarizing the major results, identifying possible extensions of the project, and pointing out future research directions in the area.

Appendix A presents the test sequences and coding parameters used for all experiments during this Ph.D. project.

Appendix B lists all the peer-reviewed published papers that were produced during the Ph.D. project.

#### 2 VIDEO CODING BACKGROUND

This chapter presents the basic concepts behind the video coding (compression) process.

## 2.1 Representation of Digital Videos

A video is made of a series of still images that, when displayed at a sufficiently high refresh rate, provides the viewer with the perception of smooth movement. Video sequences vary in spatial resolution, refresh rate, color space, and other characteristics. Contemporary videos tend to be fully digital through the entire process of production, distribution, and playback.

Each still image in a digital video sequence is called a frame, organized as a matrix of pixels. In this context, a pixel is the smallest addressable element in a frame, and it is a combination of different samples of a color space.

A color space is an arbitrary model for representing colors as tuples, e.g., triples in the Red, Green, Blue (RGB) model, and quadruples in the Cyan, Magenta, Yellow, Key (CMYK) model. The RGB color model is typically used in display devices of various technologies, and it is an additive color model in which the red, green, and blue primary colors of light are added to reproduce a broader array of colors. The CMYK model, on the other hand, is a subtractive color model that mixes the subtractive primaries cyan, magenta, and yellow to block light, rather than adding it, which is particularly convenient for color printers.

For video coding, however, the Luminance, Blue-difference Chrominance, and Red-difference Chrominance (YCbCr) model is the most suitable. In this color model, the luminance information, which is closely related to the perception of brightness, is completely separated from chrominance information, allowing encoders to take advantage of the human visual system characteristic of being much more sensitive to luminance than to color information. One practical example of this is the color subsampling technique, which is used to decrease the resolution allocated to the chrominance channels, without significant loss of information being perceived by the human eye. The most common color sampling schemes are called 4:4:4, 4:2:2, 4:2:0, and 4:0:0. In the 4:4:4 sampling, the resolution of the luminance and both chrominance channels are kept intact and no color information is discarded, whereas in the 4:2:2 and 4:2:0 subsampling, the resolution of both chrominance samples is reduced by 50%

and 75%, respectively. Finally, in the 4:0:0 scheme, only luminance information is carried.

Figure 1 shows a picture in full color and the same picture with the three channels of the RGB color model separated (left), and the same for the YCbCr color model (right). It can be observed clearly that each channel of the RGB color model represents the intensity of each of the primary colors, and that there is a part of the luminance information shared among all three channels. Furthermore, it can also be observed that the luminance channel Y of the YCbCr color model has all the luminance information, seen as a grayscale image, whereas both the chrominance channels only have color information, making it impossible to perceive edges and depth information in detail due to the lack of light information.

This way, the representation of digital videos in an uncompressed format demands a prohibitive amount of storage space or network bandwidth. For example, a UHD 4K video, displayed at a refresh rate of 30 fps (frames per second), with 8 bits per channel in the 4:2:0 sampling scheme, which are qualities of videos commonly used in internet streaming and digital television broadcasting nowadays, requires a bandwidth of approximately 3 Gbps (three billion bits per second). A video with these same qualities and 30 minutes of duration requires approximately 672 GB (672 billion bytes) of storage space.

Figure 1 Example of the RGB (left) and YCbCr (right) channels separated. Picture: John Moulton Barn (Public domain).

# 2.2 Redundancies in Digital Videos

Although digital videos demand a very high volume of data to be represented, much of this data can be compressed due to the strong correlation both between successive frames and within the frame content itself (GHANBARI, 2011). The goal of video compression is to eliminate irrelevant and redundant data present in the video representation.

Irrelevant information in the video representation is always of a visual nature and is deemed irrelevant due to the limitations of the human visual system. For example, the human eye is not sensible to high-frequency distortions (CORRÊA, 2014),

i.e., it can effectively perceive subtle variations of luminance over a relatively large area but struggles to perceive such variations in small areas (CORRÊA *et al.*, 2016). Hence, for compression purposes, an encoder can discard information that the human eye is not sensible to.

Redundant information in a digital video can be of a visual nature (spatial and temporal) or statistical nature (entropic). These types of redundancy can be defined as follows (AGOSTINI, 2007):

- Spatial Redundancy: Also called intra-picture redundancy, it is the similarity between pixels spatially close to each other. This redundancy can be explored in the spatial domain by the intra-picture prediction stage of a video coder.

- Temporal Redundancy: Also called inter-picture redundancy, it is the similarity between frames temporally close to each other. Because of the high refresh rate of a video, pixels tend to not change from one frame to another, and changes are likely to be small variations in pixel intensity (e.g., change in lighting) and position (e.g., the motion of an object or the entire background). This redundancy can be explored by the inter-picture prediction stage of a video coder.

- Entropic Redundancy: In information theory, entropy is related to the occurrence frequency of symbols. In a scenario where all symbols have the same probability of occurring, the same number of bits must be used to represent these symbols. On the other hand, if some symbols have a higher probability of occurring, then this redundancy can be explored by assigning variable length codes to these symbols (i.e., codes with fewer bits assigned to more frequent symbols). The entropic redundancy is explored by the entropy coding stage of a video coder.

## 2.3 Compression of Digital Videos

Irrelevant and redundant information can be explored by using lossless and lossy compression. The intra-picture prediction, inter-picture prediction, and entropy coding all aim at reducing redundancy without causing any loss of information. Compression techniques that do not cause loss of information are classified as lossless compression techniques (i.e., the decompressed data is identical to the original). On the other hand, compression techniques that aim at discarding information that is not relevant or is less relevant to the human visual system are classified as lossy compression techniques (i.e., the image can be reconstructed with a visual fidelity relative to the compression parameters, but never identical to the original).

Video compression can be lossless throughout the entire process, which can be particularly useful for applications that cannot tolerate any loss of sensitive information and the addition of compression artifacts. However, for the majority of consumer applications, lossy techniques are used, as these are capable of adding substantial gains to the resulting compression rate.

#### 2.4 Distortion Metrics

Lossy video compression causes distortion, and this distortion must be measured. Visual quality, however, is inherently subjective and, therefore, it is difficult to obtain a completely accurate measurement of it. There are standardized methodologies for the assessment of subjective image quality including, general testing methods, the grading scales used during assessments, and the viewing conditions recommended for carrying out assessments, which are well described in Recommendation ITU-R BT.500-14 (ITU-T, 2019). Quality can also be measured objectively with metrics that compare pixels of the original and the reconstructed image.

The most commonly used objective distortion metric is the Peak Signal-to-noise Ratio (PSNR). The PSNR, measured in decibels (dB), of a test image T of size  $M \times N$ , when compared to the original image O, is described in eq. (1), where the dividend MAX is the maximum value possible for an unsigned sample (e.g., 255 for an 8-bit sample) and the divisor is the Mean Squared Error (MSE) function, described in eq. (2), which is also a distortion metric by itself.

$$PSNR(O,T)_{dB} = 10\log_{10}\left(\frac{MAX}{MSE(O,T)}\right)$$

(1)

$$MSE(O,T) = \frac{1}{MN} \sum_{i=0}^{M-1} \sum_{j=0}^{N-1} (T_{i,j} - O_{i,j})^2$$

(2)

To measure the distortion in smaller regions of an image, like when comparing a predicted block against the original in inter- and intra-picture prediction (known as block matching), simpler metrics are used, such as the MSE, the Sum of Absolute Differences (SAD) and the Sum of Squared Errors (SSE), respectively described in eqs. (2), (3), and (4).

$$SAD(O,T) = \sum_{i=0}^{M-1} \sum_{j=0}^{N-1} |T_{i,j} - O_{i,j}|$$

(3)

$$SSE(O,T) = \sum_{i=0}^{M-1} \sum_{j=0}^{N-1} (T_{i,j} - O_{i,j})^2$$

(4)

Another metric for perceptual visual quality is the Video Multi-method Assessment Fusion (VMAF) (NETFLIX INC, 2022a; LIU *et al.*, 2013; LIN *et al.*, 2014), which attempts to predict subjective quality by combining multiple objective quality metrics. According to Netflix Inc. (2022b), the basic rationale is that each elementary metric may have its strengths and weaknesses, and by fusing elementary metrics into a final metric using a machine-learning algorithm, in this case, the Support Vector Machine (SVM) regressor, the final metric could preserve the strengths of the individual metrics, and deliver a more accurate final score.

However, the measurement of compression efficiency should not rely on distortion alone, but also on the resulting bit rate, that is, a Rate-distortion (RD) metric. A notable example of such a method is the Bjøntegaard Model (BJØNTEGAARD, 2011). In this model, PSNR is the metric of choice for distortion, because of its simplicity, and also because it reasonably matches subjective opinion scores.

In the scope of this thesis, the metric used to evaluate the proposed algorithms is the Bjøntegaard Delta Bit Rate (BD-BR), which reports the average bit rate difference in percent for two videos (e.g.: original versus compressed) considering the same PSNR.

## 2.5 Hybrid Block-based Video Encoder

Most of the contemporary encoders are based on the following signal and data processing operations: (i) inter- and intra-frame prediction, (ii) de-correlating transform (T module), (iii) quantization (Q module), and (iv) entropy coding, as shown in Figure 2. A reconstruction loop (complete decoder) with inverse quantization (IQ module) and inverse transform (IT module) is also included because the coder must use only reference frames available to the decoders, so decoders can replicate identical predictions (SALDANHA, 2021). Additionally, an optional in-loop filtering module (not shown in Figure 2) can also be included to improve the subjective image quality of reconstructed frames. Hybrid block-based encoders apply the abovementioned operations after partitioning frames into smaller blocks and use both motion- and still-picture coding techniques (SULLIVAN; WIEGAND, 1998).

Figure 2 Diagram of a typical hybrid block-based video coder.

The following subsections describe the different stages of video compression shown in Figure 2, while briefly explaining the AV1 implementation of these stages.

#### 2.5.1 Frame Partitioning

Before any signal processing operation can happen, in block-based video coding, a frame must be divided into several blocks of pixels of the maximum size supported by the codec. These blocks can then be further subdivided into smaller blocks during the prediction process. Each video codec defines a variable range of block sizes it can use.

In AV1, a frame is initially partitioned in Superblocks (SBs), which is the biggest block size supported (128×128 or 64×64 pixels). To deliver an optimal prediction for each SB, the encoder can further divide each SB using a 10-way partition tree structure, as illustrated in Figure 3. In the figure, partitions filled in blue are final, but all four subpartitions of the unfilled partition (SPLIT) can be recursively divided based on the same 10-way tree structure, down to 4×4 pixels, which is the smallest supported block size (RIVAZ; HAUGHTON, 2019). This way, the 24 block sizes supported in AV1, including symmetrical and rectangular sizes, are the ones contained in the following set: {4×4, 8×8, 16×16, 32×32, 64×64, 128×128, 4×8, 8×4, 8×16, 16×8, 16×32, 32×16, 32×64, 64×32, 64×128, 128×64, 4×16, 16×4, 8×32, 32×8, 16×64, 64×16, 32×128 e 128×32} (HAN et al., 2021).

Figure 3 AV1 10-way block partitioning tree. The numbers inside each final subpartition (in blue) indicate the order these will be processed by the following stages (raster scan). The name of each partition mode is shown below blocks.

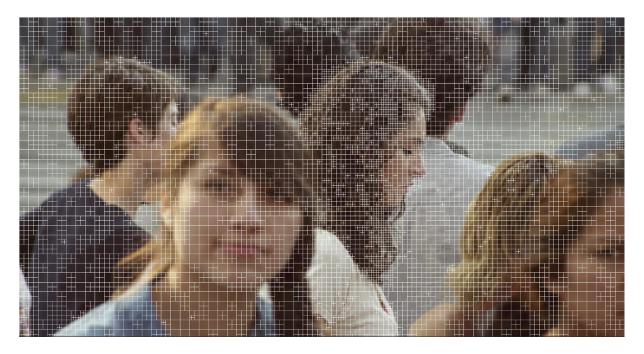

Figure 4 shows an example of frame partitioning (BEBENITA, 2017), generated using the AOM Analyzer tool (XIPH.ORG FOUNDATION, 2022). In the figure, it can be observed that the variable block size structure gives the coder freedom to explore less detailed portions of the image with large block sizes (reducing the overhead of signaling multiple smaller blocks), and more detailed portions of the image with small block sizes (prioritizing visual quality).

Figure 4 Example of frame partitioning of the test sequence Crosswalk (Property of Netflix Inc. and licensed under CC BY-NC-ND 4.0).

## 2.5.2 Prediction Stage

In inter-picture prediction, or simply inter prediction, the translational motion of areas of the frame can be estimated by searching for similar blocks in a reference frame around its original position, and by taking the difference of the best match, in what is called the Motion Estimation (ME) algorithm of a motion-compensated prediction. The ME reduces the temporal redundancy of a frame, and results in blocks of residual information (error) and Motion Vectors (MV) that are used to describe the displacement of predicted blocks. For static parts of the scene, residual differences can be zero, with no error to be coded, whereas for parts of the scene with motion, a significant error can exist, which needs to be coded.

The AV1 motion-compensated prediction supports all 24 block sizes and may use up to seven reference frames, with four being frames that precede the current frame in terms of display order, and three coming after. AV1 brings a variety of novel solutions when compared to older codecs, such as: (i) Affine Motion Compensation, which uses affine transformations to capture non-translational object movements (e.g., rotation, translation, and scaling); (ii) Compound Prediction, which linearly combines two predictions from different reference frames in a single one; and others.

In intra-picture prediction, or simply intra prediction, spatial redundancy can be explored in the spatial domain by predicting entire blocks using reconstructed samples

of previously encoded spatial neighbor blocks from the same frame. This type of prediction usually applies filters to the reference samples to generate different kinds of directional and smooth textures. Just like in the inter prediction, the objective is to obtain a predicted block that results in the lowest residual information when compared to the original block.

AV1 intra prediction supports the 19 block sizes that are equal to or smaller than 64x64 samples. For all mentioned block sizes, the codec supports 56 directional prediction algorithms (modes) to explore spatial redundancies in directional textures (e.g., samples belonging to the same edge of an object tend to be similar), and also supports various non-directional prediction modes, such as: (i) DC, similar to the mode used in many older codecs; (ii) Smooth, Smooth Vertical, and Smooth Horizontal, inspired in the H.265/HEVC Planar mode and H.264/AVC Plane mode; (iii) Paeth, evolved from the VP9 True Motion mode; (iv) five different Recursive-based-filtering (RBF) modes, which attempt to break data dependency by further dividing the intra block into smaller 4x2 patches; and (v) Chroma from Luma (CFL) mode, which predicts chrominance samples based on the information of the luminance prediction (TRUDEAU; EGGE; BARR, 2018). Two modes particularly efficient for Screen Content Coding (SCC) are also available: the Intra Block Copy (LI *et al.*, 2018) and Color Palette (GUO *et al.*, 2014) modes. Chapter 3 gives an in-depth view of the AV1 intra prediction module, as it is the focus of this work.

As mentioned above, the goal of both inter and intra predictions is to minimize the residual information, which can be coded much more effectively than the original visual data. Figure 5 shows an original luminance of the Akiyo test sequence (left), an example of AV1 intra prediction, restricted to the 8×8 block size to give a better visualization of block boundaries (middle); and the resulting residual information (prediction error) that must be coded (right). The figure demonstrates the low-energy nature of the residual information that can be obtained when the predictions are done effectively, where white and black areas are of high-energy (negative and positive differences), and gray areas are closer to zero energy.

Figure 5 Left: Luminance frame of the test sequence Akiyo (Property of Stadium Inc.). Middle: Same frame predicted with 8×8 AV1 intra prediction modes. Right: Residual information obtained.

Finally, it is important to mention that by using the side information that tells how a block was coded (i.e., intra mode, reference frame, motion vector, etc), a decoder can always replicate the same prediction done by the coder, and by adding it to the residual block, the reconstructed block is obtained.

## 2.5.3 Transform Coding

The transform coding is another stage that allows the removal of spatial redundancies in images, but in the frequency domain, as natural images tend to concentrate most of their energy in low-frequency coefficients (GHANBARI, 2011). The transform itself, however, does not result in compression, because the signal energy in the pixel domain is equal to the energy in the frequency domain. Although, in the frequency domain, coefficients with irrelevant magnitude can be quantized (resulting in zero) and high-frequency coefficients can be quantized to a higher degree for not being very important to the human visual system. For this reason, a transform kernel must also be efficient in separating components with minimal inter-dependence (decorrelation) (RICHARDSON, 2010).

The Two-dimensional (2-D) Discrete Cosine Transform II (DCT-II), as defined in eq. (5), is a widely used transform in image and video compression. When applied to an image matrix X of size  $N \times M$ , it results in a matrix Y of coefficients of the same size, where  $Y_{0,0}$  is the zero-frequency coefficient called DC, whereas the remaining coefficients are called AC coefficients.

$$Y_{x,y} = \sum_{i}^{N-1} \sum_{j=1}^{M-1} X_{i,j} \cos\left[\frac{\pi}{N} \left(i + \frac{1}{2}\right) x\right] \cos\left[\frac{\pi}{M} \left(j + \frac{1}{2}\right) y\right]$$

(5)

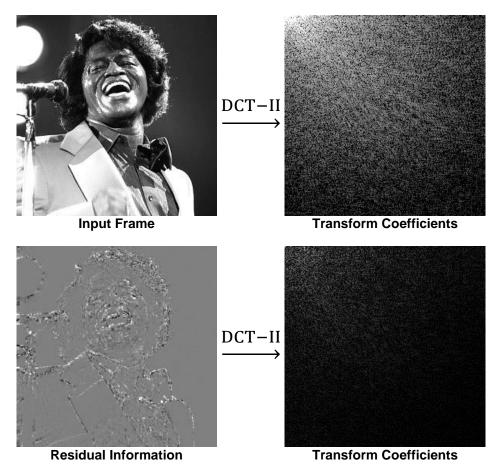

Figure 6 Top: Input image. Bottom: Residual information of the same image after AV1 intra prediction.

Figure 6 illustrates the advantage of applying the DCT-II to the low-energy residual information. At the top, an input image of artist James Brown of 256×256 pixels in size is shown, whereas, in the bottom, the residual information resulting from applying AV1 intra prediction to the same frame is shown. Two things can be observed: (i) the residual information can be represented with much smaller transform coefficients, and (ii) most big coefficients (bright area) are concentrated in the top-left (shown in logarithmic scale for better visualization).

AV1 defines transform kernels for the 19 symmetrical and rectangular sizes equal to or smaller than 64×64. A rich set of 2-D transform kernels is defined for both inter and intra predicted blocks consisting of 16 combinations of one-dimensional (1-D) vertical and horizontal DCT, Asymmetrical Discrete Sine Transform (ADST), flipped ADST, and Identity Transform (IDTX) (HAN *et al.*, 2021). The DCT is used for being a good low-complexity approximation of the optimal Karhunen-Loeve Transform (KLT). For the intra predicted blocks, which tend to concentrate higher residual energy on the bottom and/or right corners, the asymmetrical transforms ADST and flipped ADST are particularly effective (PARKER et al., 2016). The IDTX, when combined with

the other 1-D transforms, provides 1-D transforms that can be useful for dominant horizontal and vertical patterns in texture (HAN *et al.*, 2021). Furthermore, a 2-D IDTX is equivalent to a transform skip, and it can be effective for certain patterns found in SCC (PARKER et al., 2016).

#### 2.5.4 Quantization

Quantization is the process of mapping a signal with a range of values to a quantized signal with a reduced range of values and, therefore, is a lossy process. Examples of the quantizer and inverse quantizer functions for image compression are described in eq. (6) and eq. (7), where step is directly associated with a Quantization Parameter (QP). It can be observed that the lossy aspect of the quantizer function Q(Y) is a consequence of the fractional part of the division being discarded, thus the inverse quantizer function IQ(Y) is not capable of recovering the original pre-quantized value. The QP plays an important role in the RD control of a video coder, as higher QPs will result in a smaller, and hence more compressible range of transform coefficients, whereas smaller QPs will result in a higher range of coefficients that best match the pre-quantized values.

$$Q(Y) = \left| \frac{Y}{step} \right| \tag{6}$$

$$IQ(Y) = Y \times step \tag{7}$$

The QPs in AV1 range between 0 and 255, and each QP has associated with it two different *step* values, a smaller one to be applied exclusively to the DC coefficient, and a larger one to be applied to the AC coefficients (RIVAZ; HAUGHTON, 2019). Additionally, AV1 supports 15 sets of quantization weighting matrices that can further scale the quantization step differently for each frequency coefficient (HAN *et al.*, 2021), allowing for a better exploration of the human visual system.

# 2.5.5 Entropy Coding

The entropy coding processes matrices of quantized coefficients, which can be reordered to group the coefficients from the region with multiple zeros, and lateral data, such as motion vectors, prediction modes, and a variety of bitstream headers, to reduce their statistical redundancy. Variable-length coding (such as Huffman coding) and arithmetic coding are the common methods of entropy coding

used in video compression. Since efficient entropy coding depends on accurate symbol probability models (RICHARDSON, 2010), video standards further improved these algorithms to be context-based, using local spatial and/or temporal characteristics of the signal to estimate the probability of symbols being encoded. Notable examples of entropy coding algorithms are Context-adaptive Variable-length Coding (CAVLC) and Context-adaptive Binary Arithmetic Coding (CABAC), the latter being significantly more efficient at cost of requiring more processing power from both the encoder and decoder.

AV1 uses a context-adaptive multi-symbol arithmetic coder, with integer symbols ranging from 2 to 14, and the probability model is updated per symbol coding. Specifically, for transform coefficient coding, AV1 allows the coefficient matrix to be reordered (mapped to a 1-D array) in the following scan orders: (i) column scan for 1-D vertical transforms, (ii) row scan for 1-D horizontal transforms, and (iii) zig-zag scan starting at the DC coefficient and moving towards the opposite corner for 2-D transforms, including the 2-D IDTX (HAN *et al.*, 2021).

# 2.5.6 In-loop Filtering

The encoding process inevitably adds artifacts in the compressed videos, mainly because of the block partitioning and the quantization. Typical coding artifacts are blocking, ringing, and blurring. These artifacts decrease the video subjective quality and compromise the quality of prediction references. Thus, all modern codecs allow the use of in-loop filtering to reduce these artifacts.

AV1 supports three optional in-loop filters: the Deblocking Filter (DBF), the Constrained Directional Enhancement Filter (CDEF) (MIDTSKOGEN; VALIN, 2018), and the Loop Restoration Filter (LRF) (MUKHERJEE *et al.*, 2017). The improved filtered frames are used as reference frames for the prediction of subsequent frames.

#### 2.5.7 Mode Decision

The RD efficiency of the compression is based on a complex interaction between various possibilities of coding parameters, like block sizes, prediction modes, transform types, quantization parameters, and others. Therefore, one of the biggest challenges in video compression is the control of an encoder.

The control of the encoder, or its mode decision, uses the Rate-distortion Optimization (RDO) technique for taking decisions of "What part of the image should be encoded using what tool?" by minimizing the distortion D, where the number of bits needed R is subject to a bit rate constraint  $R_i$ , as defined in eq. (8). The optimization task can be solved using Lagrangian optimization, where D is weighted against R, and the Lagrangian rate-distortion J is minimized for a particular value of the Lagrange multiplier  $\lambda$ , as read in eq. (9). Each solution to eq. (9) for a given value of the Lagrange multiplier  $\lambda$  corresponds to an optimal solution to eq. (8) (SULLIVAN; WIEGAND, 1998).

$$\min\{D\}$$

, where  $R < R_i$  (8)

$$\min\{J\}$$

, where  $J = D + \lambda R$  (9)

As there are no simple models for estimating the RD cost *J* that will result from a given combination of coding parameters for a block, the RDO technique in a video encoder must pass the block through all the coding loop to obtain the real RD cost for that combination of parameters (CORRÊA *et al.*, 2016). The RDO is optimal for mode decision, but the number of possible coding parameter combinations is so large that testing all possibilities is an unfeasible task. In practical applications, different modules of the encoder often implement suboptimal local mode decisions, known as fast mode decision algorithms, to reduce the set of parameters sent to the RDO for the more expensive evaluation.

#### 3 AV1 INTRA-PICTURE PREDICTION

This section gives an in-depth view of the AV1 intra prediction, which is the focus of the optimizations proposed in this thesis.

The AV1 intra prediction process is invoked for intra blocks to predict a part of the block corresponding to a transform block. When the transform size used is smaller than the intra block itself, this process is invoked multiple times within the intra block, in raster order, using the same intra mode (RIVAZ; HAUGHTON, 2018).

# 3.1 Reference Samples

To predict a block, the intra prediction modes use reference samples from previously reconstructed blocks located to the left and above the current block. The number of reference samples needed from each side is the sum of the width and height of the block to be predicted, plus one sample.

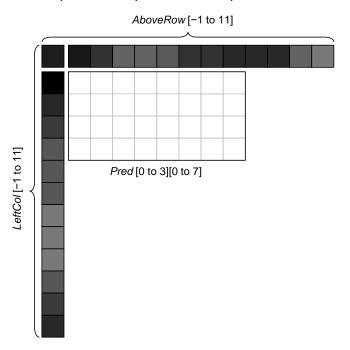

Figure 7 Block of size 8x4 to be predicted using reference arrays of size 13.

Figure 7 illustrates this concept for a block of size 8x4 (white squares). From this point forward, reconstructed samples in the current frame will be referred to as a 2-D array called *CurrFrame*, the current block to be predicted will be referred to as a 2-D array called *Pred*, and the reference samples above and to the left of *Pred* will be referred as two 1-D arrays of samples called *AboveRow* and *LeftCol*, respectively. Additionally, the width and height of *Pred* will be referred to as *W* and *H*.

Since the reference samples must come from already reconstructed transform blocks, some of these may not be available and must be somehow replaced. This happens, for example, when the coder has to predict a block located at the left edge of the frame, which does not have any reference sample to its left. At the beginning of the prediction process, for a given block, both *AboveRow*[-1] and *LeftCol*[-1] are set according to Table 2, while the remaining positions of *AboveRow* and *LeftCol* are set according to Table 3 and Table 4, respectively. In these tables, variables *X* and *Y* point to the top-left position of *Pred* within *CurrFrame*.

Table 2 Top-left reference sample derivation

| Above Available? | Left<br>Available? | Procedure for AboveRow[-1] and LeftCol[-1]                                                          |

|------------------|--------------------|-----------------------------------------------------------------------------------------------------|

| True             | True               | AboveRow[-1] and LeftCol[-1] are set to CurrFrame[Y-1][X-1].                                        |

| True             | False              | AboveRow[-1] and LeftCol[-1] are set to CurrFrame[Y-1][X].                                          |

| False            | True               | AboveRow[-1] and LeftCol[-1] are set to CurrFrame[Y][X-1].                                          |

| False            | False              | AboveRow[-1] and LeftCol[-1] are set to 128, 512 or 2048, depending on the bit depth (8, 10 or 12). |

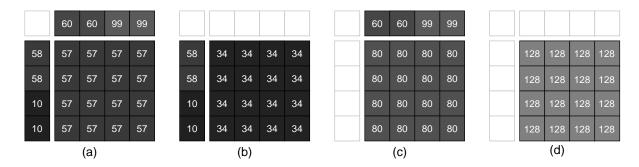

Table 3 Above reference samples derivation

| Above<br>Available? | Left<br>Available? | Above<br>Right<br>Available? | Procedure for AboveRow[pos] for pos = 0w+h−1                                                                                          |

|---------------------|--------------------|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|

| True                | True               | True                         | If pos<2*W, then AboveRow[pos] is set to CurrFrame[Y-1][X+pos].  Otherwise, AboveRow[pos] is set to CurrFrame[Y-1][X+2*W-1].          |

| True                | True               | False                        | If pos <w, aboverow[pos]="" currframe[y-1][x+pos].="" currframe[y-1][x+w-1].<="" is="" otherwise,="" set="" td="" then="" to=""></w,> |

| False               | True               | -                            | AboveRow[pos] is set to CurrFrame[Y][X-1].                                                                                            |

| False               | False              | -                            | AboveRow[pos] is set to 127, 511 or 2047, depending on the bit depth (8, 10 or 12).                                                   |

Table 4 Left reference samples derivation

| Above Available? | Left<br>Available? | Below Left Available? | Procedure for LeftCol[pos] for pos = 0w+h−1                                                                                                |

|------------------|--------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

| True             | True               | True                  | If $pos<2^*H$ , then $LeftCol[pos]$ is set to $CurrFrame[Y+pos][X-pos]$ . Otherwise, $LeftCol[pos]$ is set to $CurrFrame[Y+2^*H-1][X-1]$ . |

| True             | True               | False                 | If pos <h, currframe[y+h-1][x-1].<="" currframe[y+pos][x-1].="" is="" leftcol[pos]="" otherwise,="" set="" td="" then="" to=""></h,>       |